**********************************提前需要知道的基础知识******************************************

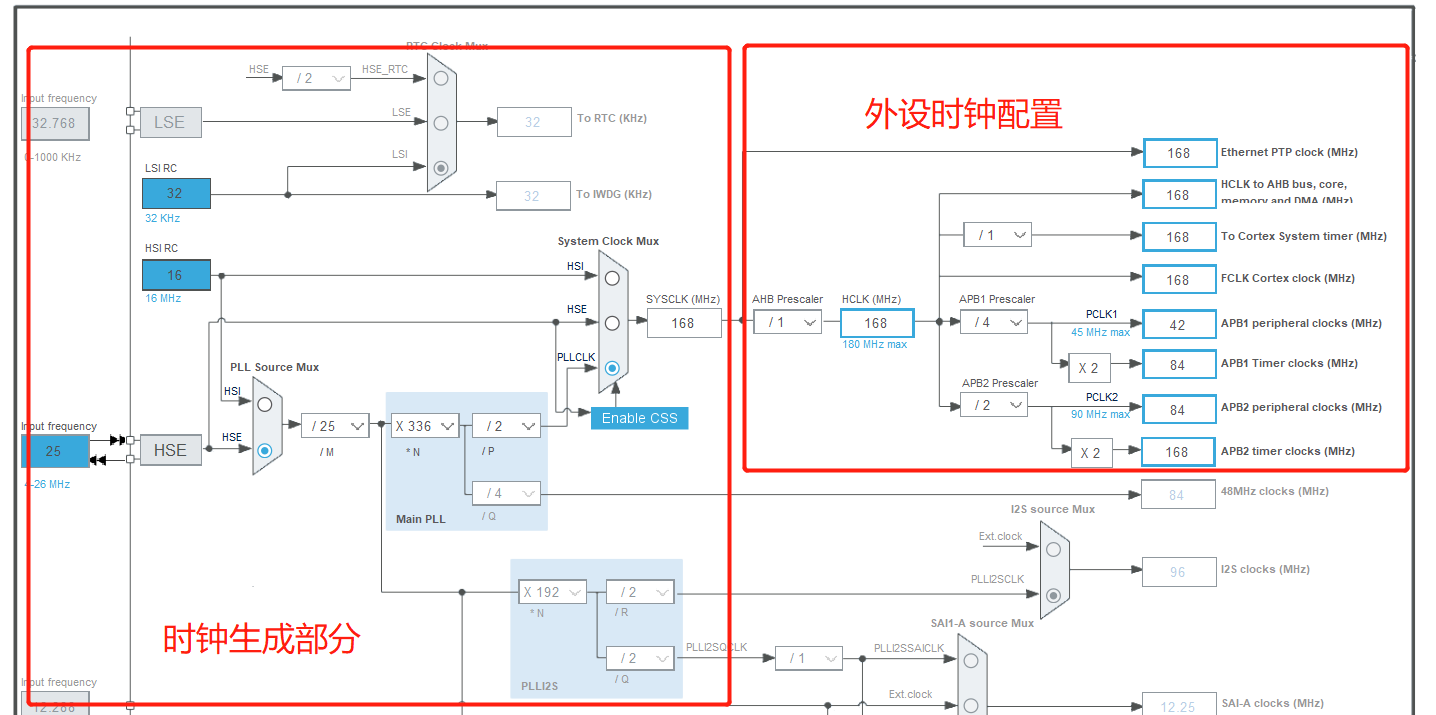

时钟树的配置主要分为两个部分, 第一部分是时钟的生成, 第二部分是外设时钟配置

***********************************正文:1系统时钟生成**************************************

时钟生成部分, 在硬件设计上,一般采用外部晶振作为时钟源, 配置时如下图,在RCC中将HSE时钟设置为外部晶振模式。

文章介绍了时钟树的配置,包括使用外部晶振作为时钟源,设置HSE为外部晶振模式,然后通过分频器和锁相环将25MHz的晶振频率转换为1MHz并倍频至168MHz作为系统时钟。系统时钟再经分频供给APB1总线,其中定时器时钟经过倍频器达到84MHz。

文章介绍了时钟树的配置,包括使用外部晶振作为时钟源,设置HSE为外部晶振模式,然后通过分频器和锁相环将25MHz的晶振频率转换为1MHz并倍频至168MHz作为系统时钟。系统时钟再经分频供给APB1总线,其中定时器时钟经过倍频器达到84MHz。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

615

615

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?