为落实原国家食品药品监督管理总局《关于适用国际人用药品注册技术协调会二级指导原则的公告》(2018年第10号)的要求,组织制定了《药物临床试验期间安全性数据快速报告标准和程序》,现予以发布。2018年5月1日后开始实施的临床试验,按照本标准和程序执行。

该标准要求申请人通过Gateway to Gateway(网关对网关)方式或在申请人之窗,向国家药品审评机构提交符合ICH

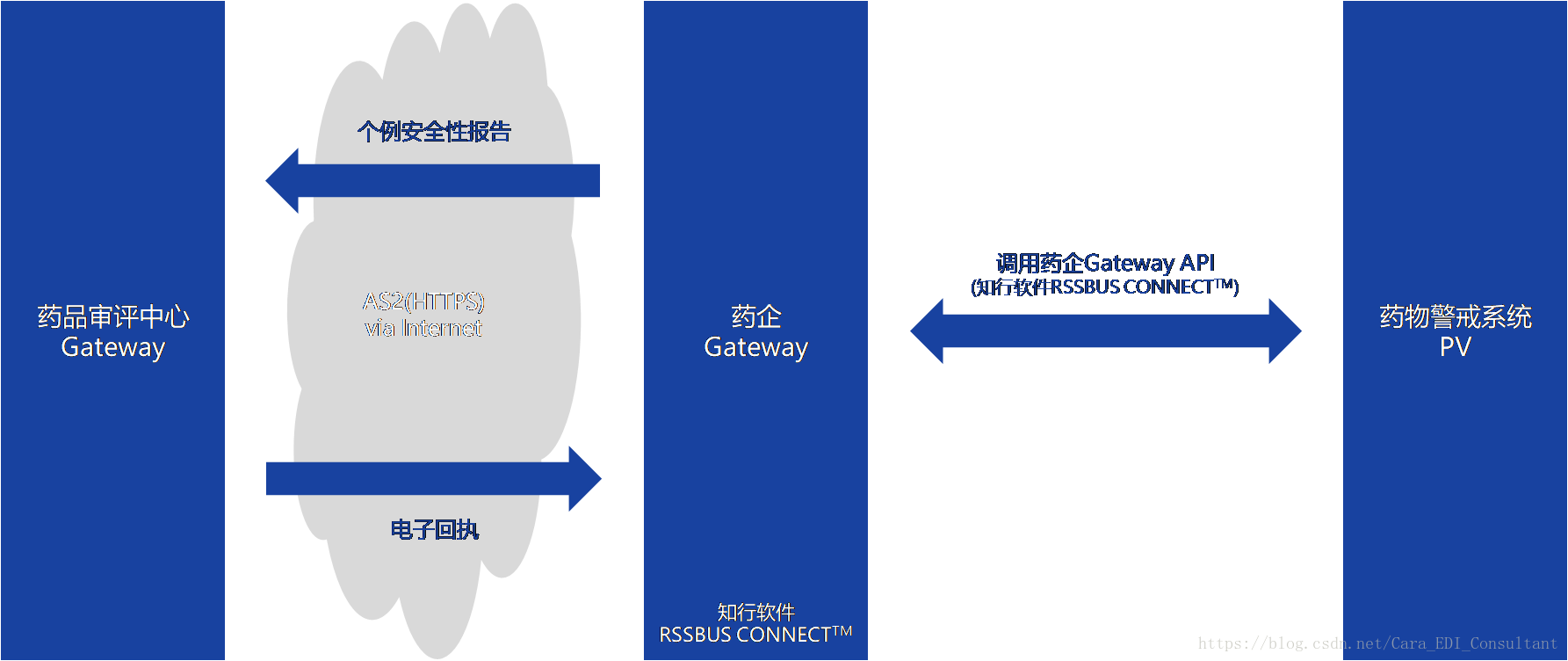

E2B(R3)规范的药物临床试验期间个例安全性报告,并对其进行分析评估,必要时按相关标准提出修改试验方案、暂停或终止药物临床试验等意见。以实现在药品的整个生命周期内、临床试验研究期间以及持续进行的安全性监测。Gateway toGateway(网关对网关)方式,采用AS2(HTTPS)传输协议,发送方发送个例安全性报告给药品审评中心,药品审评中心收到后,对个例安全性报告进行处理,根据处理结果向发送方返回电子回执(ACK)。[1]

Gateway 方式提交步骤

提交测试(正式)ICSR报告

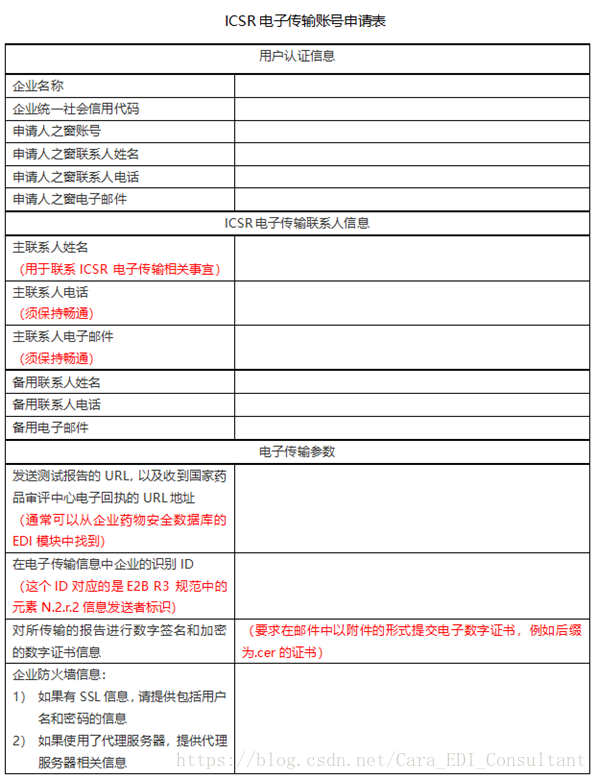

- 企业填写右侧《ICSR电子传输账号申请表》,用于注册个例安全性报告的电子传输测试账号;

- 完善电子传输参数,如URL、数字证书、ID等;

- 向药品评审中心发送一份测试(正式)的ICSR报告;

- 若收到药品评审中心确认测试报告有效的电子回执后,即表明成功建立测试(正式)传输ICSR的数据连接。

接收&校验ICSR报告

- 药品评审中心收到企业发送的ICSR后,进行校验,以确定是否满足E2B(R3)

药品评审中心返回电子回执

- 24小时内,药品评审中心回返回电子回执,告知企业ICSR提交情况(接受/拒绝)。

Gateway to Gateway解决方案

AS2(HTTPS)电子传输连接

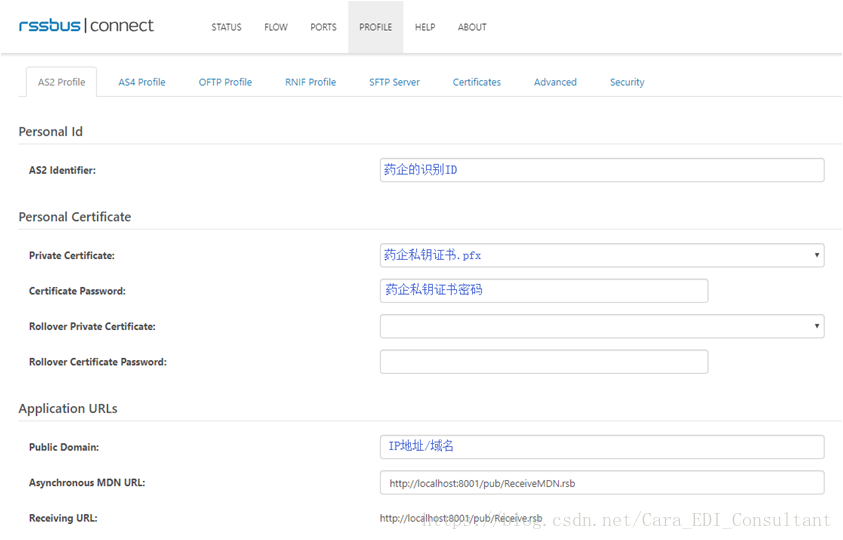

配置药企Gateway AS2(HTTPS)信息

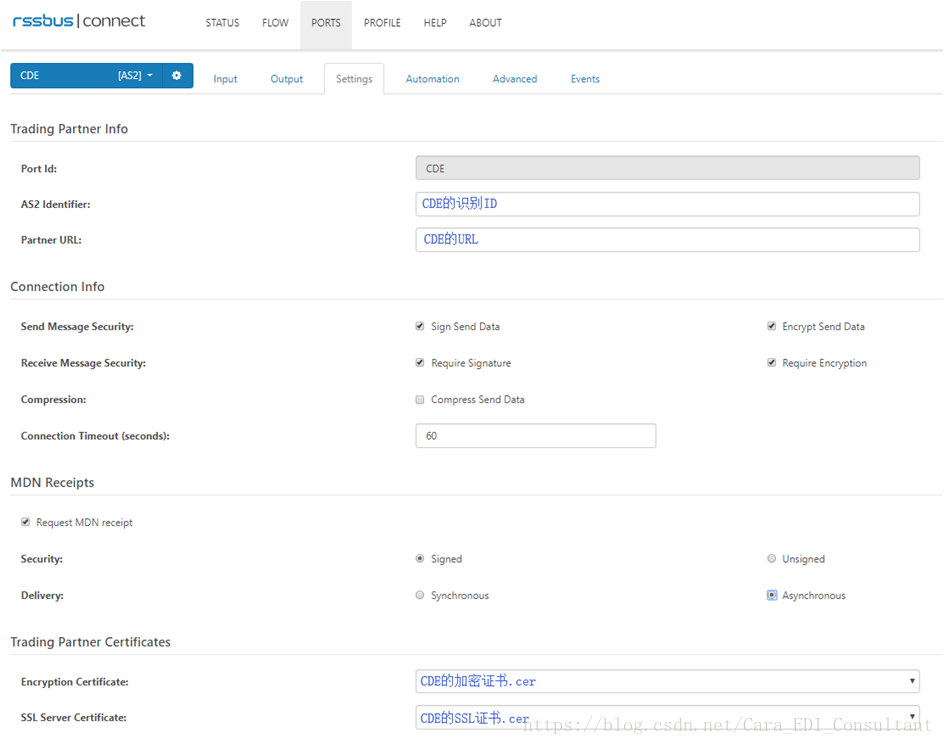

配置CDE Gateway AS2(HTTPS)信息

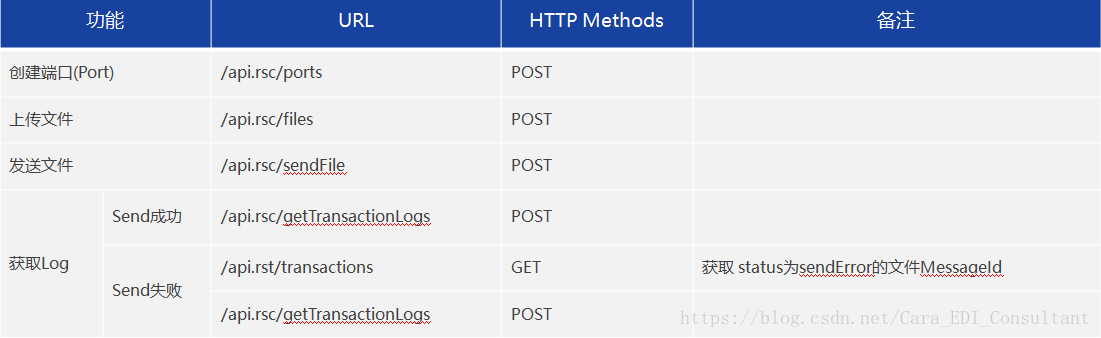

API方式集成药物警戒系统

关于PV系统与EDI系统的无缝集成,可以调用以下API:

注:API详细信息可参考RSSBus Connect EDI系统API文档。

如需了解更多,请看下方。

为遵循国家食品药品监管政策,确保临床试验期间药物安全性监测,本通知规定了药物临床试验期间安全性数据快速报告的标准和程序。申请人需通过特定方式提交符合ICH E2B(R3)规范的个例安全性报告,以便及时分析评估,必要时调整试验方案。

为遵循国家食品药品监管政策,确保临床试验期间药物安全性监测,本通知规定了药物临床试验期间安全性数据快速报告的标准和程序。申请人需通过特定方式提交符合ICH E2B(R3)规范的个例安全性报告,以便及时分析评估,必要时调整试验方案。

5479

5479

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?