教材:数字设计基础与应用 第二版 邓元庆 关宇 贾鹏 石会 编著 清华大学出版社

源文档高清截图在后

3.3 计数器

1、计数器(counter)是用来累计收到的输入脉冲个数的逻辑电路。微机系统的各种定时器和分频电路、计时电路本质上都是计数器。常见的计数器有模M计数器、加法计数器、减法计数器、双向计数器、BCD计数器、变模计数器等。模M计数器也称M进制计数器,状态图包含M个状态,每输入M个CP,状态循环一次;加法计数器和减法计数器分别随计数脉冲的输入递增、递减计数;双向计数器又称可逆计数器,既可以按加法规律又可以按减法规律计数;变模计数器的进制可以随控制量变化。计数器按照各个触发器状态更新情况的不同又可分为同步计数器和异步计数器。

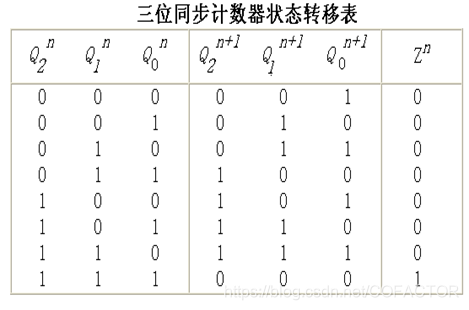

2、同步计数器的各触发器受同一输入计数脉冲(CP)控制,同步更新状态。同步计数器又称并行计数器。

3、2n进制同步计数器的连接规律是:由于是同步计数器,所以n个触发器的CP输入均接入同一个外部计数脉冲CLK。最低位的触发器Q0接成T’触发器的状态,即如果用JK触发器构成该计数器,则J0 = K0 = 1。对加法计数器,各位触发器在所有低位触发器的Q端均为1时,输入自身的激励为1,以便下一个CP到来时,低位向本位进位的时候状态就可以翻转,因此,从次低位开始,每两位之间需要增加一个与门,与门的输入分别接本位的Qi和低一位的Qi-1,只有Qi = Qi-1 = 1时,与门将1作为激励输入高一位。

可以发现,如果要低一位的Qi-1 = 1,那么就需要Qi-1 = Qi-2 = 1。以此类推,如果某一位计数器的输出Qi = 1,那么就必须有Q0 = Q1 = …… = Qi-2 = Qi-1 = 1。所以,触发器的Qi激励要求的输入是:Ti = Ji = Ki = Q0Q1……Qi-2Qi-1。对减法计数器,同样需要从次低位开始,每两位之间需要增加一个与门,但与门的输入分别接本位的Qi’和低一位的Qi-1’。类似地,触发器的Qi激励要求的输入是:Ti = Ji = Ki = Q0’Q1’……Qi-2’Qi-1’。加法计数器的最高位输入Tn-1 = Jn-1 = Kn-1。把或端与最高位的输出Qn-1作为一个与门的两个输入,就能在当Jn-1 = 1,Qn-1 = 1时输出进位信号1。下一个CP的变沿到来后,所有的Q端都将变成0。本条所有的i都要求i = 1,2,……,n-1。当同步计数器的每一位都为1时,令Zn = Q0Q1……Qn-2Qn-1,Zn会输出1,称为进位信号。

本文介绍了计数器的基本概念,包括同步计数器和异步计数器的原理,如2n进制同步计数器的连接规律和2n进制异步计数器的特点。重点讲解了加法、减法计数器,以及可逆计数器的工作方式。此外,还讨论了集成计数器如74163和7493的功能和应用,并阐述了计数器在计时、分频、脉冲分配和序列产生等领域的应用实例。

本文介绍了计数器的基本概念,包括同步计数器和异步计数器的原理,如2n进制同步计数器的连接规律和2n进制异步计数器的特点。重点讲解了加法、减法计数器,以及可逆计数器的工作方式。此外,还讨论了集成计数器如74163和7493的功能和应用,并阐述了计数器在计时、分频、脉冲分配和序列产生等领域的应用实例。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5478

5478

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?