从上次搭建熟悉SDK平台到现在已经几天了,这几天在学习zynq的ps+pl这种开发方式,现在以已有资料为原型,来重构一下单目摄像头的视频流传输的硬件部分。

在zynq中将不再以纯粹的verilog+ip核形式来做这个项目,而是通过block design直接将各模块的接口直接连接即可。但是也要我们自己懂各种协议,在此项目中AXI各组件协议会被用到,并且我看了在之后这些模块也会被大量频繁地使用,于是了解他们是怎么运行的而不是简单的像搭玩具一样地连接各模块显得尤为重要。

这里以记录的方式重温一下各模块的功能,以及各配置吧。

这里先说一嘴,下面的资料上网都能搜到,而且更齐全准确率更高更客观,慎看。以及视频流传输包含HDMI,ov5640,axi各模块,ddr3,我不会过多展示和介绍hdmi相关模块,甚至有的不讲,没必要,会用就行。

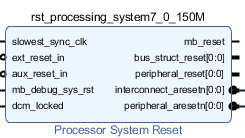

1、Processor System Reset

这是他的接口信号以及内部配置。这个只需要注意一下in就是输入,out输出,以及resetn就是低电平有效,reset是高电平有效即可,我感觉没什么需要赘述的,甚至你可以直接用一个输出复位来控制全部(除了一些EMIO口上的复位信号)。这里分了很多个复位可能是为了大项目方便控制吧,在当前项目无特殊作用。

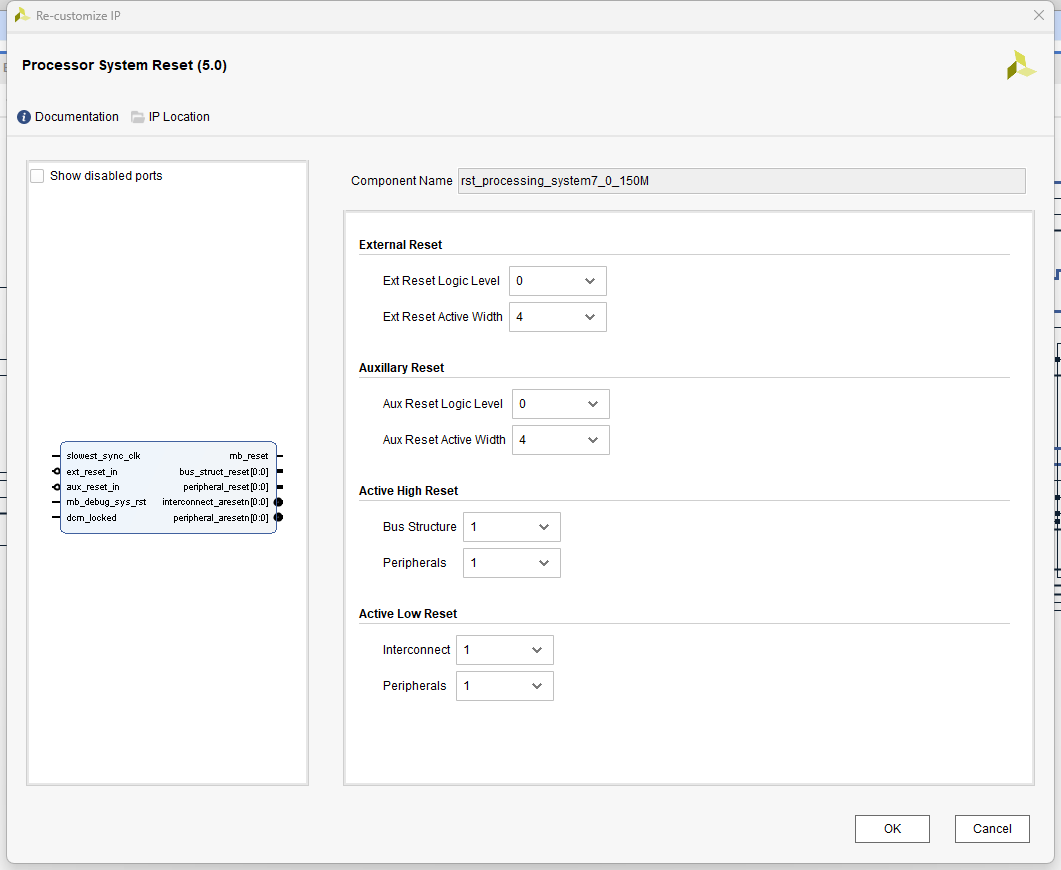

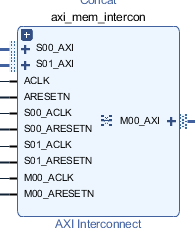

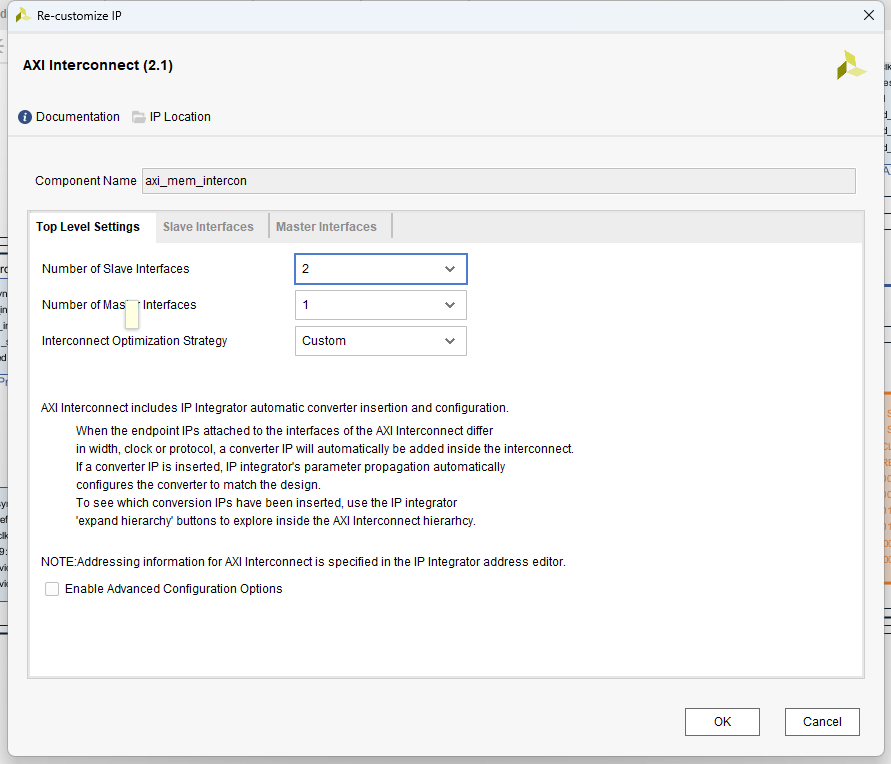

2、AXI Interconnect

这是AXI互联模块,这个最主要作用是可以设置多主机多从机的模式,然后还有将axi3协议转向AXI4接口的能力,例如GP就是一个比较典型的AXI3接口,但是这里基本都是用AXI4,所以都得转。

3、AXI Video Direct Memory Access

这个模块简称AXI VDMA,是专门为视频流传输开辟的模块,从DMA演变过来的,要介绍这个得先讲讲AXI DMA模块,AXI DMA也有转协议的功能,对于视频流来说肯定要满足AXI Stream协议的,但是我们ps通信是用AXI4与AXI3进行通信,所以无法直接接收视频流数据存进DDR3,所以需要这个模块连接在他们中间进行协议转换,具体转换逻辑是视频流数据输入然后进入fifo,达到一定长度后以axi4协议突发传输出去(包含突发长度),因为fifo缓冲区能存储视频流数据(只要一直发一直发到溢出),一般不会出现这种情况的,因为有消隐时间,不会说真的无穷无尽发送数据。

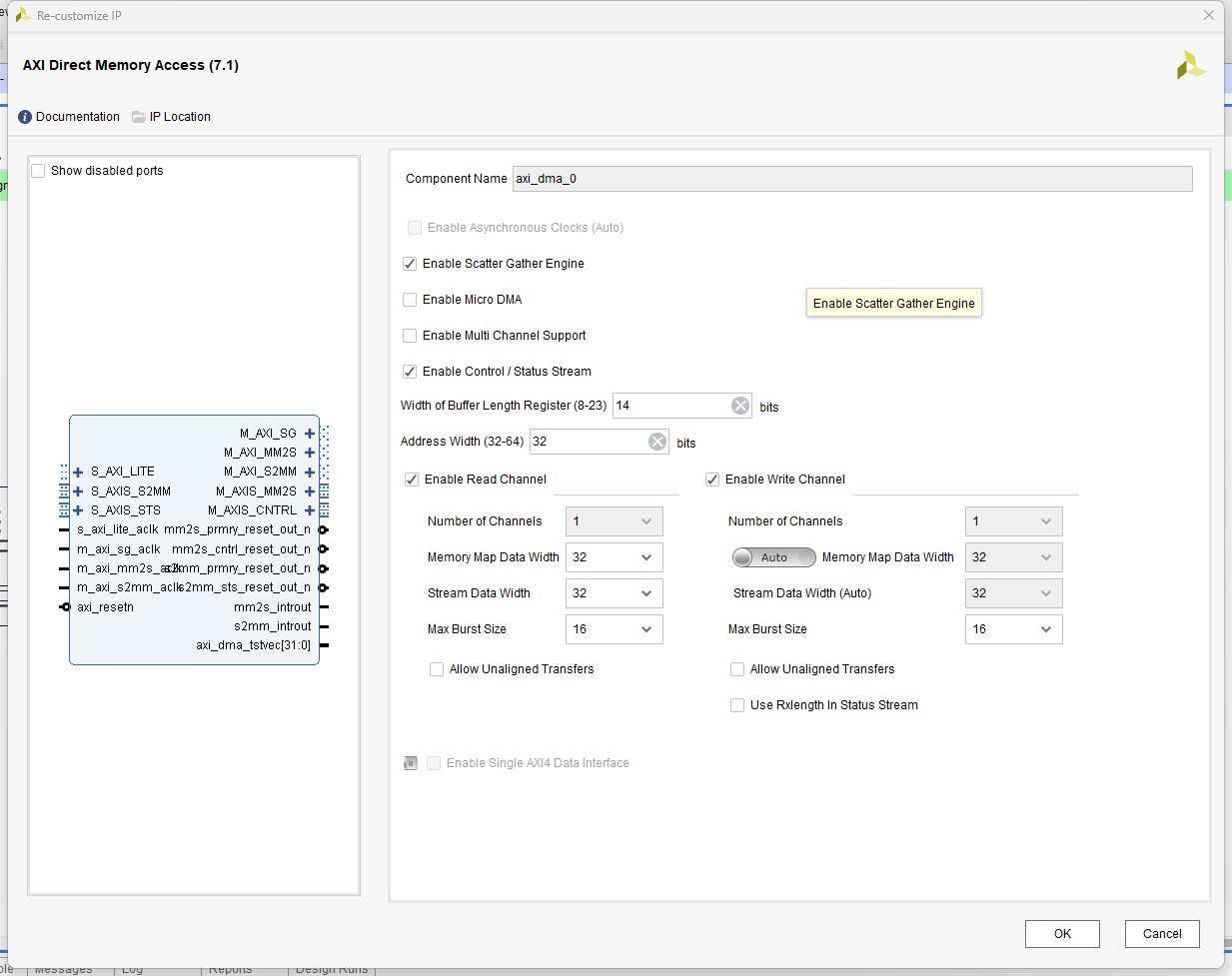

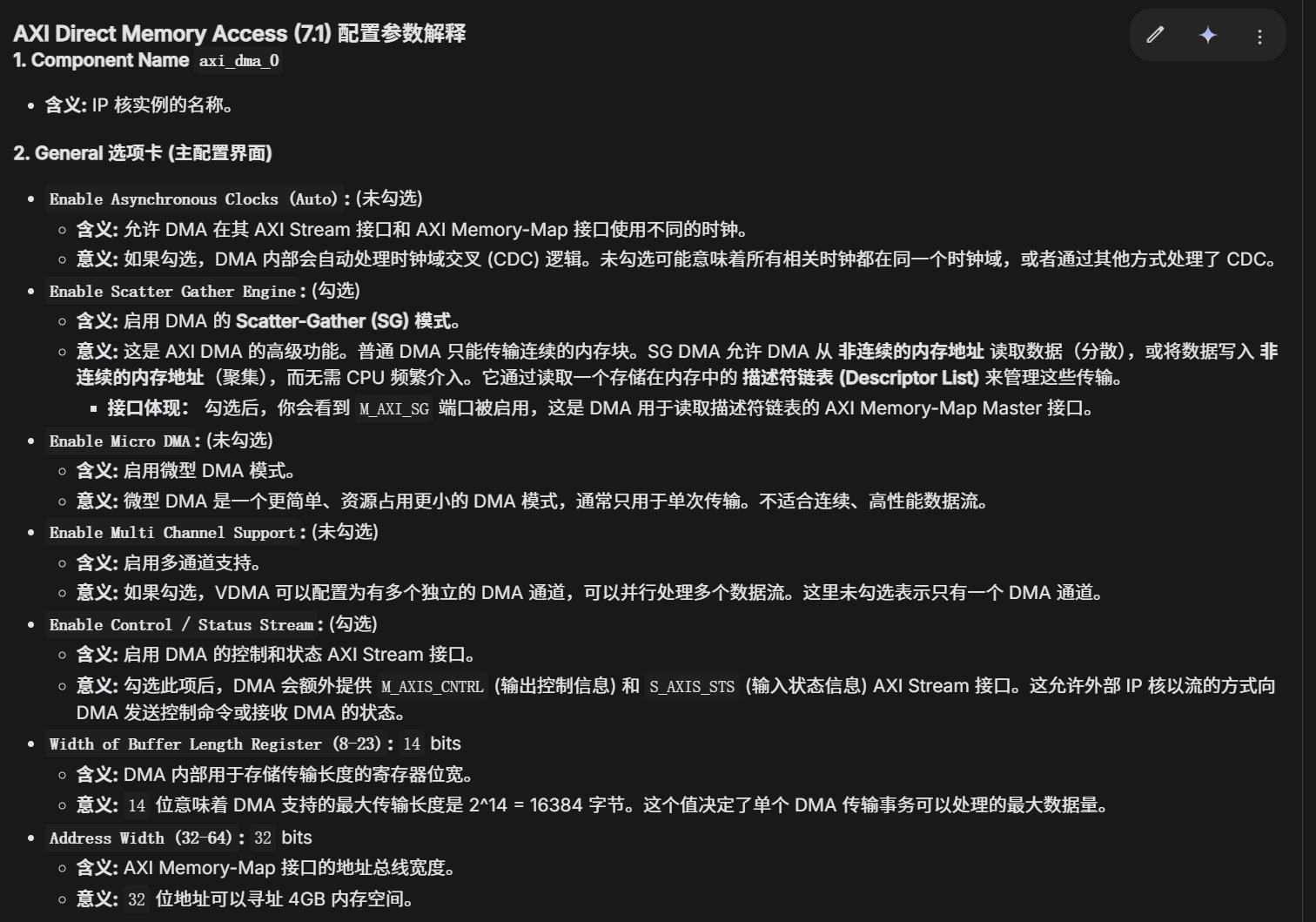

上图是AXI DMA的配置部分。

不会很难,不过多赘述。

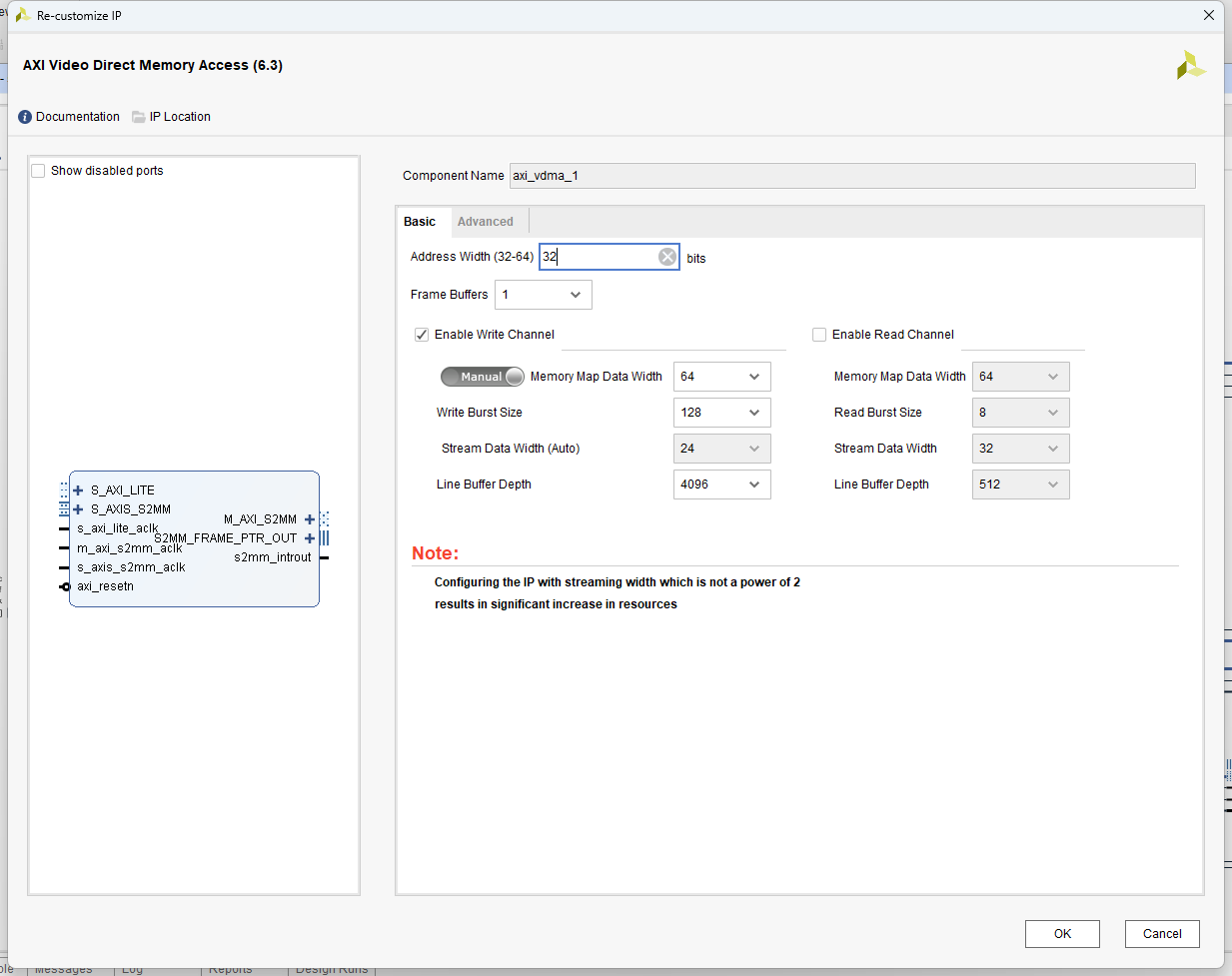

VDMA接口和DMA挺像的,vivado提供的配置简单很多。

这里的auto配置是等你连线后才会显示的莫慌。然后这里是M_AXI_S2MM本质是是M:主机,AXI:AXI4协议,S2MM:slave to memory map,被作为主机接口时,就是要发送数据给ddr3的,被作为从机接口时,就是一个中转站,接口数据然后传给ddr3的。

frame buffer是帧缓冲,这里写1就是每次只存一帧就显示了,一般缓存3帧比较好(别问我我不知道)。这里的s2mm_introut就是数据传给ddr3后就会发生中断,不过这里也没用到。

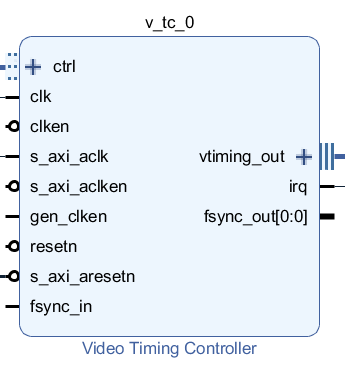

4、Video Timing Controller

这个模块顾名思义,就是控制视频输出输出时机的(可以直接通过接口信号看出)

ctrl是外界输入的接口(axi4),vtc作为从机,fsync_in应该是有关帧同步的信号,这里不需要连接他不做解释,vtiming_out接口是hdmi显示的控制接口,内部有行场同步信号和视频有效信号以及消隐信号(就是无效时间就拉高,暂时可以这样理解)。

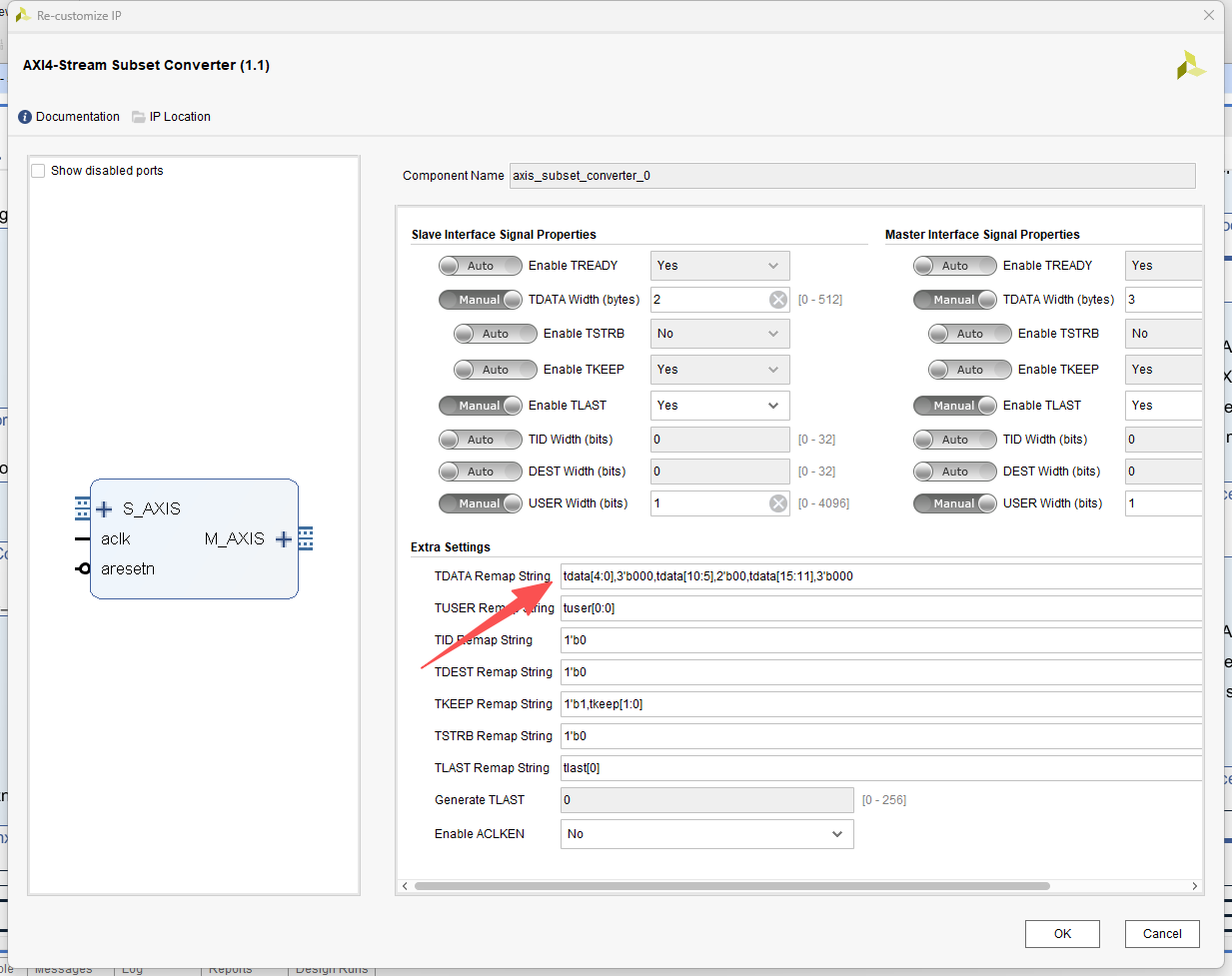

5、AXI4-Stream Subset Converter

这个是可以改变数据位宽的模块,怎么改变可以进去写公式。

信号名字跟着他来就行了,然后由于我们的ov5640输入是8比特(设置下),我们需要人为将这两个八比特数据拼接起来然后发送出去(也就是说这个模块接收到16位宽的数据),遵循RGB565协议,然后由于我们是用HDMI输出,要求RGB888输出,所以需要我们去改变,改变方法遵循把RGB565对应数据放在高位即可,具体看红色箭头指向。

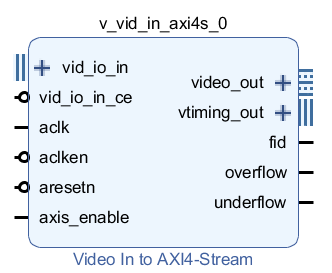

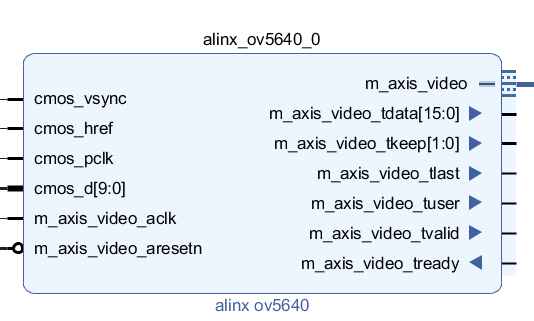

6、alinx ov5640

这是厂商自己给的ip核,可以直接用,但是也是通过调用ip核和verilog实现的,介绍一下由来

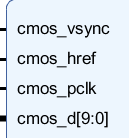

这是标准的视频输入转AXI4-Stream模块,但是ov5640的输入是这样的

其中两位数据还是无效数据,也就是说一次传输1字节数据,还有行场同步信号,但是接口要求输入消隐信号,以及不间断的2字节信号,这样之后,才能给我们去转stream协议,厂商估计觉得太麻烦了,所以干脆自己写了一个,刚好我翻到源代码,我讲一下实现方法:先将2字节的数据拼接好然后写入fifo,然后一有数据读使能就拉高就行了(虽然你可能觉得这不就是一个一个慢慢传吗,那没办法啊,人家写了那直接用就行了,会个fifo真能走天下了)。

这是他们自己创建的ip核,直接用即可。

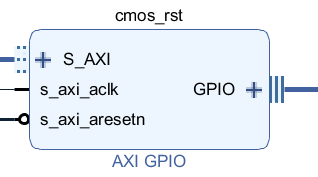

7、AXI GPIO

这个不介绍。

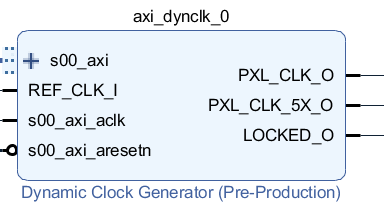

8、时钟动态分频器

这个模块很不错,可以通过ps端去配置时钟,具体逻辑我不知道,但是不影响使用。

好了文章到这里结束了,下一期我将用这些模块连接成视频流传输的基本通路。祝您生活愉快。

8568

8568

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?