本人纯小白,大二主要学习PL端,大三报名了FPGA创新创业大赛,需要用zynq7020进行开发,找了客服要了板子例程,第一次接触到PS端(印象中stm32就是),各种库函数数不胜数,目前正在学习中,但是既然例程是ps开发居多,那就稍微学习一下ps端。

资料我是去淘宝找了开发板客服索要资料他给我的,我就不直接提供了。

平台:Win11 版本:Vivado2017.4

如果要对例程进行增删改查,最好就是平台和工具版本要和例程对的上,不然开发中会不断出现各种错误。

这里用的是AX7Z010板子的资料,有需要的可以私聊我(侵权会删)。

用的是资料里面的例程SDK开发的第十章DMA回环开发,直接导入例程即可。我尝试去跟着思路直接搭建,发现:我不理解SDK里面各部分的关系,以及我在block design时发现AXI DMA的S2MM接口信号和AXI Interconnect信号没有完全对上(AXI Interconnect多了很多信号,但是又不能直接删去)。我不知道例程的这个模块为什么信号完全对上了,于是我打算给它换一下,看看还能不能成功。

好了进入正题,修改步骤如下:

1、导入AXI-interconnect模块,然后把各接口连接好(时钟,复位,以及AXI接口)

2、把原来的AXI-interconnect模块删去。然后点击Validate design,没有错误后去sources那里点击”create hdl wrapper“生成verilog顶层,然后再点击”generate output product“生成输出(必要步骤),然后去file-export-export Hardware里面生成hdf文件(应该是ps端映射之类的),并且重新生成比特文件。

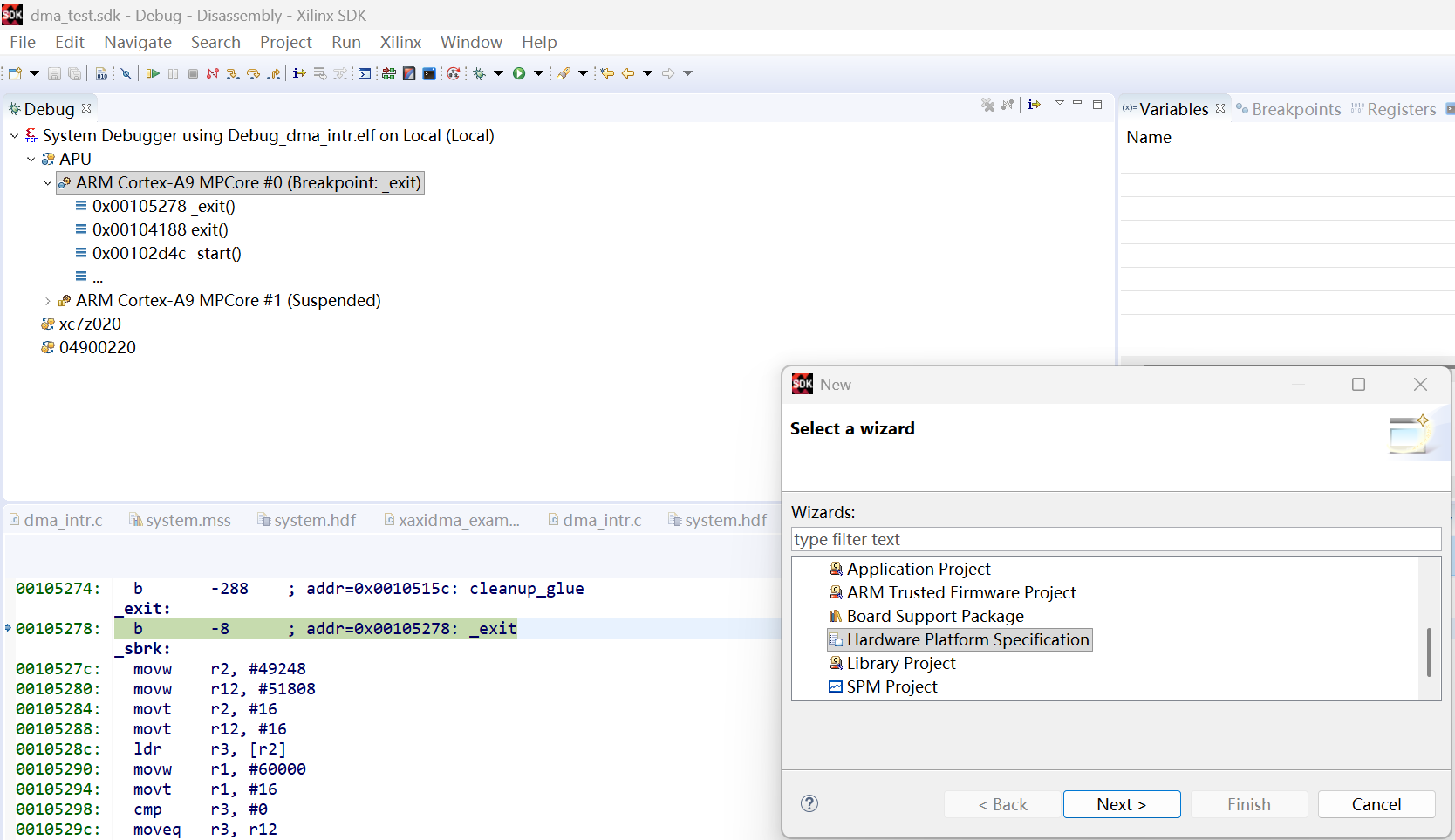

3、通过launch SDK打开工程,会发现有两个platform平台,以及一些c语言工程。这里解释一下,这两个平台都是例程自己的,我们不要这两个。直接file-new-other,在xilinx里面找到Hardware Platform选项。

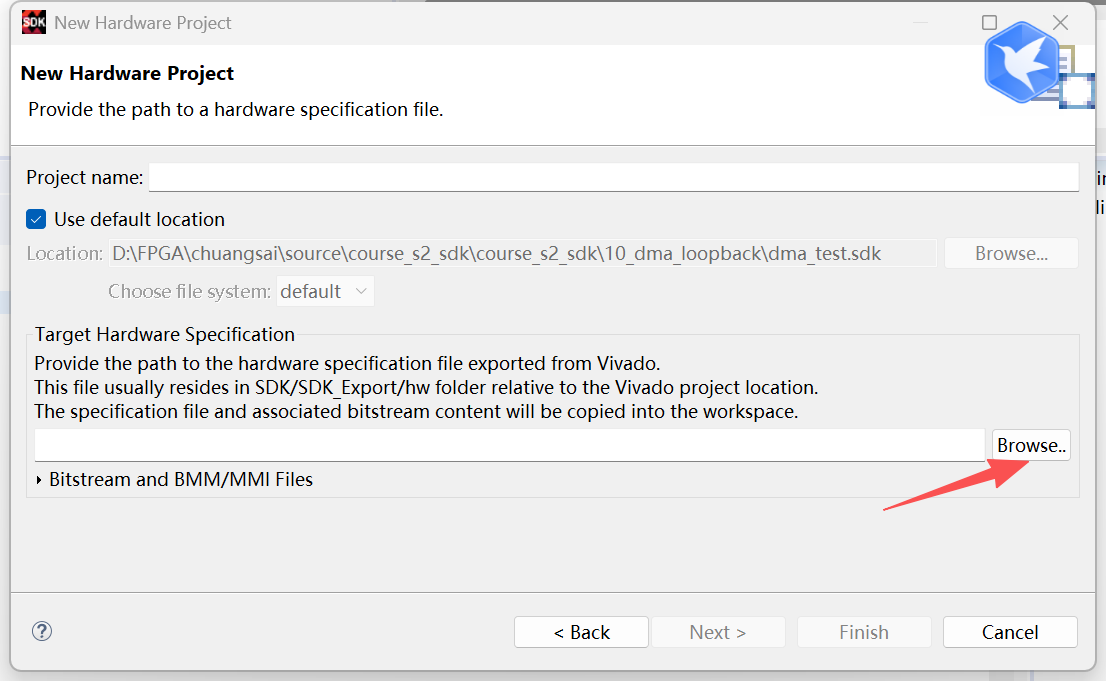

name不用管(你想填啥都行,英文+数字),然后点击下面的browse,选中刚刚生成的hdf文件。默认目录应该是在.SDK下。

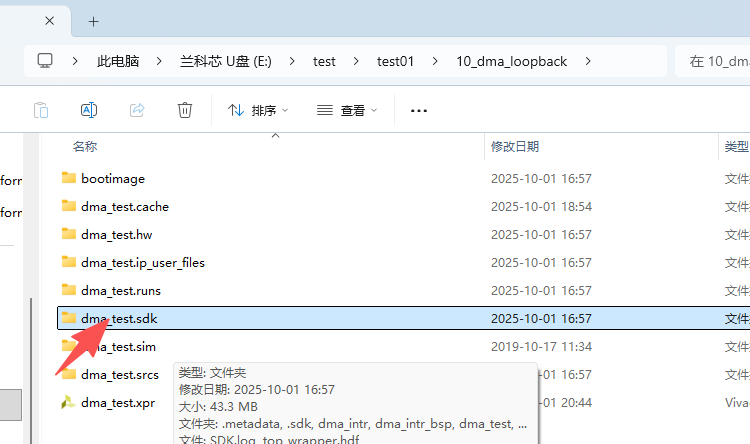

点进去直接就有一个hdf文件了,如果不放心可以在文件夹里面看一下修改日期,如果对的上那就是新的文件了。选中后点击完成,等一会,等到SDK下方不会再弹出消息,最后应该是什么project finished这样子?反正提示消息很明显,差不多等个几分钟就好,这样新的platform就创建好了。

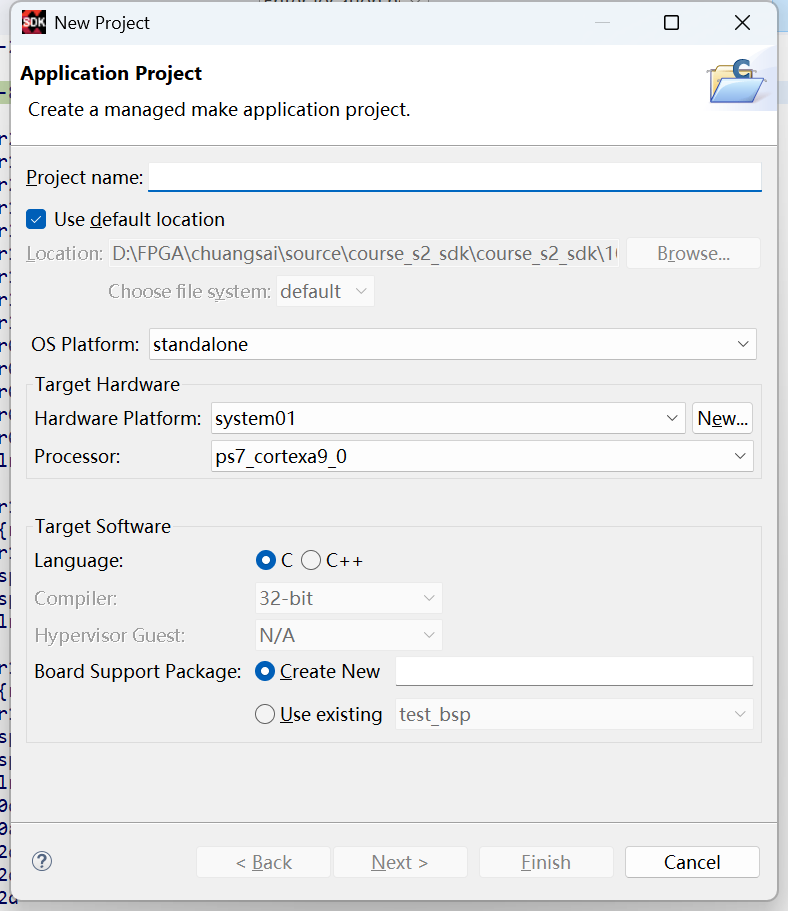

4、接下来就是导入c工程,直接file-new-application project里面选中那个fsbl的。

配置的话也不难,name ,Hardware Platform(选中刚刚创建的那个)记得别搞错就行,name自己想啥取啥,然后点击finish即可。

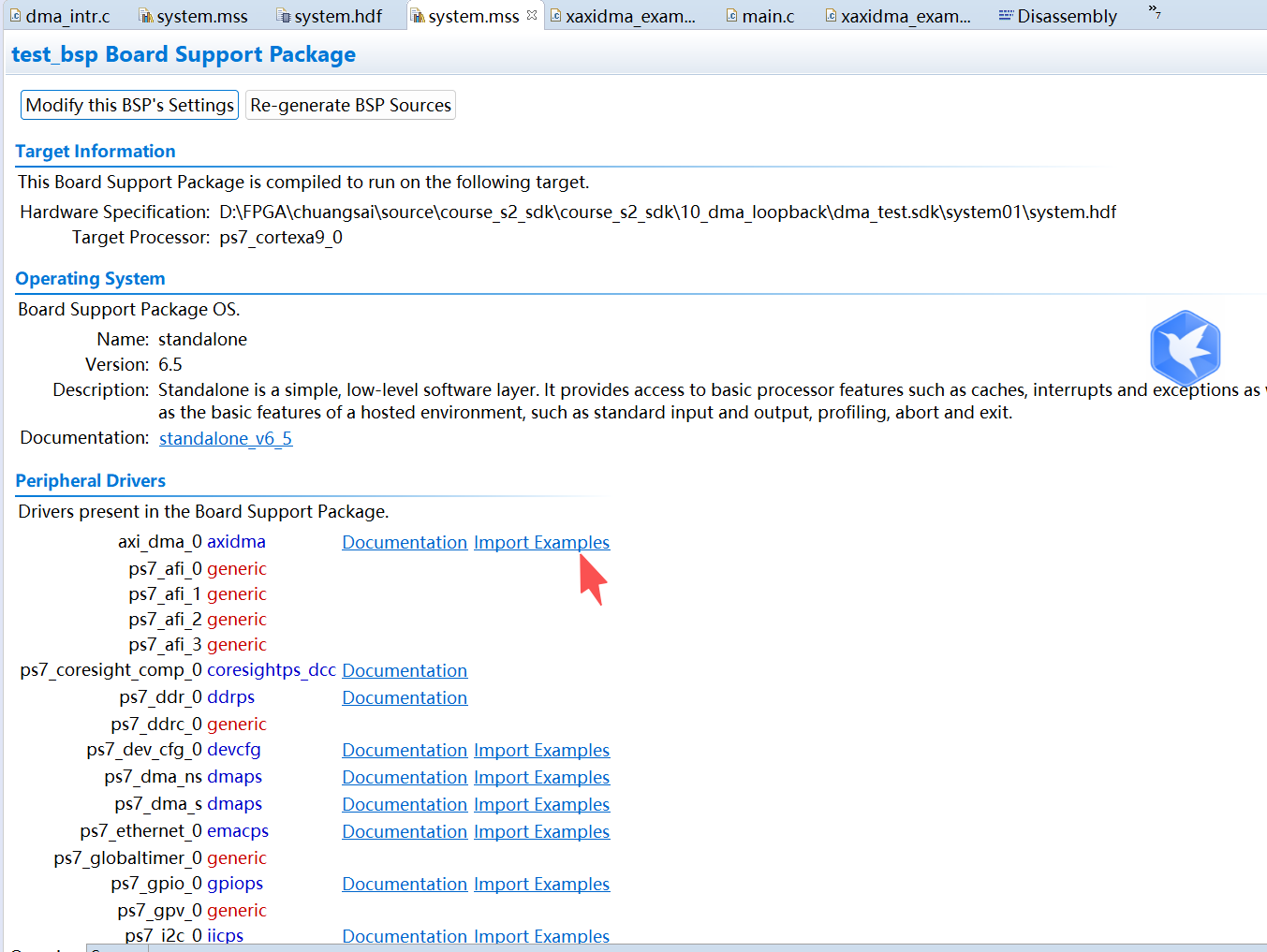

5、然后会生成一个bsp和一个初始化工程,例如fsbl ,fsbl_bsp。然后点击fsbl_bsp里面的system.mss,如图

然后选那个后缀是poll的。完成后会生成一个新的工程再project explorer(sdk左边的界面),然后这个工程就是对应platform里的,然后直接进入新工程/src/main文件,把整份文件完完全全改为原来的工程的src文件的main文件。然后保存,下面会显示编译工程中,等待finish即可。

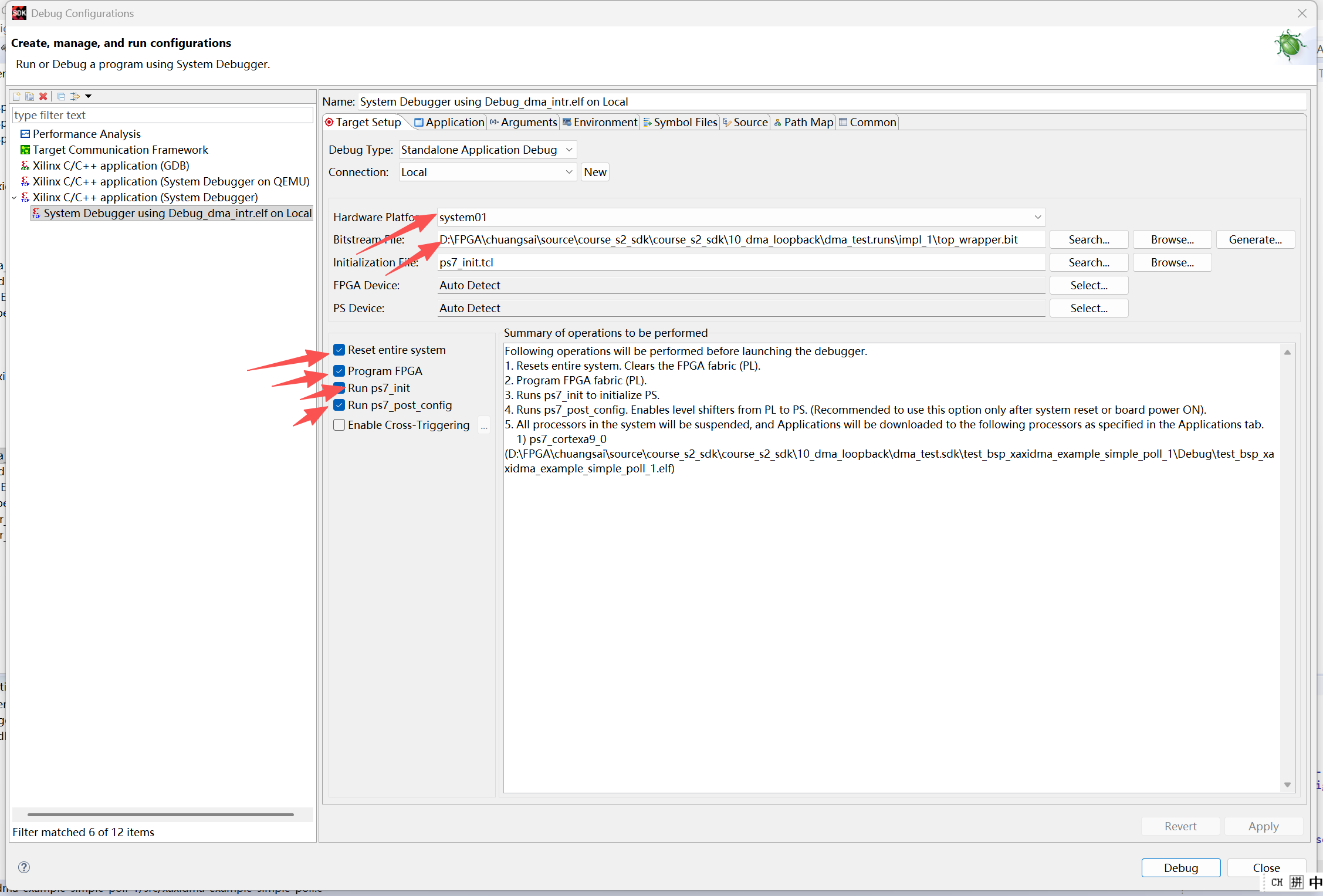

6、运行就不展示了,展示如何调试。可以去vivado的block design里面看到是有ila的,于是直接SDK-run-Debug configuration,这里需要修改的有:

打勾的和我一样即可,平台选中刚刚创建的,bitstream file选中自己生成的(一般在文件夹里面的run/imply_1)。然后重要的来了(卡我很久的一个bug)

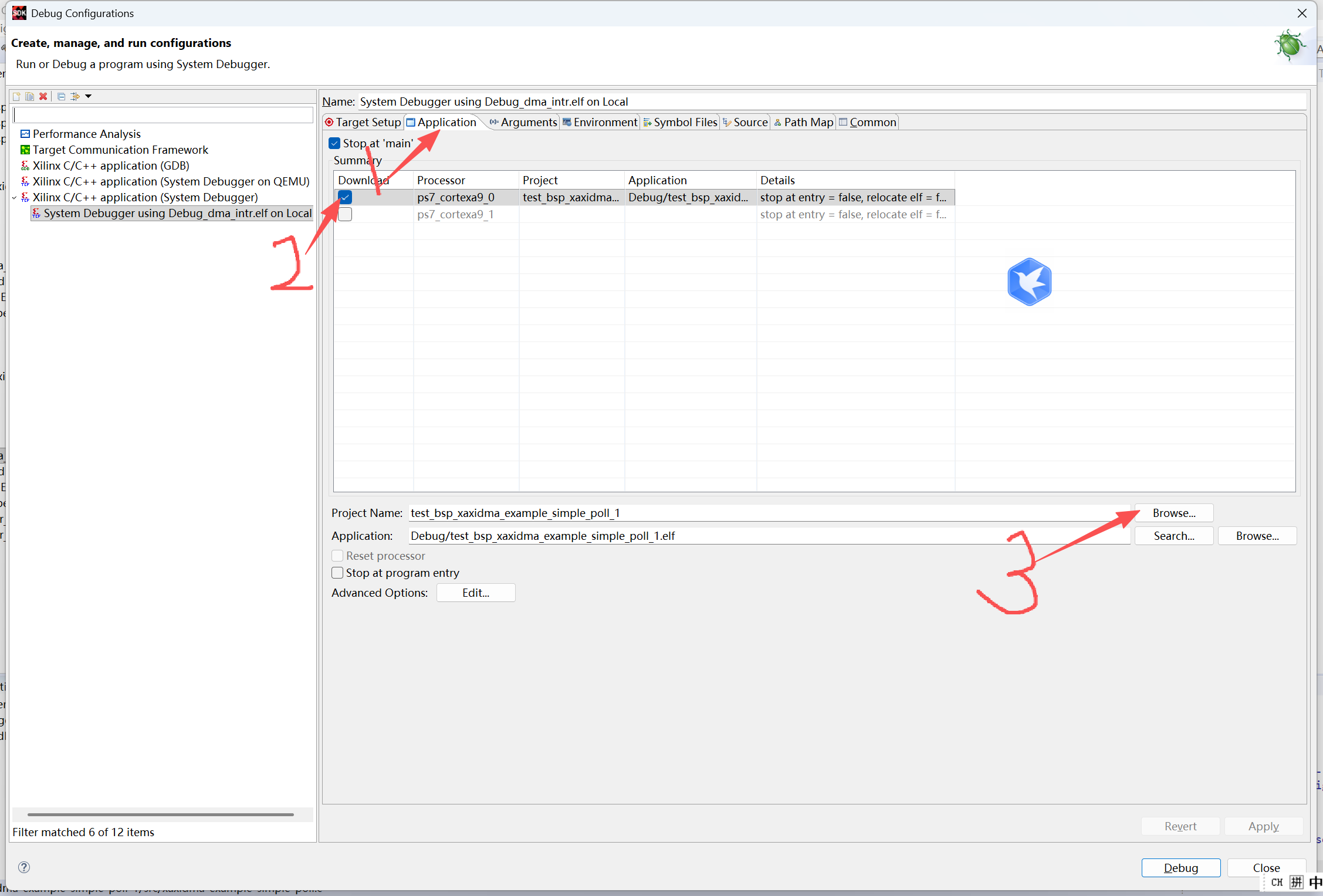

按照步骤即可,然后点击刚刚创建的那个poll工程(点进去至少会有两个工程,如果只有一个说明你poll工程没创建成功),然后点击debug-yes,会弹到另一个界面(想恢复,直接去找ai问SDK跳转到debug专属页面怎么回去)。对了,记得给板子线连接好,不然会一直失败。

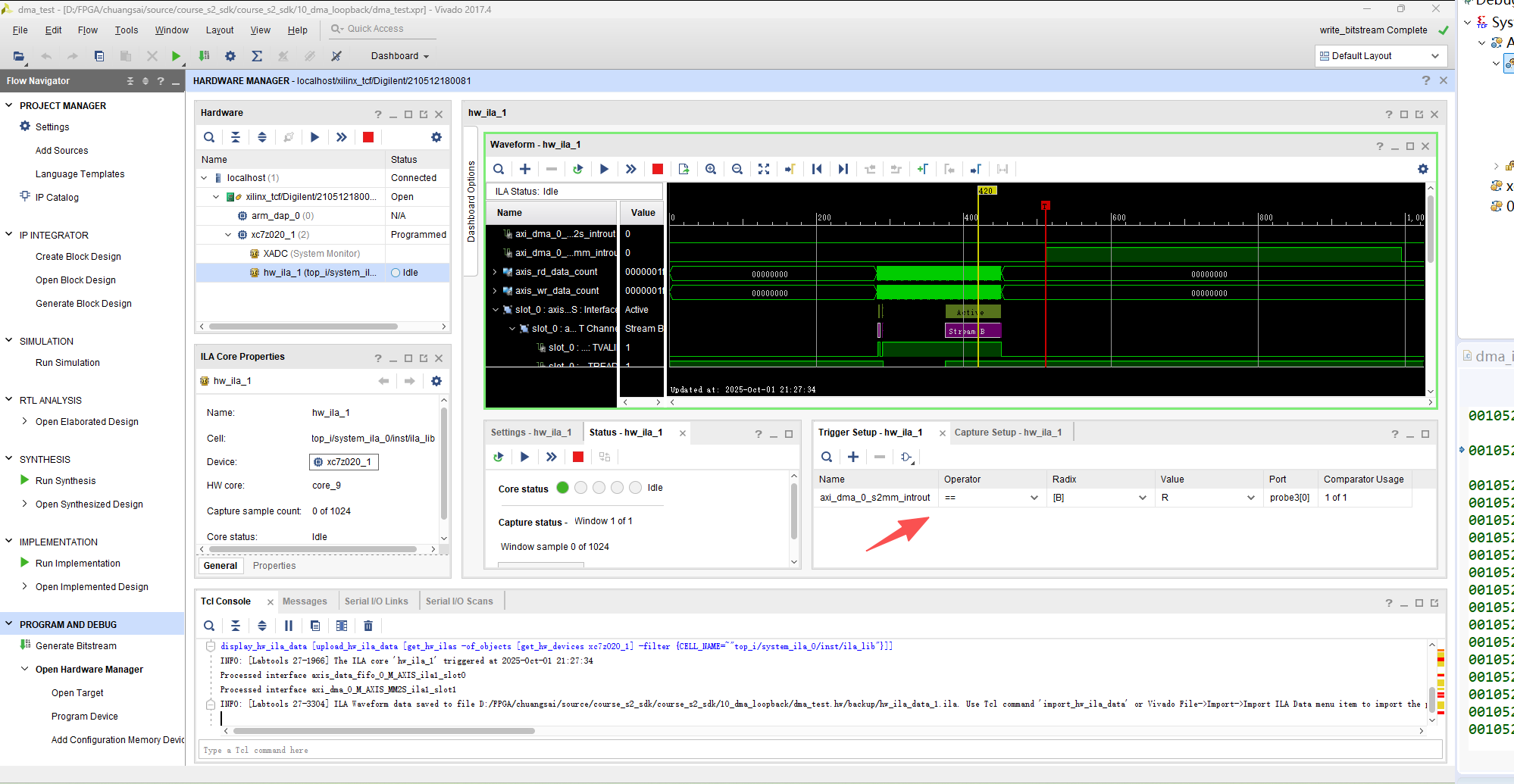

7、回去vivado,open target里面的自动连接。然后就会弹出ila的图像,点击波形上方那个三角形,然后回到SDK,点击resume(Source正下面),然后再回去看波形,就会发现有了,这里要解释一下

这里是一个设置触发方式的地方,切记切记。

好了波形出来后就算成功了,讲错和讲多的地方希望多多包涵,我只是一个来记录自己学习的小白,祝您生活愉快。

4220

4220

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?