74LS85的IP核设计

今天更新一款74LS85芯片的IP核设计实例。

74LS85是一款4位数值比较器芯片,作用是可对两个4位二进制码和BCD码进行比较,实物图与引脚图如下:

| 名称 | 引脚 |

|---|---|

| 2位电源正极与接地 | Ucc ,GND |

| 2个4位二进制数 | A0A1A2A3,B0B1B2B3 |

| 3位级联 | I1,I2,I3 |

| 3位输出 | OA,OB,OC |

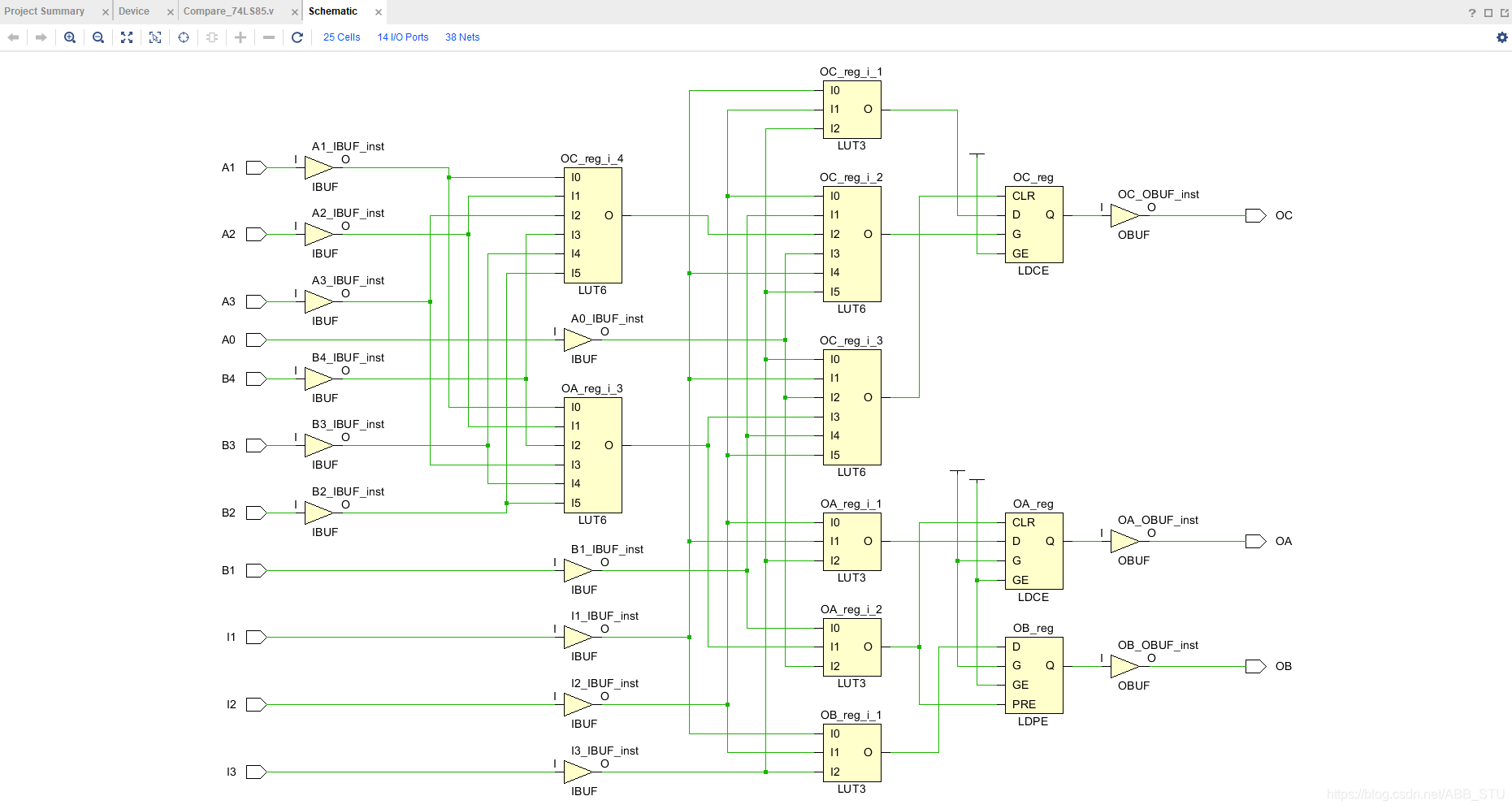

Verilog实例代码如下

// 74LS85的Verilog语言设计

module Compare_74LS85(

input wire A0,A1,A2,A3,B1,B2,B3,B4, //8个输入信号

input I1,I2,I3, //级联信号输入

output reg OA,OB,OC //输出信号

);

wire[3:0] A,B; //输入信号是4个一位,需要拼接成1个4位

A={A0,A1,A2,A3};

B={B1,B2,B3,B4};

always@(*) begin //根据芯片手册中功能表转换成代码

if(A>B)begin

OA = 1;

OB = 0;

OC = 0;

end

if(A<B)begin

OA = 0;

OB = 1;

OC = 0;

end

else if(I1&!I2&!I3)begin

OA = 1;

OB = 0;

OC = 0;

end

else if(!I1&I2&!I3)begin

OA = 0;

OB = 1;

OC = 0;

end

else if(!I1&!I2&I3)begin

OA = 0;

OB = 0;

OC = 1;

end

else if(I3)begin

OA = 0;

OB = 0;

OC = 1;

end

else if(I1&I2&!I3)begin

OA = 0;

OB = 0;

OC = 0;

end

else if(!I1&!I2&!I3)begin

OA = 0;

OB = 0;

OC = 1;

end

end

endmodule

一介书生。

一介书生。

本文介绍了如何设计74LS85的IP核,74LS85是一款4位数值比较器,可以比较4位二进制码和BCD码。内容包括芯片的功能及引脚图。

本文介绍了如何设计74LS85的IP核,74LS85是一款4位数值比较器,可以比较4位二进制码和BCD码。内容包括芯片的功能及引脚图。

7582

7582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?