74LS138译码器IP核设计

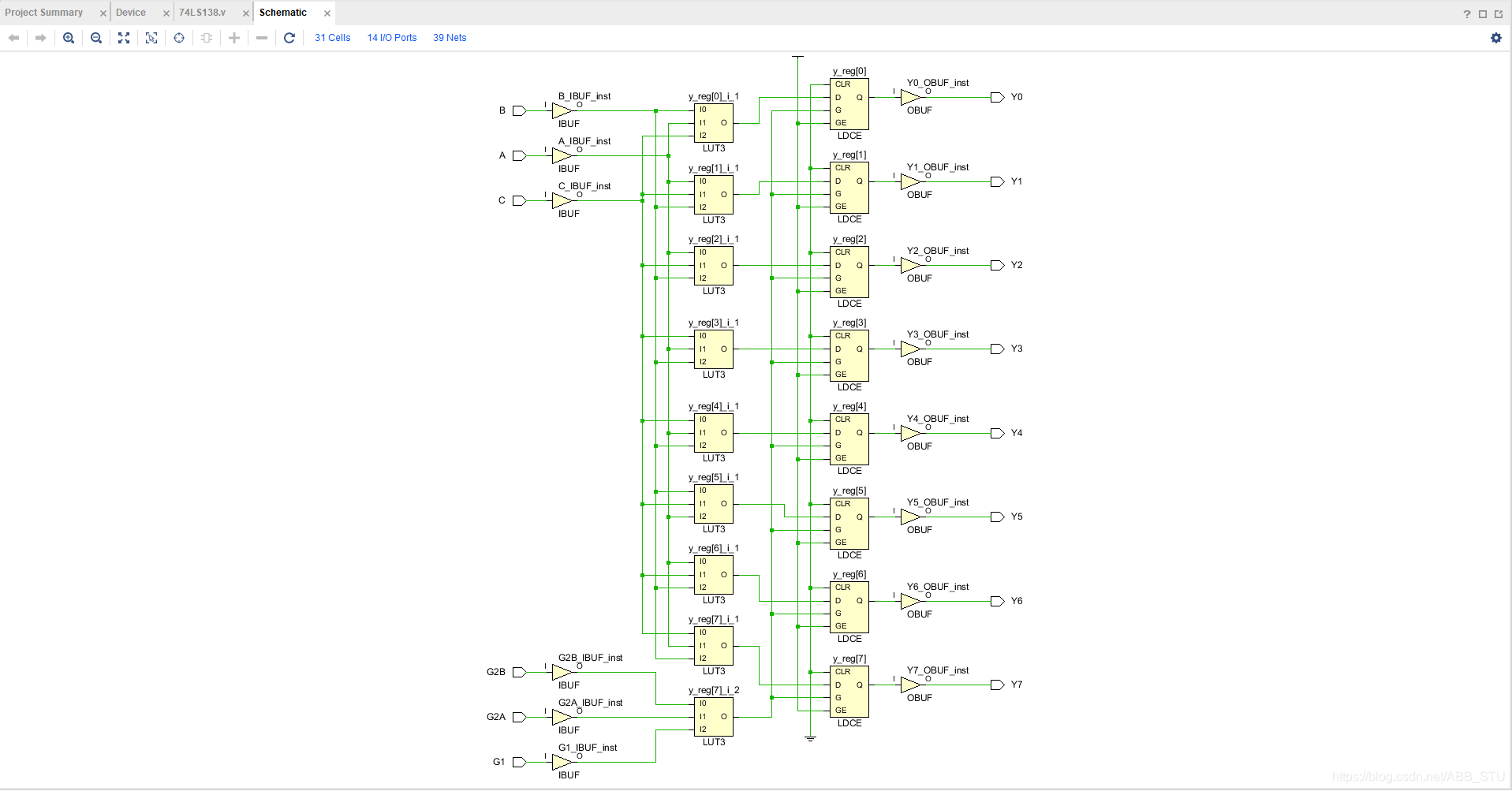

今天更新74LS138 译码器的IP核设计,Verilog语法实现。

74LS138为3位的二进制译码器,其实物图与引脚图如下。

74LS138实物图

74LS138引脚图和真值表

其中G1,G2A,G2B为片选信号,当G1=1,G2A=0,G2B=0时,译码器工作

A,B,C为译码地址输入端,Y1~ Y7为译码输出

//74LS138的IP核设计

module decode74LS138(

input A,B,C,

input G1,G2A,G2B,

output Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7

);

reg [7:0] y;

integer i;

always@(*)begin

if({G2A,G2B,G1==3'B001})begin

for(i=0;i<8;i=i+1)begin

if ({C,B,A} == i) y[i]=0;

else y[i]=1;

end

end

end

assign Y0 = y[0];

assign Y1 = y[1];

assign Y2 = y[2];

assign Y3 = y[3];

assign Y4 = y[4];

assign Y5 = y[5];

assign Y6 = y[6];

assign Y7 = y[7];

endmodule

一介书生。

一介书生。

这篇博客介绍了如何使用Verilog语法设计74LS138译码器的IP核。74LS138是一个3位二进制译码器,其工作条件为G1=1, G2A=0, G2B=0。内容包括译码器的实物图、引脚图和真值表。"

89337827,8507485,物联网信息安全:挑战与对策,"['物联网信息', '网络安全', '密钥技术', '加密算法', '信息安全策略']

这篇博客介绍了如何使用Verilog语法设计74LS138译码器的IP核。74LS138是一个3位二进制译码器,其工作条件为G1=1, G2A=0, G2B=0。内容包括译码器的实物图、引脚图和真值表。"

89337827,8507485,物联网信息安全:挑战与对策,"['物联网信息', '网络安全', '密钥技术', '加密算法', '信息安全策略']

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?