1.系统概述

本设计在AlteraCyclone II EP2C35 平台上,利用锁相环、计数器等数字电路,产生占空比可随时间自动变化的PWM波形,从而控制LED灯的亮度变化,实现以2s为周期的LED灯的呼吸显示效果。

2.系统原理图

如图 1所示,input和output为输入输出模块。altpll0为锁相环模块,inclk0为输入引脚,c0为输出引脚。count10为十分频计数器模块,clk为输入引脚,outclk为输出引脚。pwm为脉冲宽度调制模块,clkus为输入引脚,pwmout为输出引脚。PIN_U11为FPGA开发板上的50MHz晶振产生引脚,PIN_W22为LED灯1的电平输入引脚。

图1 系统原理图

晶振产生的50MHz信号从input输入后经过锁相环处理,将不稳定的晶振转换为稳定可靠的10Mhz时钟信号,从锁相环模块的c0脚输出。10MHz时钟信号又从十分频计数器模块的clk引脚输入,在outclk 引脚输出所需要的1MHz脉冲信号。1MHz的脉冲信号通过脉冲宽度调制模块,从clkus引脚输入,pwmout引脚输出。将调制处理后的信号接PIN_W22引脚,即接LED灯,从而实现对LED亮度的控制。

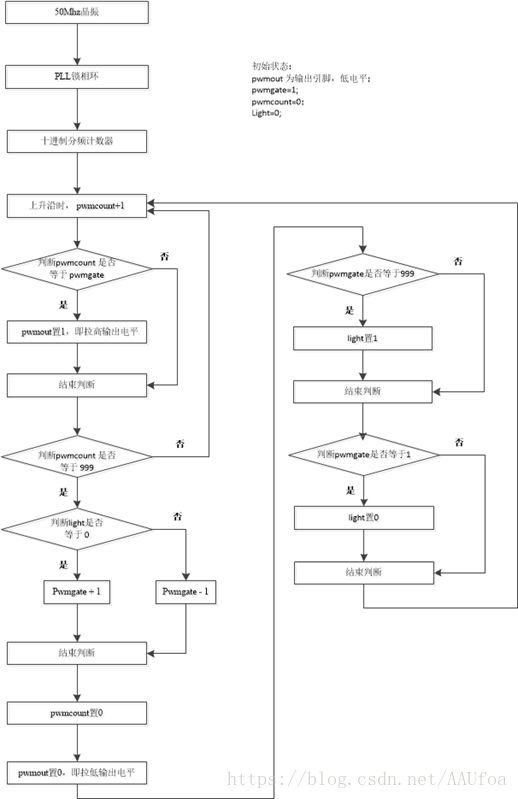

3.系统工作流程

50Mhz晶振通过PLL锁相环和十进制分频计数器后得到所需的1Mhz时钟信号,所有计数调制操作均以1Mhz时钟信号为基础[3]。

对上升沿进行计数,计满1000个上升沿,即经过1000个基本时钟周期(1ms)时,拉低输出电平,同时时计数值归0,使PWM调制后的输出波形频率为1Khz。每次计数后将计数值pwmcount与阈值pwmgate进行比较,若两者相等,拉高输出电平。当light=0,也就是处于一次完整呼吸的前半个过程时,在每次拉高输出电平后使阈值加1。当light=0,处于呼吸的后半个过程时,在每次拉高输出电平后使阈值减1。阈值的上下限分别为999和1,控制呼吸周期为2s。

图2 系统流程框图

4.模块代码

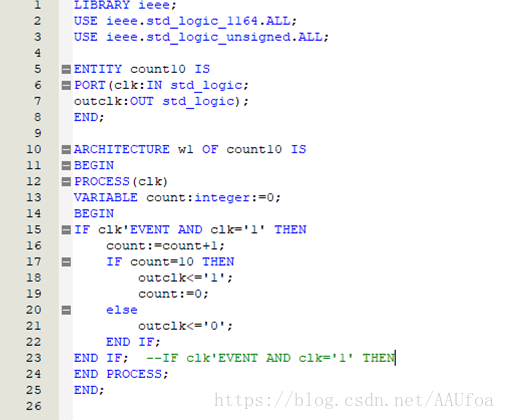

1.十分频计数器的VHDL实现

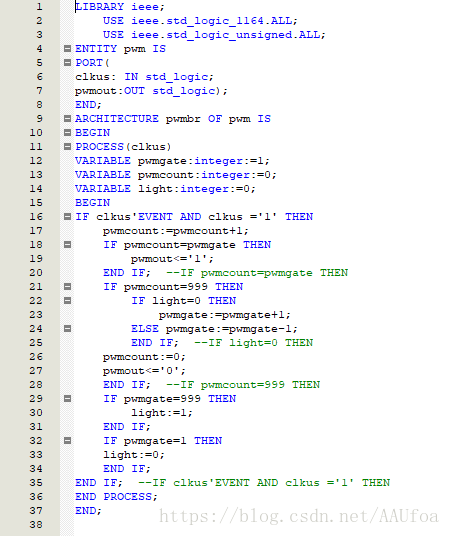

2.波形调制的VHDL实现

本文介绍了一种基于Altera Cyclone II EP2C35 FPGA平台的呼吸灯设计,通过锁相环、计数器生成可变占空比的PWM波形来控制LED亮度,实现2秒周期的呼吸效果。设计包括锁相环、计数器和PWM模块,详细阐述了系统原理和工作流程,并提供了相关VHDL代码实现。

本文介绍了一种基于Altera Cyclone II EP2C35 FPGA平台的呼吸灯设计,通过锁相环、计数器生成可变占空比的PWM波形来控制LED亮度,实现2秒周期的呼吸效果。设计包括锁相环、计数器和PWM模块,详细阐述了系统原理和工作流程,并提供了相关VHDL代码实现。

459

459