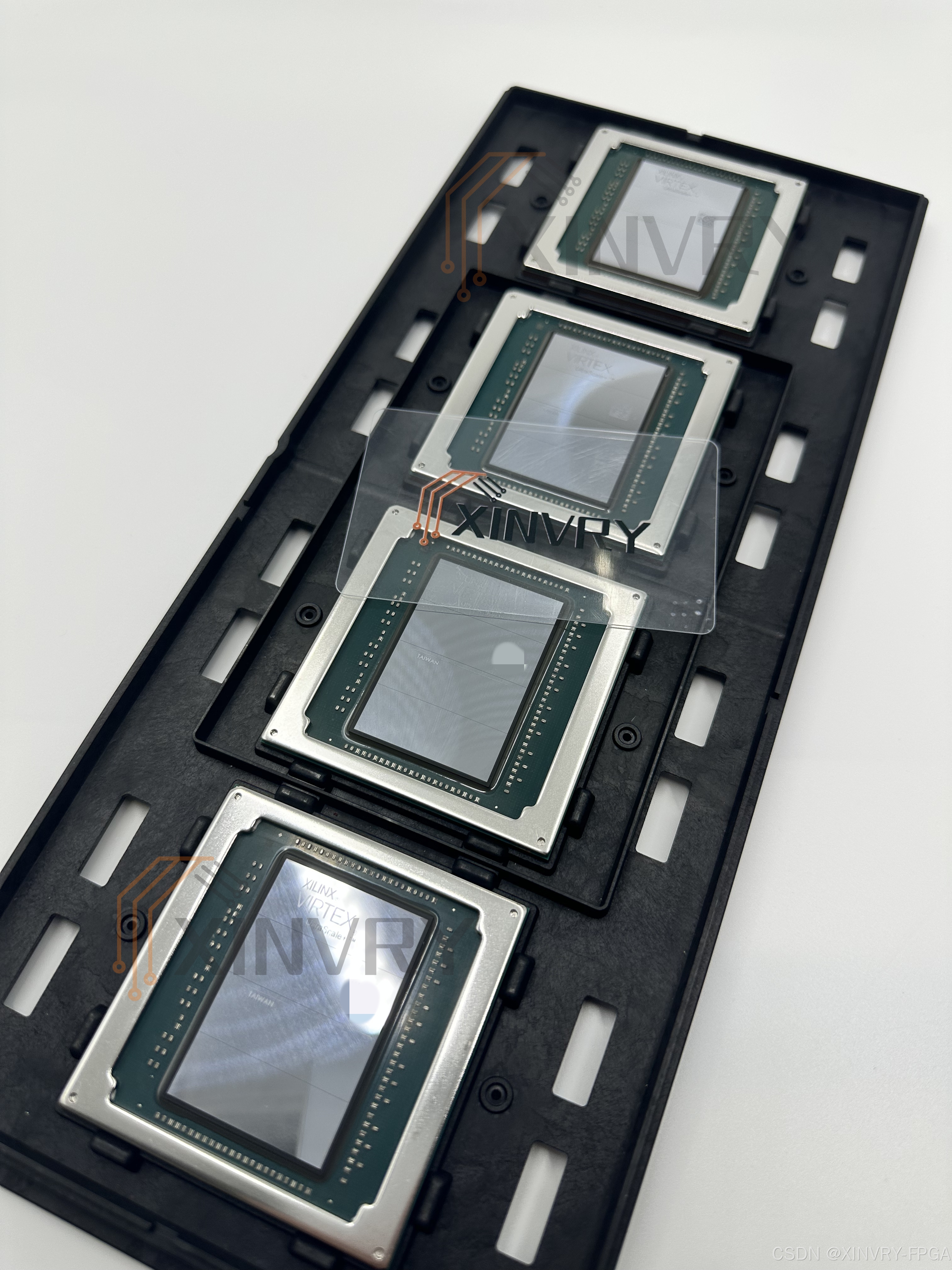

Xilinx 赛灵思 FPGA Virtex UltraScale+ VU19P

XCVU19P-2FSVA3824E

XCVU19P-2FSVB3824E

1. 核心规格与特性

逻辑资源

逻辑单元(LUTs):约 1,143,000 个

触发器(Flip-Flops):约 2,286,000 个

DSP Slices:约 6,840 个(支持高精度乘加运算)

Block RAM(BRAM):约 312.5 MB(约 25,620 Kb)

UltraRAM:约 540 Mb(大容量片上存储,适合数据缓冲)

工艺技术

制程:16nm FinFET+

功耗优化:支持动态电压频率调整(DVFS)和低功耗模式。

高速接口

收发器(Transceivers):

数量:24 个 GTY 收发器

速率:最高 32.75 Gbps(支持 PCIe Gen4、100G以太网、Interlaken等协议)

PCIe接口:集成 PCI Express Gen3 x16 或 Gen4 x8 硬核。

以太网支持:支持 10G/25G/100G 等高速网络协议。

时钟管理

时钟管理单元(CMT):支持多频率合成、抖动滤波。

全局时钟网络:低延迟、高扇出时钟分配。

封装与物理规格

封装型号:FSVA3824E

封装类型:Flip-Chip BGA(球栅阵列封装)

引脚数:3824 个

尺寸:45mm x 45mm(具体需参考官方文档)

散热:需配合散热片或主动冷却方案。

开发工具与生态

设计工具:Xilinx Vivado Design Suite(支持RTL综合、布局布线、调试)。

IP核支持:可调用DDR4/5、HBM、AI引擎等预验证IP。

生态系统:支持OpenCL、C/C++高层次综合(HLS),与第三方工具(如Matlab)集成。

关键优势

高密度与灵活性:适合快速迭代复杂算法。

低延迟互联:通过高速收发器和片上网络(NoC)优化数据流。

3774

3774

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?