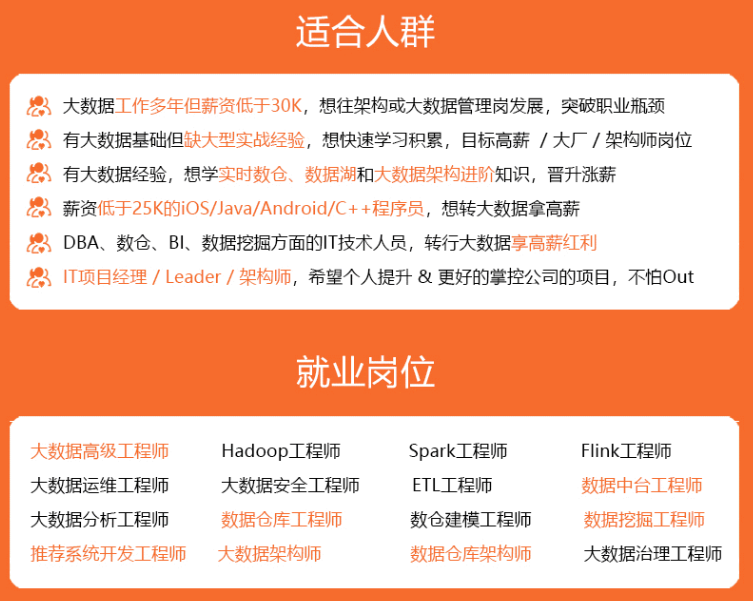

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

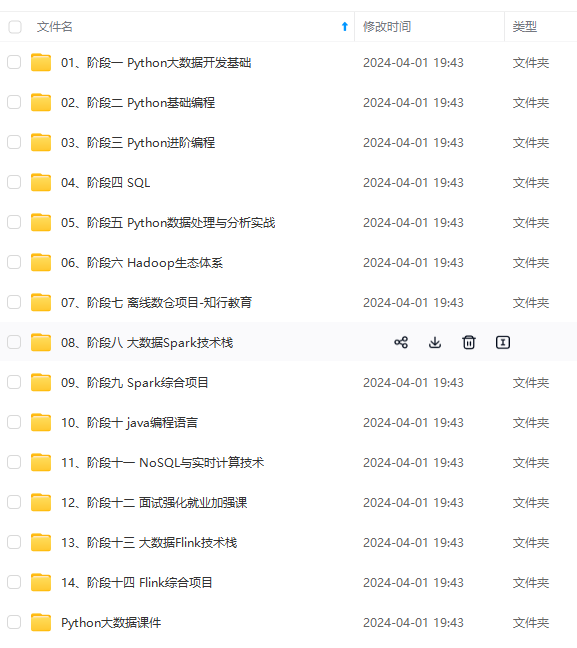

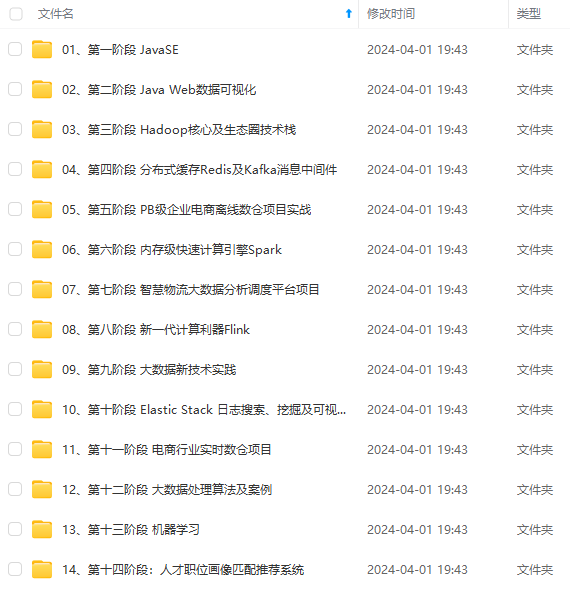

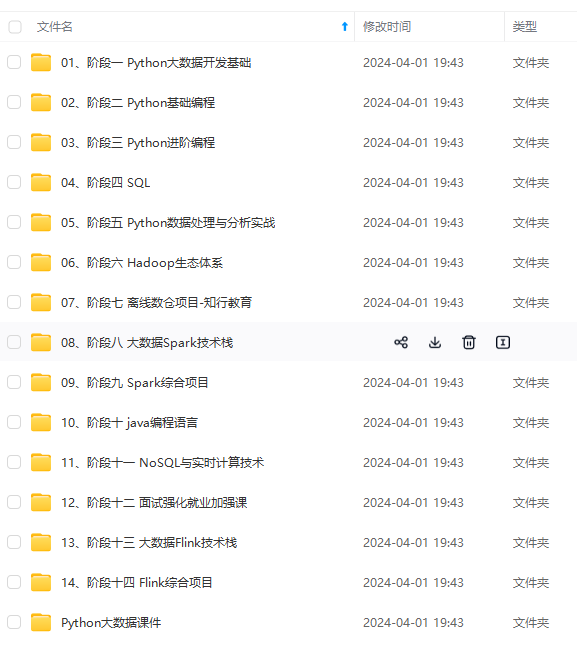

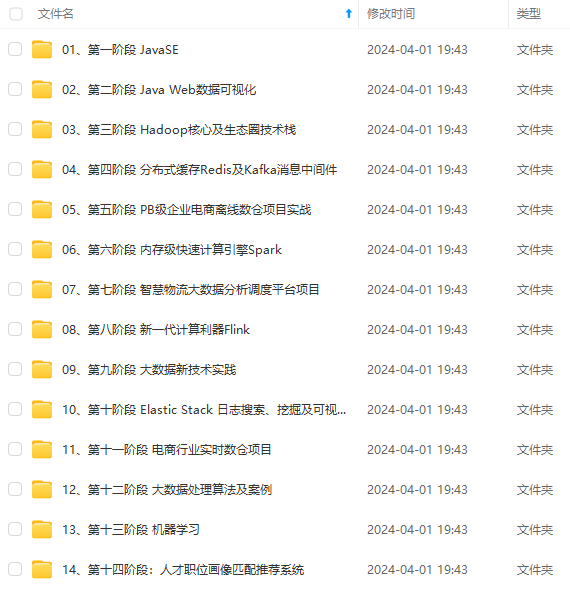

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

组合逻辑与时序逻辑

在搞清这两种赋值方式的区别之前,我们需要先弄明白数字电路的分类。

先看看百度百科怎么说:

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

不说人话?没关系,我来慢慢讲。

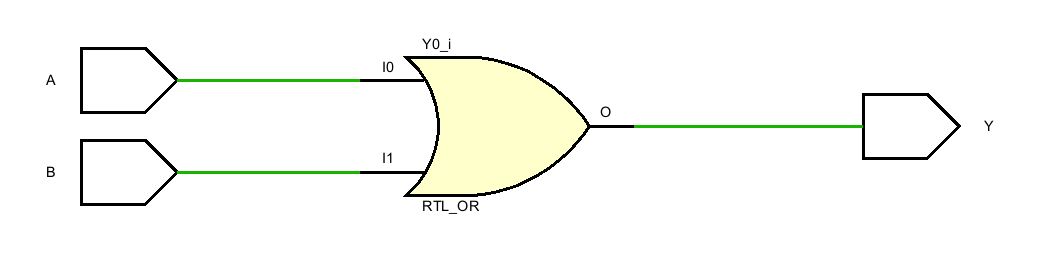

举个栗子,你现在想要实现一个功能:你有两个输入A和B,你想看看他们的或运算的结果Y是什么?也就是说Y = A | B。这很简单,一个2输入的或门就可以解决这一问题。

显然,这是组合逻辑的一种。同样的,与、非、异或等等这些逻辑运算也都是组合逻辑。可以看到,在组合逻辑中,是不需要时钟输入的。

有了这个或门后,我们希望每10ns改变一次A和B的值,再观察他们进行或操作的结果。假如在时刻0ns,AB的值为00,则输出结果为0;在时刻10ns,AB的值为11,则其输出结果为1。

但是现在问题来了,AB是两个不同的信号,它们到达或门的时间不一定一致。假如A信号年富力强,在8ns就到了或门,此时A值已经变为了1,而B信号年老力衰,此时仍没有到达或门,其值依旧为0。那么根据组合逻辑实时输出的特性,输出Y就会提前2ns从0变成1,但是,我们需要的是其在第一个10ns的期间保持0,而在第二个10ns保持1。这与我们的预期相违背!

这样我们就可以把目光转向时序逻辑了。在时序电路中,加入了一个时钟信号,有了这个时钟信号后,就可以只在时钟信号的上升沿或者下降沿对输入信号进行采样,而在其他时候则让它保持上一次的输出即可。

再举个例子:多人多足游戏大家应该都不陌生,在这个游戏里,我们通常会有节奏地喊口号:“一、二”、一、二,然后大家跟着这个节奏来同时迈动左腿或者右腿。

时序电路的时钟信号就如同这个节奏“一、二”一样,每当时钟的上升沿或者下降沿到来时,便会对电路的输入进行采样,然后根据逻辑关系进行对应的输出。而当时钟边沿没有到来的时候,则电路的输出保持在上一个状态不变。

为了实现这一特性,也会有一些小小的要求。

- 输入信号必须在时钟上升沿到来之前的一段时间内就保持稳定,因为在电路采样期间你输入信号不能左右横跳

- 同样的,在电路完成采样后的一段时间内,输入信号也必须保持稳定,也不能左右横跳影响下一个周期的信号采样

这两个时间就是触发器的建立时间和**保持时间,**触发器正常工作需要满足建立时间和保持时间的时序要求。

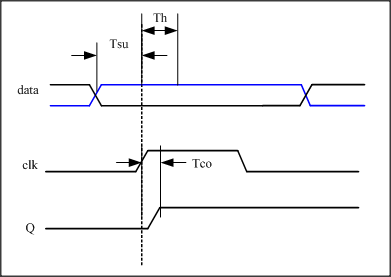

- 建立时间(Tsu:set up time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间

- 保持时间(Th:hold time):是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间

时序逻辑的核心就是触发器,触发器的输出不是瞬变的,而是需要一定的时间。这个参数就是触发器的**数据输出延时(Clock-to-Output Delay)----Tco,**这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。

比如在10ns处,时钟上升沿到来,此时触发器输入采样值为1。由于Tco的存在,这个值1可能要在11ns处才会出现在触发器的输出端。了解这一点很重要,是后面搞懂非阻塞赋值与阻塞赋值区别的前提条件。

赋值区别

首先直接上结论:

- 时序逻辑电路用非阻塞赋值(<=)

- 组合逻辑电路用阻塞赋值(=)

阻塞赋值就是直接连线,其映射到具体电路,就是指定一个具体导向的wire,即线网;而非阻塞赋值就是触发器,映射到具体电路就是一个reg。根本就不需要管这两个赋值的名字,只要想想你到底要实现一个什么电路就行了。

下面是阻塞赋值的例子:

module test(

input clk,

input [1:0]din,

output reg [1:0]a,

output reg [1:0]b

);

always @(*)begin

a = din;

b = a;

end

endmodule

看到这里,你可能会想阻塞赋值是顺序执行的,也就是先执行这一句: a = din;然后才是: b = a。所以会把din的值赋给a,然后再把a的值赋给b。就好像第一句的结果会影响第二句的赋值一样,所以被称为阻塞赋值。

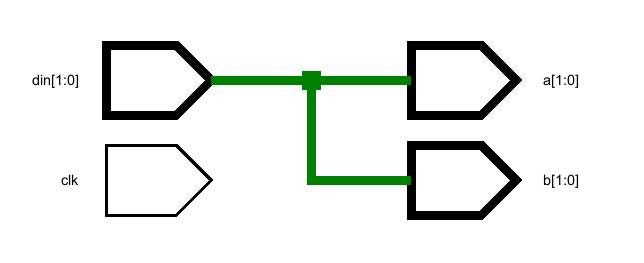

这个道理是没问题的,但是看起来非常的绕。如果把这个module直接映射到电路,你会发现这三个变量,根本就是三条总线互相连到了一起,如下:

所以其结果就是,当输入din发生变化时,会立马同步到输出a、b。可以写一个简单的testbench验证一下:

`timescale 1ns/1ns

module test_tb();

reg clk;

reg [1:0]din;

wire [1:0]a,b;

initial begin

din = 0;

clk = 0;

end

always #({$random}%100) din = {$random}%4; //随机赋值0~3

always #10 clk = ~clk;

test tb(

.clk(clk),

.din(din),

.a(a),

.b(b)

);

endmodule

可以看到,输入、输出的变化是实时同步的,这也是组合逻辑的特点。

- 162ns:din=1;a=1;b=1;

- 170ns:din=1;a=1;b=1;

- 190ns:din=2;a=2;b=2;

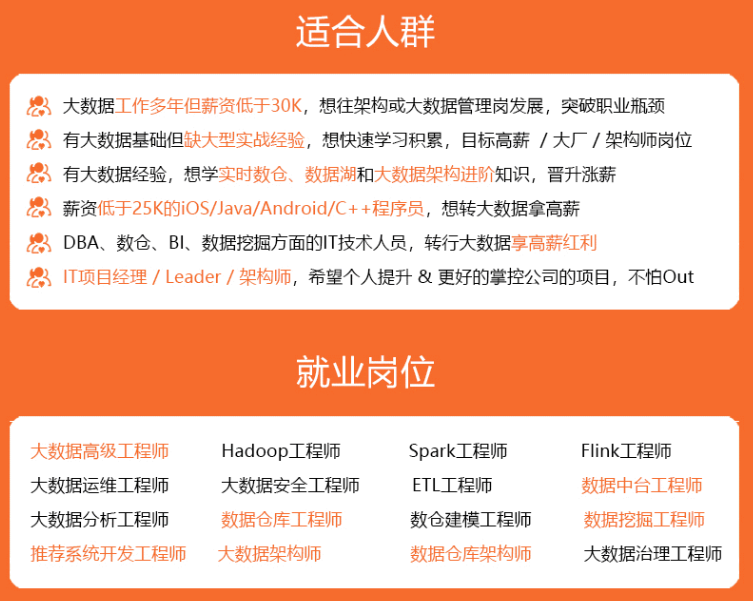

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

习提升的进阶课程,涵盖了95%以上大数据知识点,真正体系化!**

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?