目的:测试ISE生成的NGC在labview中使用;

测试功能:带IO的NGC;

硬件平台:黑金AX545.

软件代码包括verilog代码和ucf约束文件。

代码如下:

//===========================================================================

// Module name: led_test.v

// 描述: 每隔1秒依次点亮开发板上的LED0~LED4

//===========================================================================

`timescale 1ns / 1ps

module led_test (

clk, // 开发板上输入时钟: 50Mhz

rst_n, // 开发板上输入复位按键

led // 输出LED灯,用于控制开发板上四个LED(LED1~LED4)

);

//===========================================================================

// PORT declarations

//===========================================================================

input clk;

input rst_n;

output [3:0] led;

//寄存器定义

reg [31:0] timer;

reg [3:0] led;

//===========================================================================

// 计数器计数:循环计数0~4秒

//===========================================================================

always @(posedge clk or negedge rst_n) //检测时钟的上升沿和复位的下降沿

begin

if (~rst_n) //复位信号低有效

timer <= 0; //计数器清零

else if (timer == 32'd199_999_999) //开发板使用的晶振为50MHz,4秒计数(50M*4-1=199_999_999)

timer <= 0; //计数器计到4秒,计数器清零

else

timer <= timer + 1'b1; //计数器加1

end

//===========================================================================

// LED灯控制

//===========================================================================

always @(posedge clk or negedge rst_n) //检测时钟的上升沿和复位的下降沿

begin

if (~rst_n) //复位信号低有效

led <= 4'b1111; //LED灯输出全为高,四个LED灯灭

else if (timer == 32'd49_999_999) //计数器计到1秒,

led <= 4'b1110; //LED1点亮

else if (timer == 32'd99_999_999) //计数器计到2秒,

led <= 4'b1101; //LED2点亮

else if (timer == 32'd149_999_999) //计数器计到3秒,

led <= 4'b1011; //LED3点亮

else if (timer == 32'd199_999_999) //计数器计到4秒,

led <= 4'b0111; //LED4点亮

end

endmodule

ucf约束文件代码如下:

##

NET clk LOC = V10 | TNM_NET = sys_clk_pin | IOSTANDARD = "LVCMOS33";

TIMESPEC TS_sys_clk_pin = PERIOD sys_clk_pin 50000 kHz;

##

##

NET rst_n LOC = N4 | IOSTANDARD = "LVCMOS15"; ## SW2 pushbutton

##

########LED Pin define#####################

NET led<0> LOC = V5 | IOSTANDARD = "LVCMOS33"; ## LED1

NET led<1> LOC = R3 | IOSTANDARD = "LVCMOS33"; ## LED2

NET led<2> LOC = T3 | IOSTANDARD = "LVCMOS33"; ## LED3

NET led<3> LOC = T4 | IOSTANDARD = "LVCMOS33"; ## LED4

综合实现后,生成的bit文件和mcs文件下载到板子中,程序按照1s的间隔时间循环点亮4个led灯。

NGC文件操作如下:

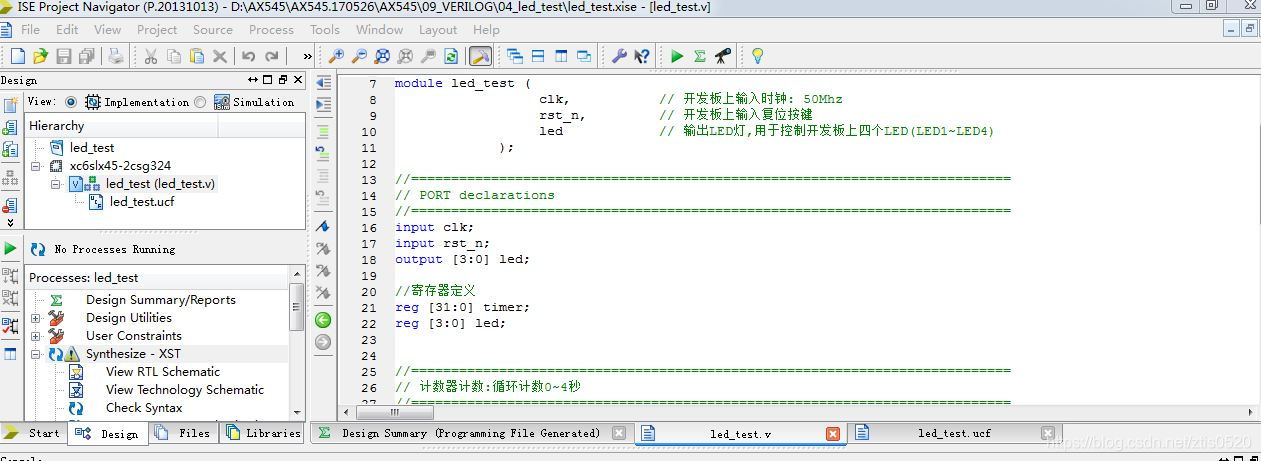

1、工程文件见下图。

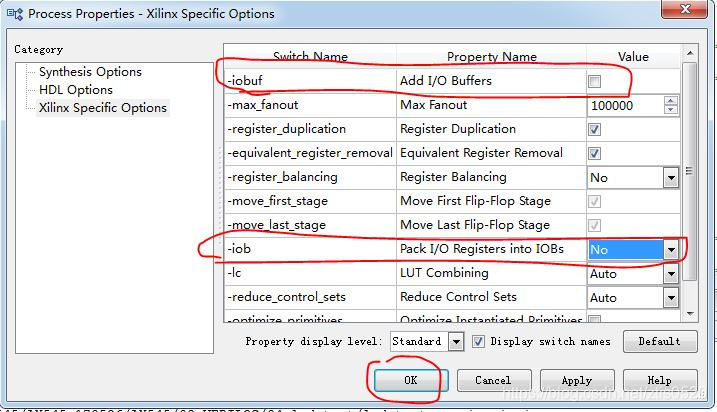

2、右键Synthesize-XST,选择Process Properties进行设置。

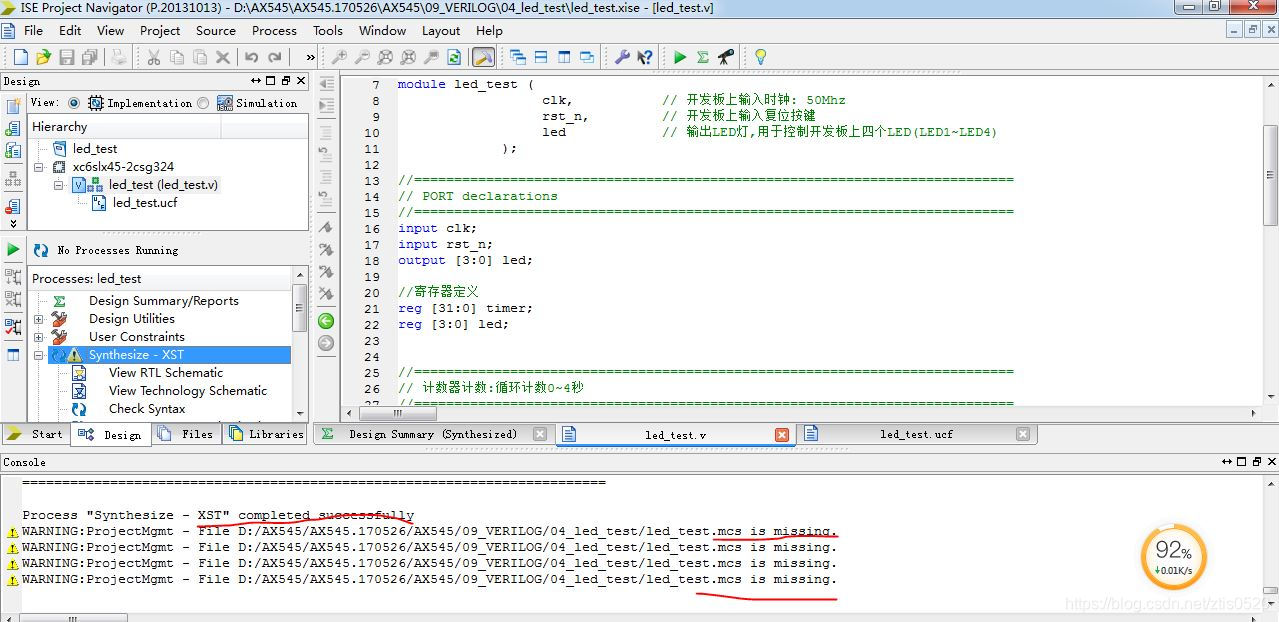

3、运行Synthesize-XST

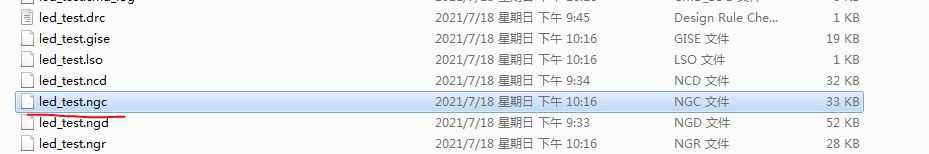

4.在工程文件夹下可以找到生成的<design_name>.ngc文件,此处<design_name>是所编译的.v文件名。

5、将led_test.ngc导入labview FPGA中的IP节点中,编译通过,但是运行无反应。标明ngc在IP节点中不能直接访问IO引脚。

使用CLIP方法进行测试:

1、使用VHDL语言重新对ngc文件进行封装,目的方便labview 调用。

该博客介绍了如何在LabVIEW FPGA环境中测试由ISE生成的Verilog代码,该代码控制一个带有IO的NGC,使得LED灯每隔1秒依次点亮。测试平台为黑金AX545,代码包括Verilog模块和UCF约束文件。然而,当直接在LabVIEW IP节点中使用NGC文件时,无法直接访问IO引脚,需要通过VHDL封装解决此问题。

该博客介绍了如何在LabVIEW FPGA环境中测试由ISE生成的Verilog代码,该代码控制一个带有IO的NGC,使得LED灯每隔1秒依次点亮。测试平台为黑金AX545,代码包括Verilog模块和UCF约束文件。然而,当直接在LabVIEW IP节点中使用NGC文件时,无法直接访问IO引脚,需要通过VHDL封装解决此问题。

722

722

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?