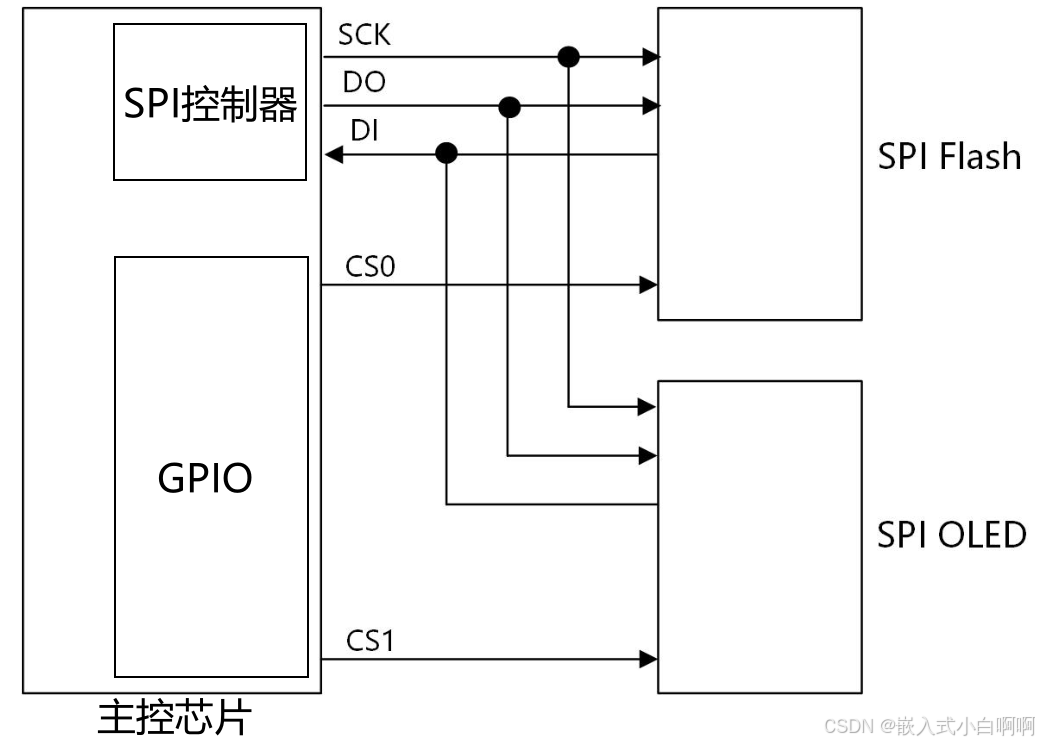

一、SPI硬件连接框图

SPI硬件连接框图如下:

1.1 引脚说明

- SCK:Serial Clock,时钟引脚

- DO(MOSI):Master Output, Slave Input,SPI主控发出数据,SPI从设备接收数据

- DI(MISO):Master Input, Slave Output,SPI主控接收数据,SPI从设备发出数据

- CS:Chip Select,片选引脚

1.2 连接说明

SPI属于主从结构。其中,SPI控制器代表主设备,一个SPI控制器上可以外接多个SPI从设备,例如可以外接 SPI Flash 、SPI OLED 等等。那么主设备如何和其中的某个从设备进行通信呢?通过片选引脚拉低(或者拉高)来选中想要通信的从设备,同一时刻只能有一个从设备被选中进行通信。

二、SPI协议

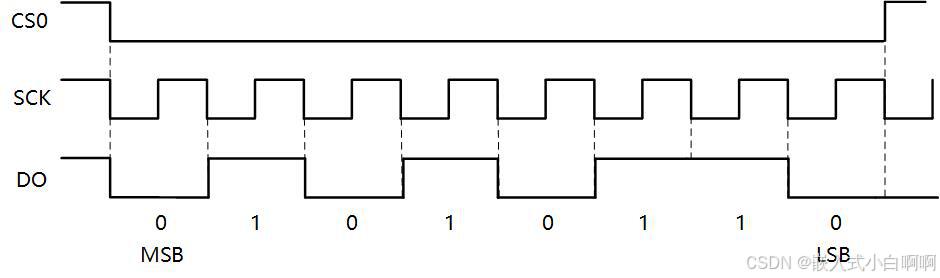

2.1 SPI传输示例

SPI协议是怎么传输数据的呢?下面以主控芯片传输一个字节数据0x56给SPI Flash为例进行说明。时序图如下:

- 首先,CS0 片选引脚拉低选中SPI Flash设备。

- 0x56 的二进制就是0b0101 0110,因此在每个SCK时钟周期,DO输出对应的电平,先传输的是最高位。

- SPI Flash会在每个时钟周期的上升沿读取D0上的电平。

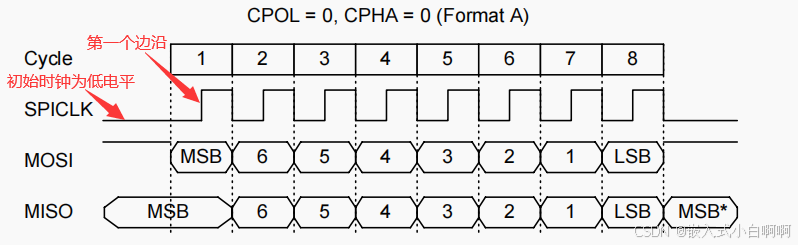

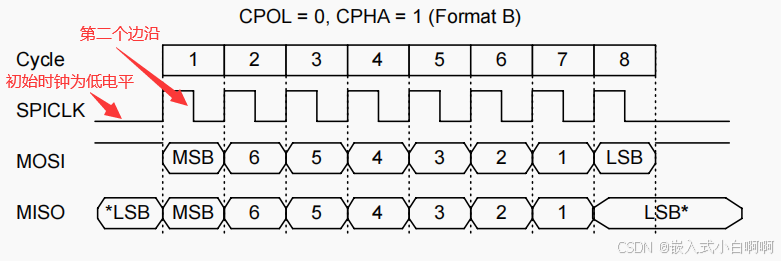

2.2 SPI工作模式

对于SPI传输示例时序图中,有两个地方是可以设置的:

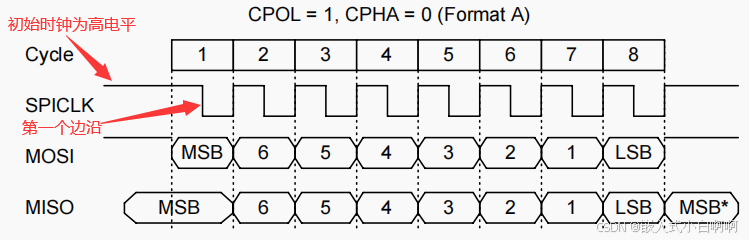

(1)SCK起始位置的电平可以设置为高电平或者低电平,这个用CPOL来表示,CPOL等于0为低电平,等于1为高电平。

(2)在时钟的第一个还是第二跳变沿进行数据采样,这个用CPHA来表示,CPHA等于0为第一个时钟跳变沿,等于1为第二个时钟跳变沿。

根据 CPOL 和 CPHA 的值,可以组成SPI的4种工作模式:

| CPOL | CPHA | 模式 | 含义 |

|---|---|---|---|

| 0 | 0 | 0 | SPI CLK初始电平为低电平,在第一个时钟沿采样数据 |

| 0 | 1 | 1 | SPI CLK初始电平为低电平,在第二个时钟沿采样数据 |

| 1 | 0 | 2 | SPI CLK初始电平为高电平,在第一个时钟沿采样数据 |

| 1 | 1 | 3 | SPI CLK初始电平为高电平,在第二个时钟沿采样数据 |

4钟模式的时序图如下:

- 模式0时序图

- 模式1时序图

- 模式2时序图

- 模式3时序图

注意:根据这4种模式的时序图可以知道,无论是哪种模式,主控芯片在 MOSI 发出8位数据的同时,MISO 也会接收8位数据。

三、总结

本文简要介绍了SPI协议,根据 CPOL 和 CPHA 的值,可以组成4中不同工作模式。

3658

3658

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?