关于按键的特性可以参照下文

按键消抖指南

下面分享两个从网上找到的消抖例子:

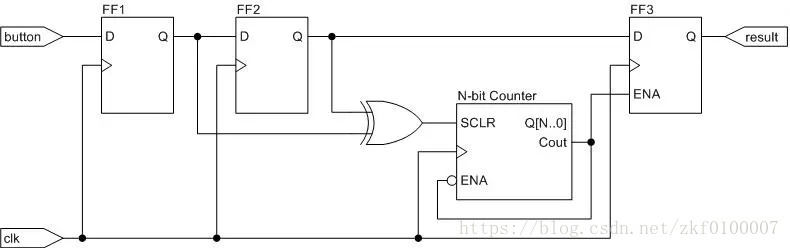

例子1:

代码如下:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENTITY debounce IS

GENERIC(

counter_size : INTEGER := 19); --counter size (19 bits gives 10.5ms with 50MHz clock)

PORT(

clk : IN STD_LOGIC; --input clock

button : IN STD_LOGIC; --input signal to be debounced

result : OUT STD_LOGIC); --debounced signal

END debounce;

ARCHITECTURE logic OF debounce IS

SIGNAL flipflops : STD_LOGIC_VECTOR(1 DOWNTO 0); --input flip flops

SIGNAL counter_set : STD_LOGIC; --sync reset to zero

SIGNAL counter_out : STD_LOGIC_VECTOR(counter_size DOWNTO 0) := (OTHERS => '0'); --counter output

BEGIN

counter_set <= flipflops(0) xor flipflops(1); --determine when to start/reset counter

PROCESS(clk)

BEGIN

IF(clk'EVENT and clk = '1') THEN

flipflops(0) <= button;

flipflops(1) <= flipflops(0);

If(counter_set = '1') THEN --reset counter because input is changing

counter_out <= (OTHERS => '0');

ELSIF(counter_out(counter_size) = '0') THEN --stable input time is not yet met

counter_out <= counter_out + 1;

ELSE --stable input time is met

result <= flipflops(1);

END IF;

END IF;

END PROCESS;

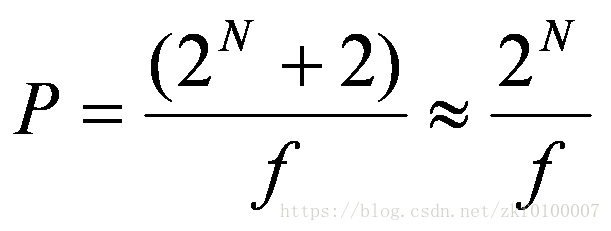

END logic;其中的计数器长度由如下公式确定:

2是表示两级同步DFF的延迟,一般可以忽略, (2^19+2) / 50,000,000 = 10.49ms.

例子2

代码如下:

module PushButton_Debouncer(

input clk,

input PB, // "PB" is the glitchy, asynchronous to clk, active low push-button signal

// from which we make three outputs, all synchronous to the clock

output reg PB_state, // 1 as long as the push-button is active (down)

output PB_down, // 1 for one clock cycle when the push-button goes down (i.e. just pushed)

output PB_up // 1 for one clock cycle when the push-button goes up (i.e. just released)

);

// First use two flip-flops to synchronize the PB signal the "clk" clock domain

reg PB_sync_0; always @(posedge clk) PB_sync_0 <= ~PB; // invert PB to make PB_sync_0 active high

reg PB_sync_1; always @(posedge clk) PB_sync_1 <= PB_sync_0;

// Next declare a 16-bits counter

reg [15:0] PB_cnt;

// When the push-button is pushed or released, we increment the counter

// The counter has to be maxed out before we decide that the push-button state has changed

wire PB_idle = (PB_state==PB_sync_1);

wire PB_cnt_max = &PB_cnt; // true when all bits of PB_cnt are 1's

always @(posedge clk)

if(PB_idle)

PB_cnt <= 0; // nothing's going on

else

begin

PB_cnt <= PB_cnt + 16'd1; // something's going on, increment the counter

if(PB_cnt_max) PB_state <= ~PB_state; // if the counter is maxed out, PB changed!

end

assign PB_down = ~PB_idle & PB_cnt_max & ~PB_state;

assign PB_up = ~PB_idle & PB_cnt_max & PB_state;

endmodule

864

864

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?