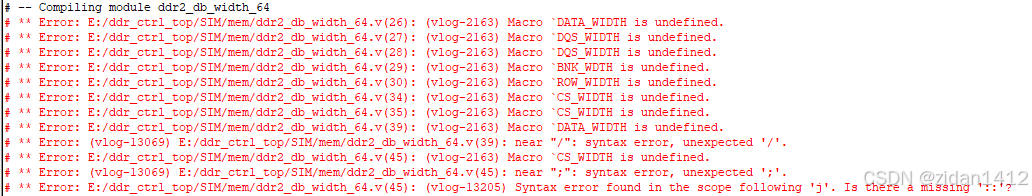

一、DDR2.v中的参数未加载

Error:: (vlog-2730) Undefined variable: 'BA_BITS'.

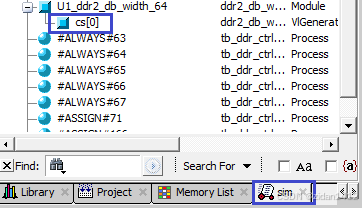

解决办法:在ddr2_db_width_64.v和ddr2.v中加入参数文件。

PS:此处用的是相对路径。将tb_config_params.v和ddr_sdram_mem_params.v两个参数文件放到ddr2_db_width_64.v和ddr2.v文件同一级目录下。

由于tb_config_params.v调用了ddr_sdram_mem_params.v的参数,所以ddr_sdram_mem_params.v必须在tb_config_params.v的前面调用。

`timescale 1 ps / 1 ps

`include"ddr_sdram_mem_params.v" //add this ,note the path

`include"tb_config_params.v" //add this ,note the path

//must in this order

module ddr2_db_width_64 (

ddr_dq,

ddr_dqs,

ddr_dqs_n,

ddr_ba,

ddr_ad,

ddr_clk,

ddr_clk_n,

ddr_cke,

ddr_cs_n,

ddr_odt,

ddr_ras_n,

ddr_cas_n,

ddr_we_n,

ddr_dqm

);

module ddr2 (

ck,

ck_n,

cke,

cs_n,

ras_n,

cas_n,

we_n,

dm_rdqs,

ba,

addr,

dq,

dqs,

dqs_n,

rdqs_n,

odt

);

`include"tb_config_params.v" //add this ,note the path

`include"ddr_sdram_mem_params.v" //add this ,note the path

`include "ddr2_parameters.vh"

// text macros

`define DQ_PER_DQS DQ_BITS/DQS_BITS

`define BANKS (1<<BA_BITS)

`define MAX_BITS (BA_BITS+ROW_BITS+COL_BITS-BL_BITS)

`define MAX_SIZE (1<<(BA_BITS+ROW_BITS+COL_BITS-BL_BITS))

`define MEM_SIZE (1<<MEM_BITS)

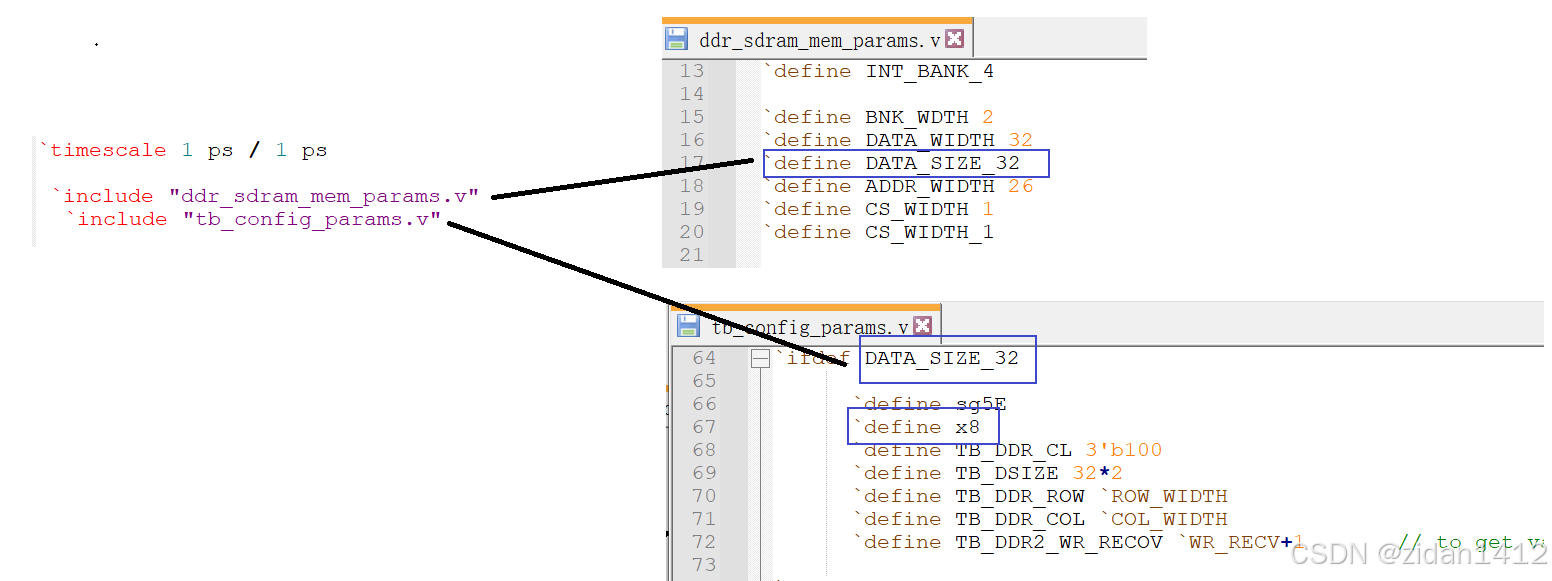

`define MAX_PIPE 2*(AL_MAX + CL_MAX)二、ddr2_parameters.vh 语法异常

** Error (suppressible):(vlog-13388) A macro defintion has been found on the same line as a conditional compilation directive.

** Error (suppressible): (vlog-2902) A `define was found on the same line as a SystemVerilog `ifdef, `ifndef, `elsif, or `else.

解决办法:在ddr2_parameters.vh中将`else `define 中的`define 换到下一行去

`ifdef sg187E

`else `ifdef sg25E

`else `ifdef sg25

`else `ifdef sg3E

`else `ifdef sg3

`else `ifdef sg37E

//`else `define sg5E //wrong code

`else

`define sg5E //right code

`endif `endif `endif `endif `endif `endif

`ifdef x4

`else `ifdef x8

`else `ifdef x16

//`else `define x32 //wrong code

`else

`define x32 //right code

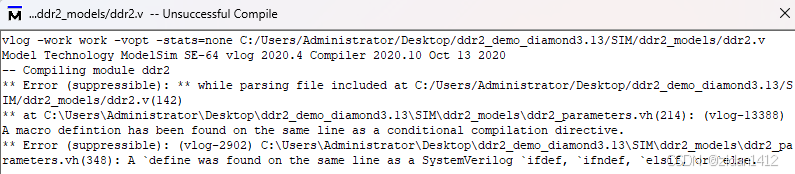

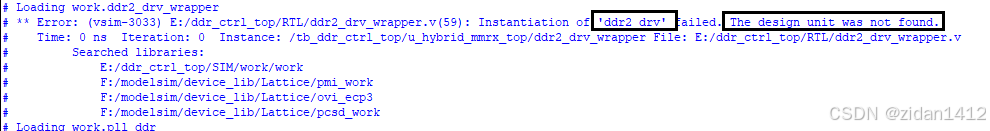

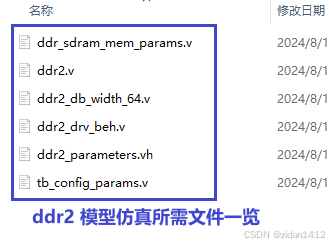

`endif `endif `endif三、DDR2 IP核模型behavior未调用

解决办法:手动将ddr2_drv_beh.v加载进modelsim仿真工程,注意ddr2_drv_beh.v也需要加入参数文件。

PS: ddr2_drv_beh.v在ddr2 IP核生成的文件夹中,名称和自定义的IP核命名有关,此处DDR2 IP核命名为ddr2_drv,所以 产生的对应文件为ddr2_drv_beh.v

`include "ddr_sdram_mem_params.v" //add this file

`timescale 1 ns / 100 ps

module ddr_sdram_mem_core ( //ddr2_drv_beh.v is for ddr2 IP simulation

clk,

rst_n,

fb_cmd,

fb_addr,

fb_cmd_valid,

`ifdef BRST_CNT_EN

fb_burst_length,

`endif

fb_init_start,

fb_write_data,

fb_data_mask,

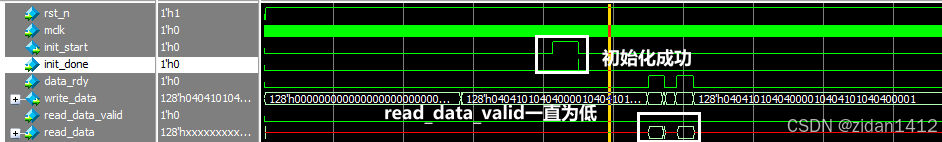

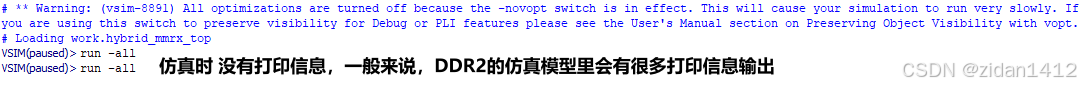

cas_latency,四、read_data_valid一直为低,且仿真无打印信息

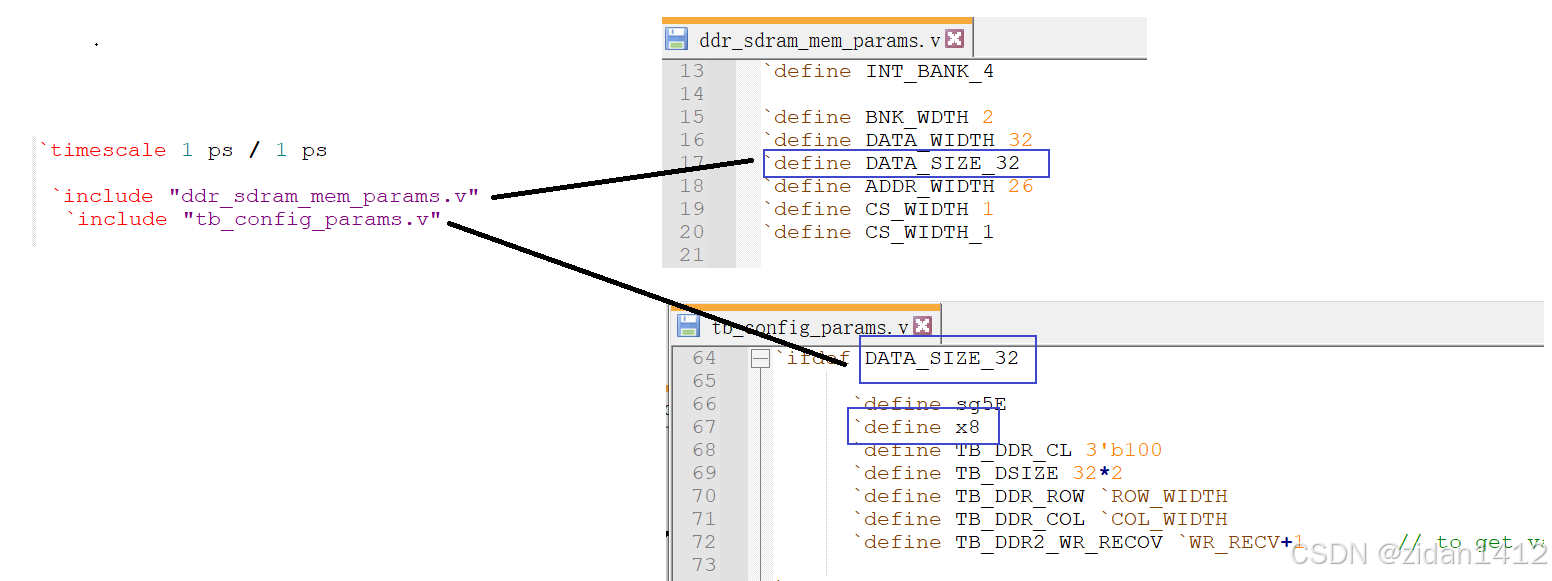

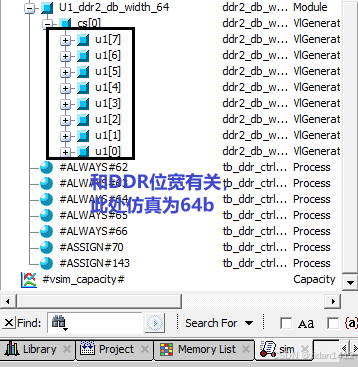

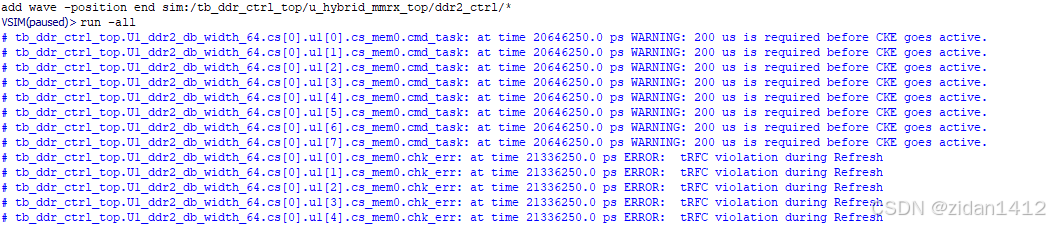

此时modelsim显示的信息如上图所示,结合调用的ddr2_db_width_64.v中调用的ddr2.v模型

只有cs[0],怀疑是ddr2.v还存在异常。

通过排查,在ddr2_db_width_64.v文件中,必须先调用ddr_sdram_mem_params.v后在调用tb_config_params.v ,修改后重新仿真即可。

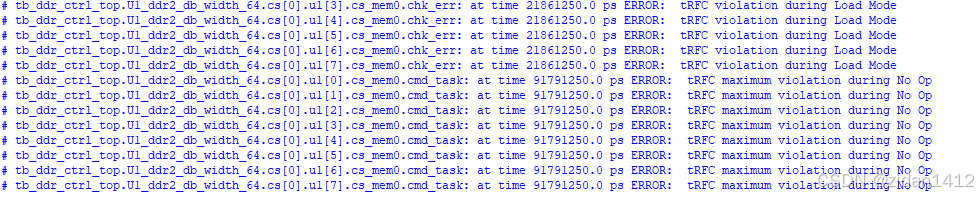

五、打印信息报错

ERROR: tRFC maximum violation during No Op

ERROR: tRFC violation during Load Mode

2601

2601

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?