一、 新建工程并导入verilog文件

1)新建工程

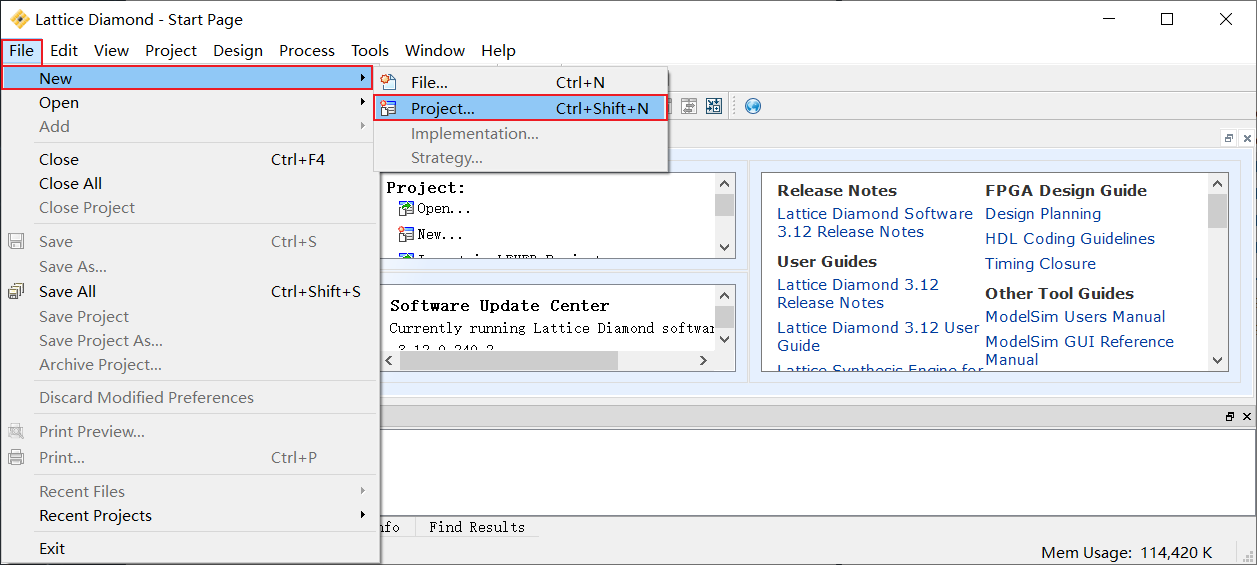

选择File →New →Project →Next

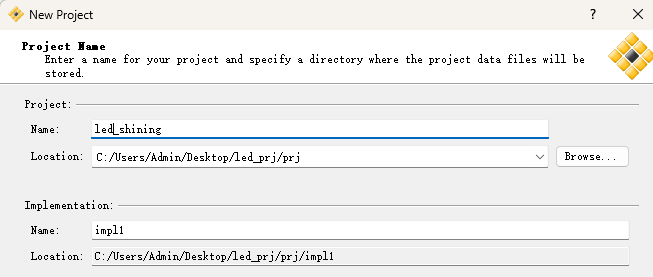

2)工程命名

我们将新工程命名为LEDshining,工程目录G:/LEDshining,然后点击Next

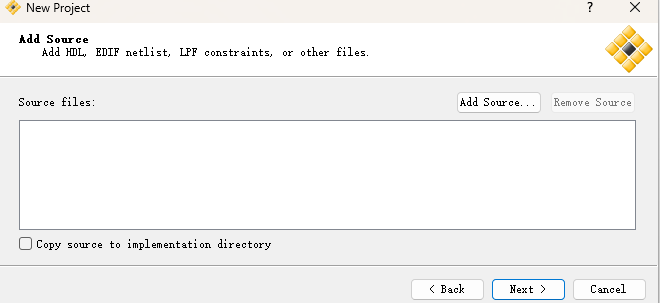

3)添加相关设计文件或约束文件

如果已经有设计文件和约束文件,我们可以选择添加进工程,

此处我们新建工程,没有相关文件,不需添加,直接Next

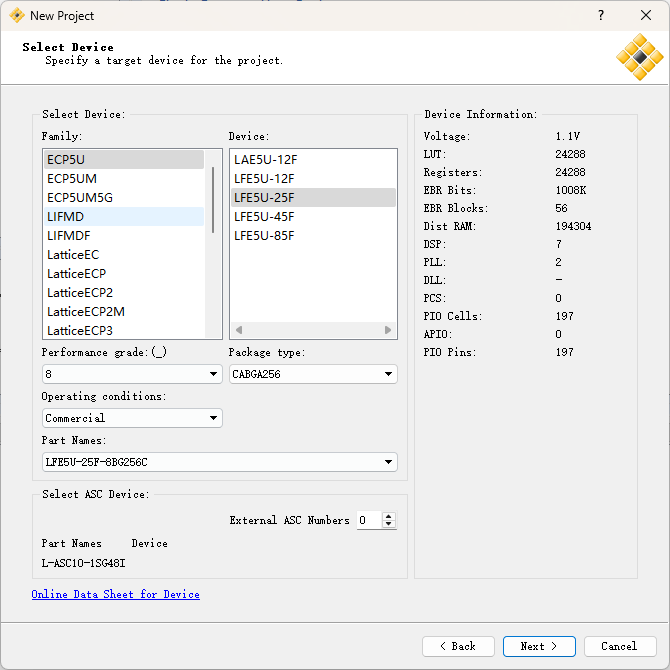

4)选择器件

按照Step FPGA开发板器件ECP5U-LFE5U-25F-CABGA256配置,Next(器件型号必须确认正确,否则在管脚设置时会报错)

5)选择综合工具

Synplify Pro(第三方)和Lattice LSE(原厂)都可以,我个人习惯使用Synplify Pro,

此处为了展示代码生成的网表,则选择Lattice LSE

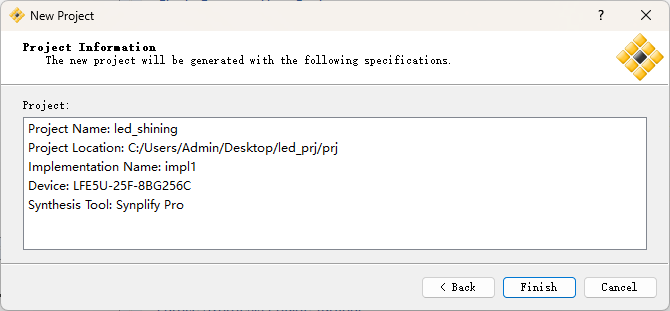

6)确认工程信息

上面选择的所有信息都在这里,确认没有问题,直接Finish

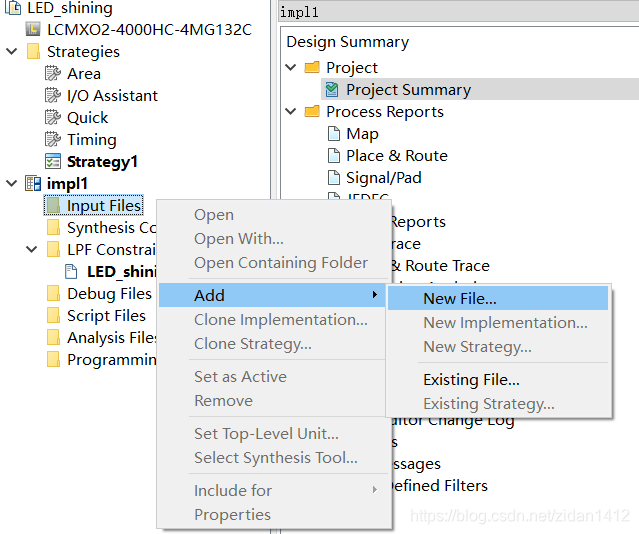

7)新建verilog设计文件

在input files文件夹点击鼠标右键→Add →New File

选择Verilog Files(选择自己使用的硬件描述语言),Name填写LED_shining,然后点击New,这样我们就创建了一个新的设计文件LED_shining.v,然后我们就可以在设计文件中进行编程了

8)准备代码

module led_shining

(

input clk_in ,

input rst_n_in ,

output led1 ,

output led2

);

parameter CLK_DIV_PERIOD= 12_000_000;

reg clk_div=0;

assign led1= clk_div;

assign led2= ~clk_div;

reg [ 23: 0] cnt=0;

always@(posedge clk_in or negedge rst_n_in)

begin

if(!rst_n_in)

begin

cnt<=0;

clk_div<=0;

end

else

begin

if(cnt==(CLK_DIV_PERIOD-1))

cnt<=0;

else

cnt<=cnt+1'b1;

if(cnt<(CLK_DIV_PERIOD>>1))

clk_div<=0;

else

clk_div<=1;

end

end

endmodule二、设计综合

1)综合编译

程序编写完成,需要综合,在软件左侧Process栏,选择Process,双击Synthesis Design,对设计进行综合,综合完成后Synthesis Design显示绿色对勾(如果显示红色叉号,说明代码有问题,根据提示修改代码),如图

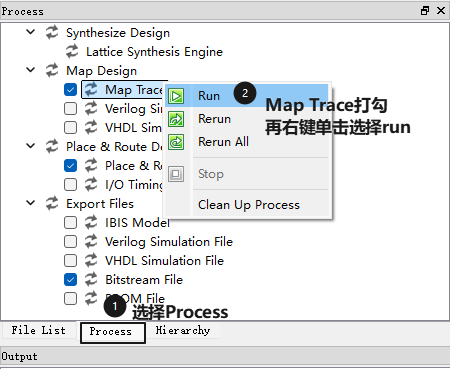

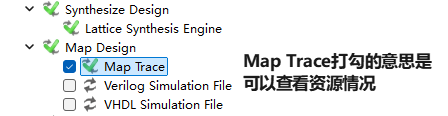

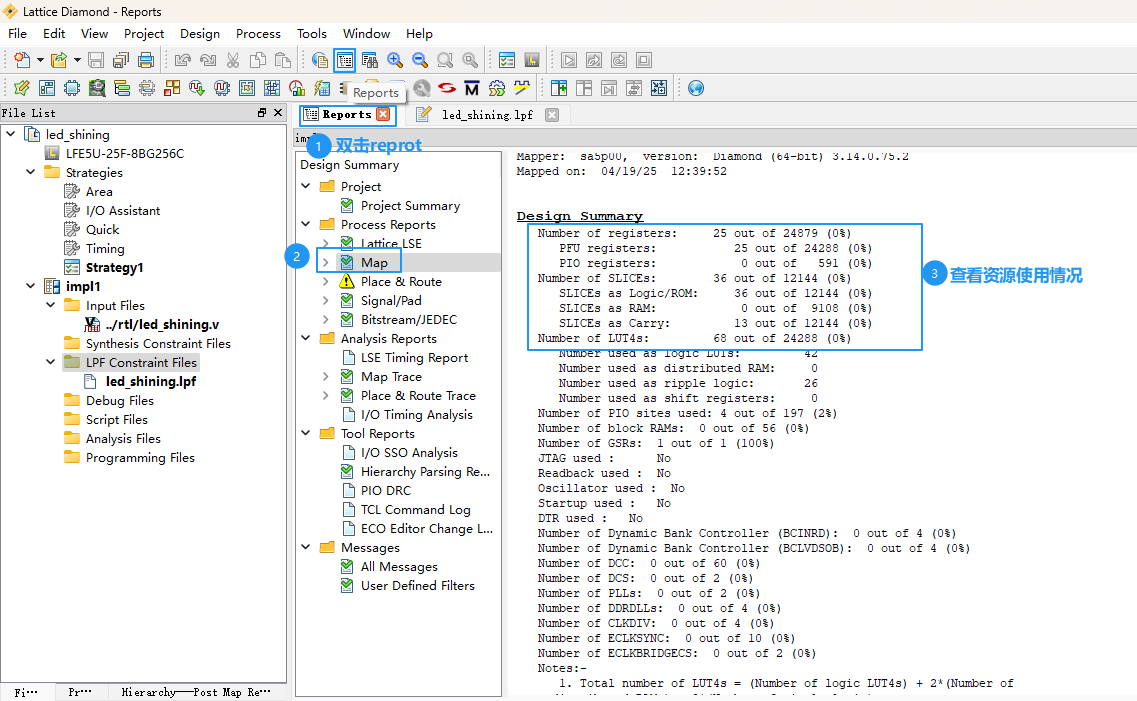

2)查看资源使用情况

3)查看网表

通过综合工具,我们的代码就被综合成了电路,生成的具体电路,我们可以通过选择Tools → Netlist Analyzer查看(仅限Lattice的LSE综合工具,第三方综合工具无法查看),如图

4)分配管脚

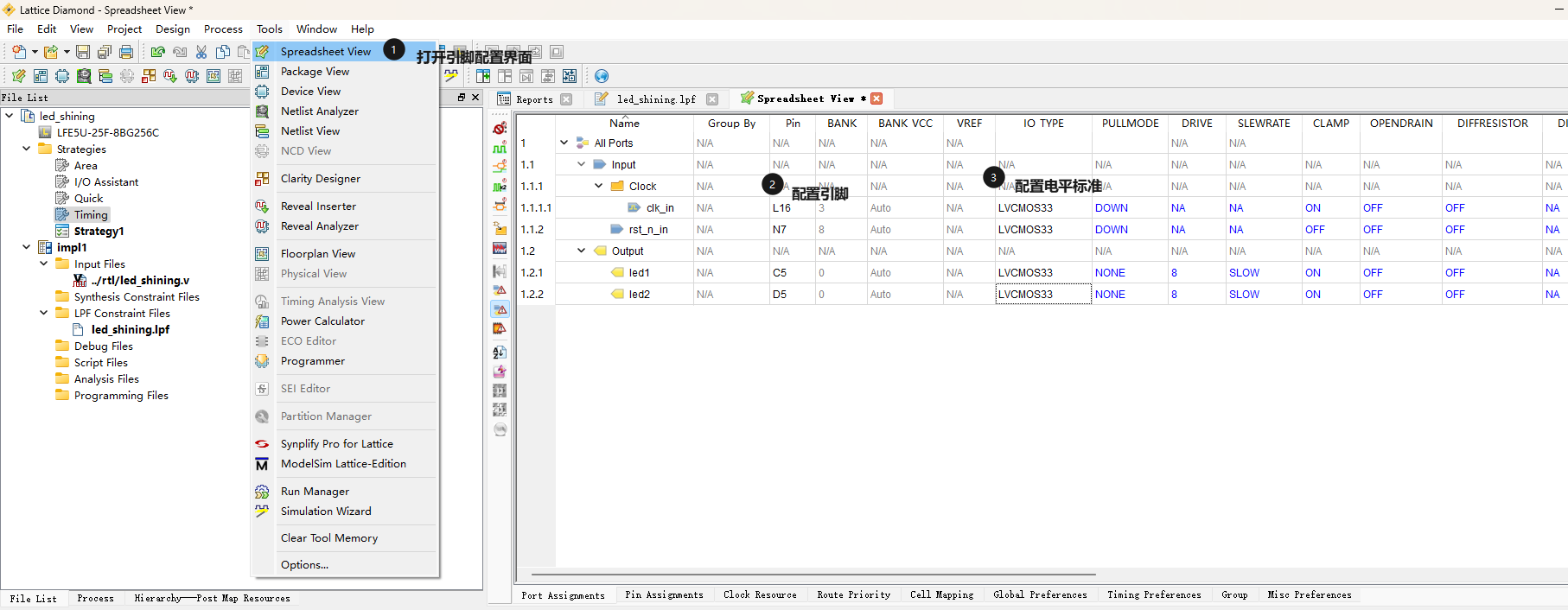

选择Tools → Spreadsheet View,按照下图分配FPGA管脚,然后设置IO_TYPE为LVCMOS33,保存,界面如下

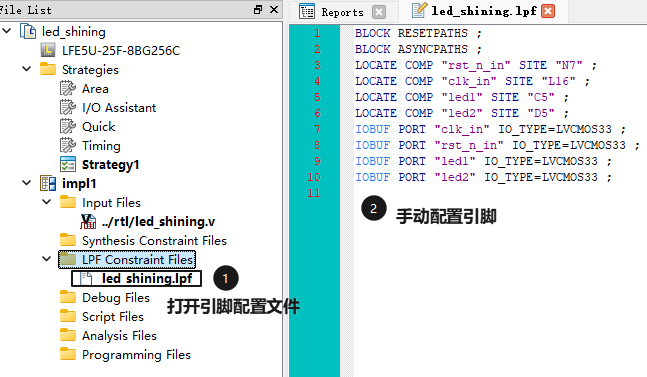

5)查看LPF管脚配置文件

Spreadsheet View配置保存信息会写入到lpf文件,查看lpf文件即可知是否引脚是否配置好

当然,后续如果想重新配置引脚,可以直接到lpf文件中修改。

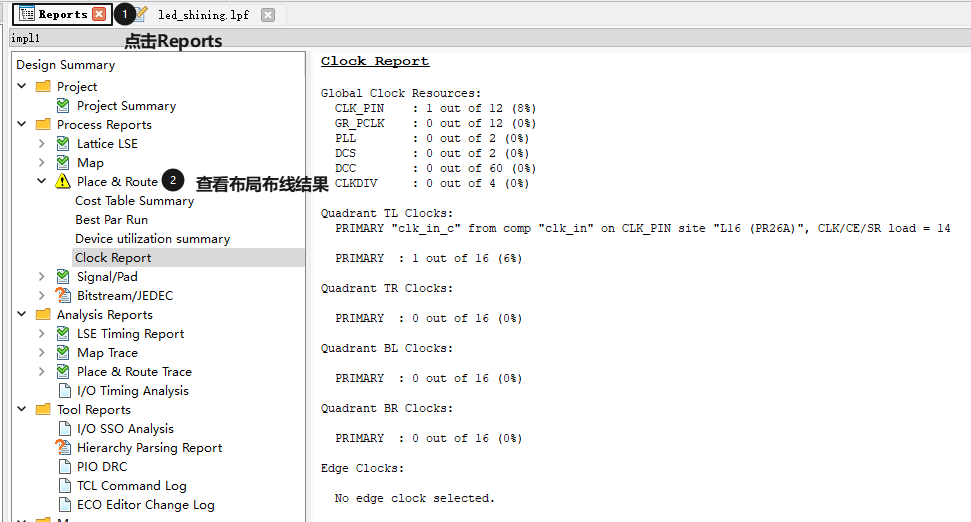

三、布局布线

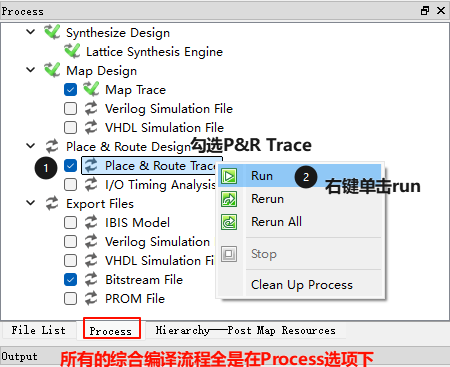

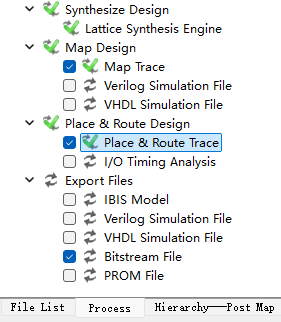

1)使能布局布线

在软件左侧Process栏,选择Process,直接双击Export Files,所有布局布线输出依次完成,结束后,所有选项显示绿色对勾。到这里就完成了程序的布局布线。

2)查看时序报告 略

此处程序过于简单,也没有约束时钟,故时序报告也没什么好看的

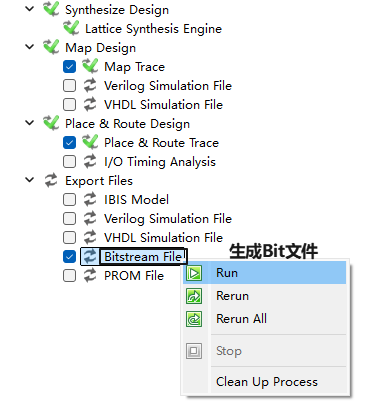

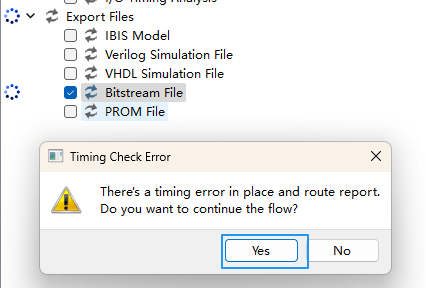

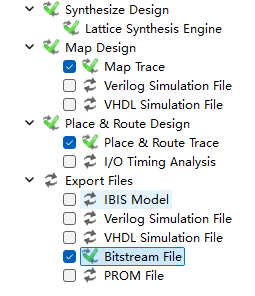

四、生成bit文件

五、固化程序

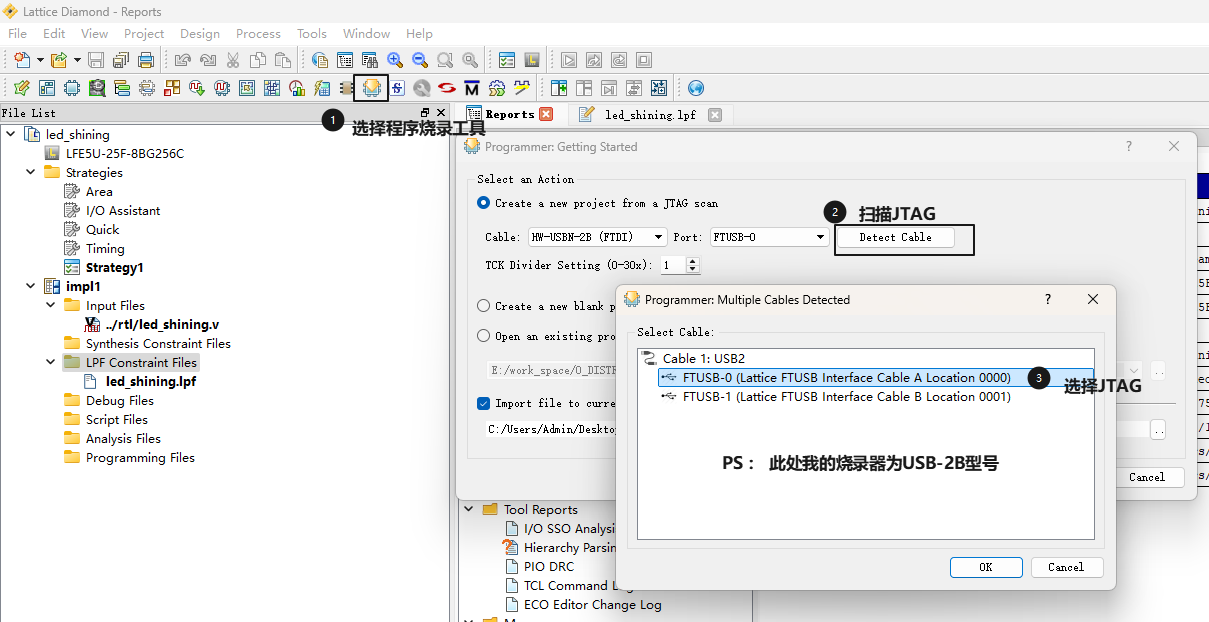

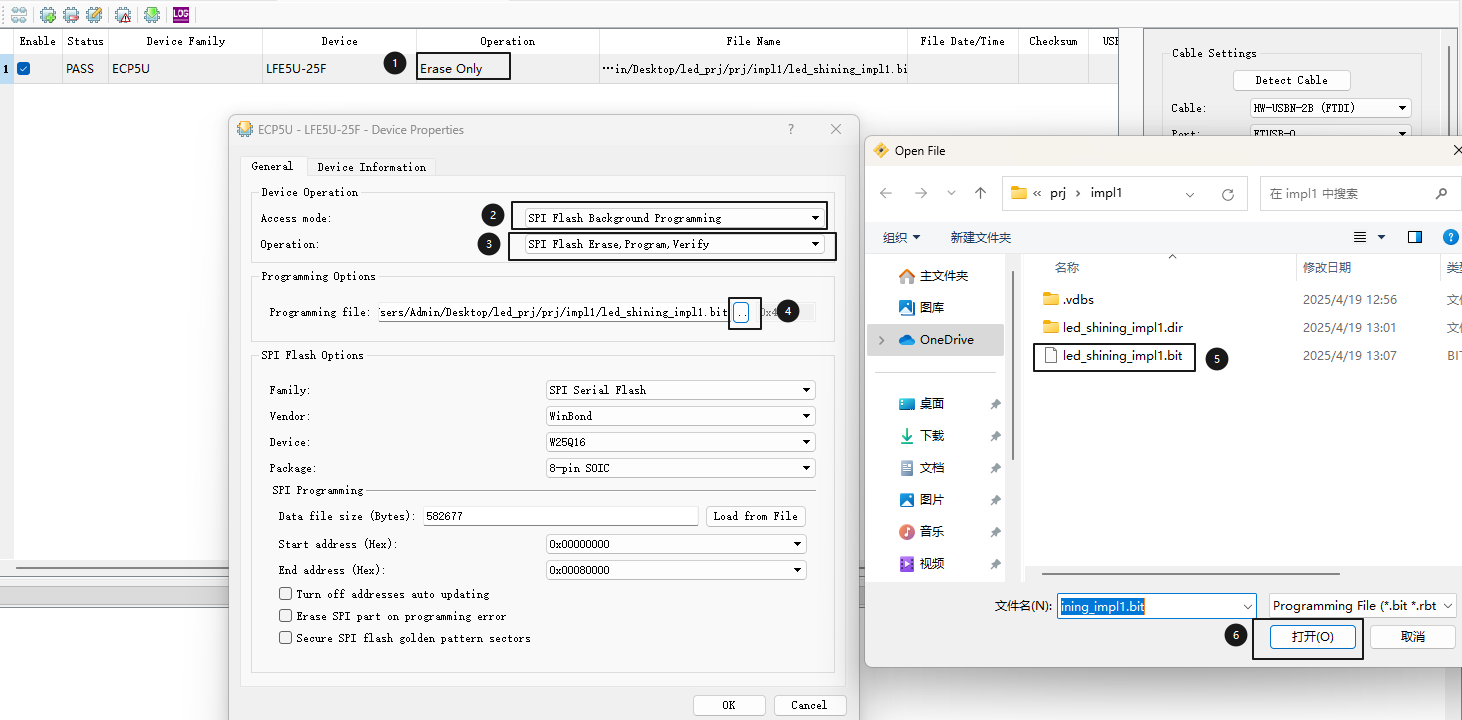

1)扫描JATG

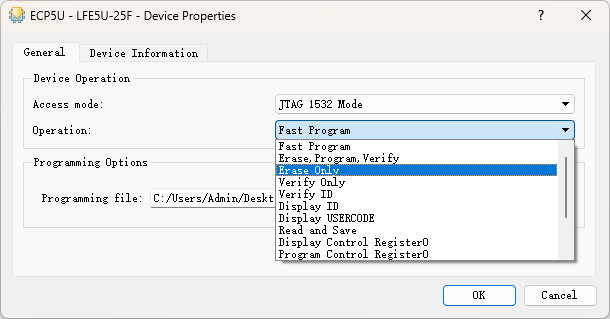

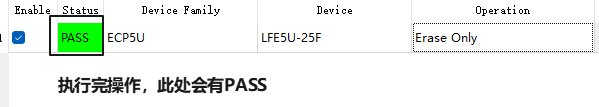

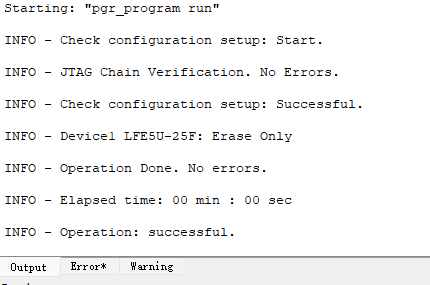

2)擦除程序(仅针对ECP5U系列,固化前需要擦除)

3)选择操作模式及bit文件

4)选择对应的FLASH

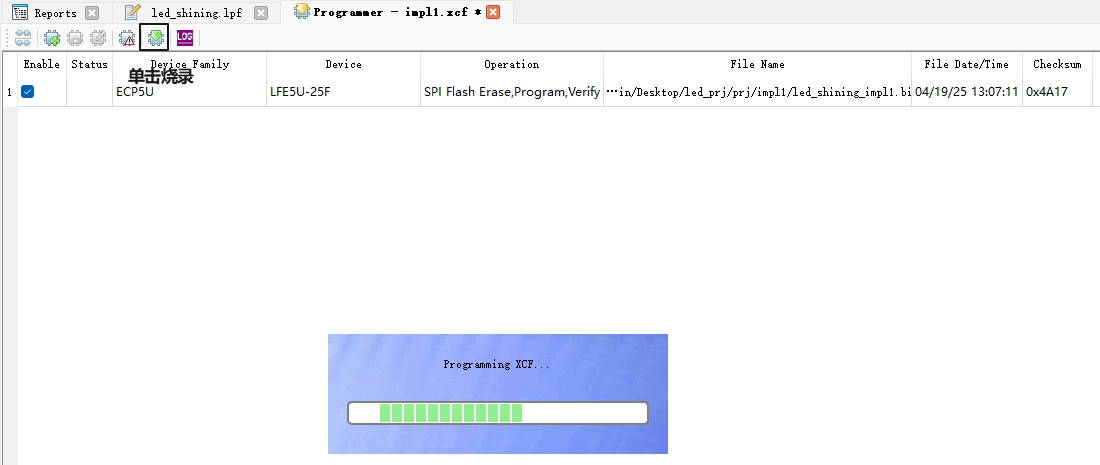

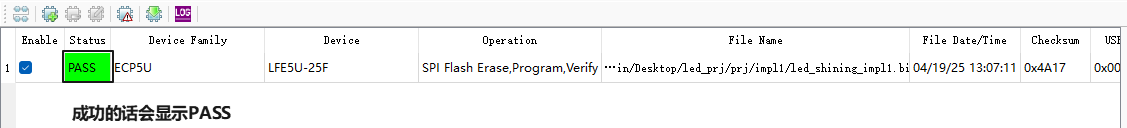

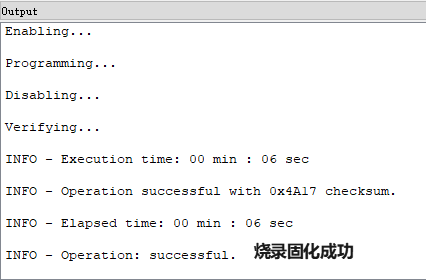

5)固化烧录程序

接下来重启FPGA板,即可运行程序。

PS:在以上流程遇到的问题,我都总结在以下链接

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?