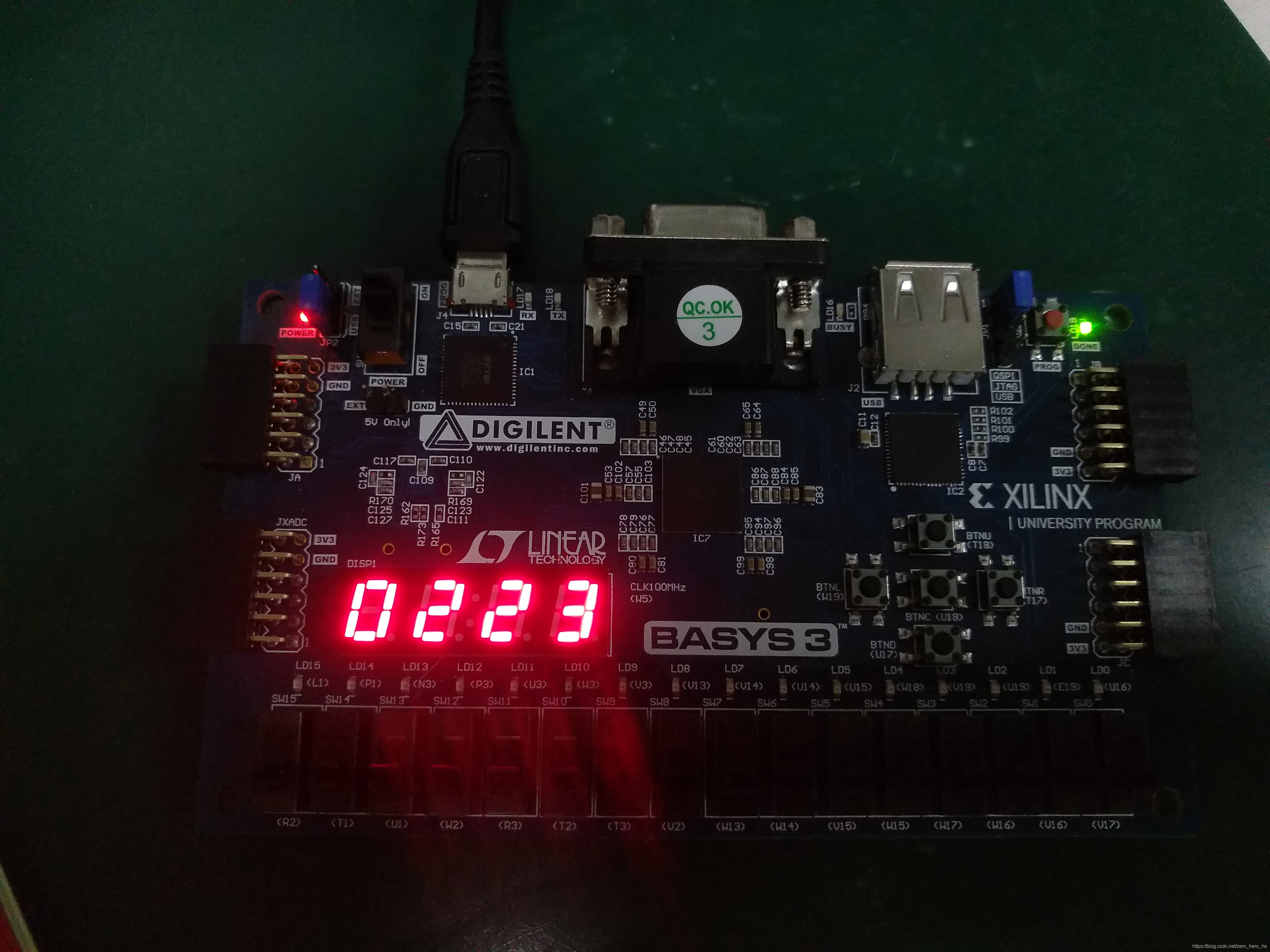

基于Vivado的四位数码管扫描显示VHDL实现

最近在学习FPGA,记录一下自己遇到的一些问题。

一、所需平台:

1、硬件平台:basys3(XILINX);

2、开发软件:vivado2017.4;

3、使用语言:VHDL;

二、遇到的一些问题:

1、位选信号扫描频率大概在1000hz左右,显示正常。频率过高显示乱码,过低则会出现闪烁。(利用人眼暂留原理)

2、由1可知,我们要涉及到时钟分频。开发板时钟为100MHZ,所以分频数N为100000,用计数器分频时,计数个数为(m=N/2-1),一定要给计数赋初值,否则无法计数,导致没有分频。还有就是目标分频时钟clk_f也要赋初值。

3、数码管的位选及单个数码管的段选信号,一定要分清楚是共阴还是共阳,及高电平/低电平有效。(basys3是共阳,低电平有效)

4、数码管的段控制信号的顺序一定要和管脚约束相匹配,八段数码管段由低到高位为(abcdefgh)。(h为小数点,有些没有)

三、相关代码:

1、代码

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity scan_led is

Port ( clk : in STD_LOGIC;

seg : out STD_LOGIC_VECTOR (7 downto 0); --段显示控制信号

scan : out STD_LOGIC_VECTOR (3 downto 0)); --数码管地址选择控制信号

end scan_led;

architecture Behavioral of scan_led is

signal cnt4 : integer range 0 to 3;

signal data : integer range 0 to 15;

signal cnt : integer range 0 to 49999:=0;

signal clk_f: std_logic:='0';

begin

--时钟分频产生1000hz

clk_f_gen:process(clk)

begin

if(clk'event and clk='1')then

cnt<=cnt+1;

if(cnt=49999)then

cnt<=0;

end if;

end if;

end process;

process(clk)

begin

if(clk'event and clk='1')then

if(cnt=0)then

clk_f<=not clk_f;

end if;

end if;

end process;

--用于扫描数码管地址的计数器

process(clk)

begin

if(clk_f'event and clk_f='1')then

cnt4<=cnt4+1;

if(cnt4=3) then

cnt4<=0;

end if;

end if;

end process;

--数码管地址扫描

process(clk)

begin

if(clk'event and clk='1')then

case cnt4 is

when 0 =>scan<="0111";

when 1 =>scan<="1011";

when 2 =>scan<="1101";

when 3 =>scan<="1110";

when others=>null;

end case;

end if;

end process;

--四个数码管分别显示的数字

process(clk)

begin

if(clk'event and clk='1')then

case cnt4 is

when 0 =>data<=0; --显示0223

when 1 =>data<=2;

when 2 =>data<=2;

when 3 =>data<=3;

when others=>null;

end case;

end if;

end process;

--七段译码

process(clk)

begin

if(clk'event and clk='1')then

case data is

when 0 =>seg<="00000011";

when 1 =>seg<="10011111";

when 2 =>seg<="00100101";

when 3 =>seg<="00001101";

when 4 =>seg<="10011001";

when 5 =>seg<="01001001";

when 6 =>seg<="01000001";

when 7 =>seg<="00011111";

when 8 =>seg<="00000001";

when 9 =>seg<="00001001";

when 10 =>seg<="00010001";

when 11 =>seg<="11000001";

when 12 =>seg<="01100011";

when 13 =>seg<="10000101";

when 14 =>seg<="01100001";

when 15 =>seg<="01110001";

when others=>null;

end case;

end if;

end process;

end Behavioral;

2、testbench文件:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity scan_tb is

-- Port ( );

end scan_tb;

architecture Behavioral of scan_tb is

component scan_led

port(

clk : in STD_LOGIC;

seg : out STD_LOGIC_VECTOR (7 downto 0);

scan : out STD_LOGIC_VECTOR (3 downto 0)

);

end component;

--输入信号

signal clk : STD_LOGIC := '0';

--输出信号

signal seg : STD_LOGIC_VECTOR(7 downto 0);

signal scan : STD_LOGIC_VECTOR(3 downto 0);

--时钟周期的定义

constant clk_period:time:=20ns;

begin

instant: scan_led port map

(

clk=>clk,seg=>seg,scan=>scan

);

clk_gen:process

begin

clk<='1';

wait for clk_period/2;

clk<='0';

wait for clk_period/2;

end process;

end Behavioral;

3、约束文件xdc:

set_property PACKAGE_PIN W5 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk]

set_property PACKAGE_PIN W7 [get_ports {seg[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[7]}]

set_property PACKAGE_PIN W6 [get_ports {seg[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[6]}]

set_property PACKAGE_PIN U8 [get_ports {seg[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[5]}]

set_property PACKAGE_PIN V8 [get_ports {seg[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[4]}]

set_property PACKAGE_PIN U5 [get_ports {seg[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[3]}]

set_property PACKAGE_PIN V5 [get_ports {seg[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[2]}]

set_property PACKAGE_PIN U7 [get_ports {seg[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[1]}]

set_property PACKAGE_PIN V7 [get_ports {seg[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[0]}]

set_property PACKAGE_PIN U2 [get_ports {scan[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {scan[0]}]

set_property PACKAGE_PIN U4 [get_ports {scan[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {scan[1]}]

set_property PACKAGE_PIN V4 [get_ports {scan[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {scan[2]}]

set_property PACKAGE_PIN W4 [get_ports {scan[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {scan[3]}]

四、基于vhdl的仿真文件书写(testbench)

详情参照下面博客:链接: [link](https://blog.youkuaiyun.com/chiyiwei7384/article/details/79753435).

五、basys3开发板约束(xdc)参考文件:

## This file is a general .xdc for the Basys3 rev B board

## To use it in a project:

## - uncomment the lines corresponding to used pins

## - rename the used ports (in each line, after get_ports) according to the top level signal names in the project

## Clock signal

#set_property PACKAGE_PIN W5 [get_ports clk]

#set_property IOSTANDARD LVCMOS33 [get_ports clk]

#create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk]

## Switches

#set_property PACKAGE_PIN V17 [get_ports {sw[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[0]}]

#set_property PACKAGE_PIN V16 [get_ports {sw[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[1]}]

#set_property PACKAGE_PIN W16 [get_ports {sw[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[2]}]

#set_property PACKAGE_PIN W17 [get_ports {sw[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[3]}]

#set_property PACKAGE_PIN W15 [get_ports {sw[4]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[4]}]

#set_property PACKAGE_PIN V15 [get_ports {sw[5]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[5]}]

#set_property PACKAGE_PIN W14 [get_ports {sw[6]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[6]}]

#set_property PACKAGE_PIN W13 [get_ports {sw[7]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[7]}]

#set_property PACKAGE_PIN V2 [get_ports {sw[8]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[8]}]

#set_property PACKAGE_PIN T3 [get_ports {sw[9]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[9]}]

#set_property PACKAGE_PIN T2 [get_ports {sw[10]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[10]}]

#set_property PACKAGE_PIN R3 [get_ports {sw[11]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[11]}]

#set_property PACKAGE_PIN W2 [get_ports {sw[12]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[12]}]

#set_property PACKAGE_PIN U1 [get_ports {sw[13]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[13]}]

#set_property PACKAGE_PIN T1 [get_ports {sw[14]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[14]}]

#set_property PACKAGE_PIN R2 [get_ports {sw[15]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {sw[15]}]

## LEDs

#set_property PACKAGE_PIN U16 [get_ports {led[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

#set_property PACKAGE_PIN E19 [get_ports {led[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

#set_property PACKAGE_PIN U19 [get_ports {led[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

#set_property PACKAGE_PIN V19 [get_ports {led[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

#set_property PACKAGE_PIN W18 [get_ports {led[4]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}]

#set_property PACKAGE_PIN U15 [get_ports {led[5]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}]

#set_property PACKAGE_PIN U14 [get_ports {led[6]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}]

#set_property PACKAGE_PIN V14 [get_ports {led[7]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}]

#set_property PACKAGE_PIN V13 [get_ports {led[8]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[8]}]

#set_property PACKAGE_PIN V3 [get_ports {led[9]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[9]}]

#set_property PACKAGE_PIN W3 [get_ports {led[10]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[10]}]

#set_property PACKAGE_PIN U3 [get_ports {led[11]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[11]}]

#set_property PACKAGE_PIN P3 [get_ports {led[12]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[12]}]

#set_property PACKAGE_PIN N3 [get_ports {led[13]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[13]}]

#set_property PACKAGE_PIN P1 [get_ports {led[14]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[14]}]

#set_property PACKAGE_PIN L1 [get_ports {led[15]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {led[15]}]

##7 segment display

#set_property PACKAGE_PIN W7 [get_ports {seg[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[0]}]

#set_property PACKAGE_PIN W6 [get_ports {seg[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[1]}]

#set_property PACKAGE_PIN U8 [get_ports {seg[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[2]}]

#set_property PACKAGE_PIN V8 [get_ports {seg[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[3]}]

#set_property PACKAGE_PIN U5 [get_ports {seg[4]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[4]}]

#set_property PACKAGE_PIN V5 [get_ports {seg[5]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[5]}]

#set_property PACKAGE_PIN U7 [get_ports {seg[6]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {seg[6]}]

#set_property PACKAGE_PIN V7 [get_ports dp]

#set_property IOSTANDARD LVCMOS33 [get_ports dp]

#set_property PACKAGE_PIN U2 [get_ports {an[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {an[0]}]

#set_property PACKAGE_PIN U4 [get_ports {an[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {an[1]}]

#set_property PACKAGE_PIN V4 [get_ports {an[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {an[2]}]

#set_property PACKAGE_PIN W4 [get_ports {an[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {an[3]}]

##Buttons

#set_property PACKAGE_PIN U18 [get_ports btnC]

#set_property IOSTANDARD LVCMOS33 [get_ports btnC]

#set_property PACKAGE_PIN T18 [get_ports btnU]

#set_property IOSTANDARD LVCMOS33 [get_ports btnU]

#set_property PACKAGE_PIN W19 [get_ports btnL]

#set_property IOSTANDARD LVCMOS33 [get_ports btnL]

#set_property PACKAGE_PIN T17 [get_ports btnR]

#set_property IOSTANDARD LVCMOS33 [get_ports btnR]

#set_property PACKAGE_PIN U17 [get_ports btnD]

#set_property IOSTANDARD LVCMOS33 [get_ports btnD]

##Pmod Header JA

##Sch name = JA1

#set_property PACKAGE_PIN J1 [get_ports {JA[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[0]}]

##Sch name = JA2

#set_property PACKAGE_PIN L2 [get_ports {JA[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[1]}]

##Sch name = JA3

#set_property PACKAGE_PIN J2 [get_ports {JA[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[2]}]

##Sch name = JA4

#set_property PACKAGE_PIN G2 [get_ports {JA[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[3]}]

##Sch name = JA7

#set_property PACKAGE_PIN H1 [get_ports {JA[4]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[4]}]

##Sch name = JA8

#set_property PACKAGE_PIN K2 [get_ports {JA[5]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[5]}]

##Sch name = JA9

#set_property PACKAGE_PIN H2 [get_ports {JA[6]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[6]}]

##Sch name = JA10

#set_property PACKAGE_PIN G3 [get_ports {JA[7]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JA[7]}]

##Pmod Header JB

##Sch name = JB1

#set_property PACKAGE_PIN A14 [get_ports {JB[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[0]}]

##Sch name = JB2

#set_property PACKAGE_PIN A16 [get_ports {JB[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[1]}]

##Sch name = JB3

#set_property PACKAGE_PIN B15 [get_ports {JB[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[2]}]

##Sch name = JB4

#set_property PACKAGE_PIN B16 [get_ports {JB[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[3]}]

##Sch name = JB7

#set_property PACKAGE_PIN A15 [get_ports {JB[4]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[4]}]

##Sch name = JB8

#set_property PACKAGE_PIN A17 [get_ports {JB[5]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[5]}]

##Sch name = JB9

#set_property PACKAGE_PIN C15 [get_ports {JB[6]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[6]}]

##Sch name = JB10

#set_property PACKAGE_PIN C16 [get_ports {JB[7]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JB[7]}]

##Pmod Header JC

##Sch name = JC1

#set_property PACKAGE_PIN K17 [get_ports {JC[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[0]}]

##Sch name = JC2

#set_property PACKAGE_PIN M18 [get_ports {JC[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[1]}]

##Sch name = JC3

#set_property PACKAGE_PIN N17 [get_ports {JC[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[2]}]

##Sch name = JC4

#set_property PACKAGE_PIN P18 [get_ports {JC[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[3]}]

##Sch name = JC7

#set_property PACKAGE_PIN L17 [get_ports {JC[4]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[4]}]

##Sch name = JC8

#set_property PACKAGE_PIN M19 [get_ports {JC[5]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[5]}]

##Sch name = JC9

#set_property PACKAGE_PIN P17 [get_ports {JC[6]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[6]}]

##Sch name = JC10

#set_property PACKAGE_PIN R18 [get_ports {JC[7]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JC[7]}]

##Pmod Header JXADC

##Sch name = XA1_P

#set_property PACKAGE_PIN J3 [get_ports {JXADC[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[0]}]

##Sch name = XA2_P

#set_property PACKAGE_PIN L3 [get_ports {JXADC[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[1]}]

##Sch name = XA3_P

#set_property PACKAGE_PIN M2 [get_ports {JXADC[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[2]}]

##Sch name = XA4_P

#set_property PACKAGE_PIN N2 [get_ports {JXADC[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[3]}]

##Sch name = XA1_N

#set_property PACKAGE_PIN K3 [get_ports {JXADC[4]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[4]}]

##Sch name = XA2_N

#set_property PACKAGE_PIN M3 [get_ports {JXADC[5]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[5]}]

##Sch name = XA3_N

#set_property PACKAGE_PIN M1 [get_ports {JXADC[6]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[6]}]

##Sch name = XA4_N

#set_property PACKAGE_PIN N1 [get_ports {JXADC[7]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[7]}]

##VGA Connector

#set_property PACKAGE_PIN G19 [get_ports {vgaRed[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[0]}]

#set_property PACKAGE_PIN H19 [get_ports {vgaRed[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[1]}]

#set_property PACKAGE_PIN J19 [get_ports {vgaRed[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[2]}]

#set_property PACKAGE_PIN N19 [get_ports {vgaRed[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[3]}]

#set_property PACKAGE_PIN N18 [get_ports {vgaBlue[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[0]}]

#set_property PACKAGE_PIN L18 [get_ports {vgaBlue[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[1]}]

#set_property PACKAGE_PIN K18 [get_ports {vgaBlue[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[2]}]

#set_property PACKAGE_PIN J18 [get_ports {vgaBlue[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[3]}]

#set_property PACKAGE_PIN J17 [get_ports {vgaGreen[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[0]}]

#set_property PACKAGE_PIN H17 [get_ports {vgaGreen[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[1]}]

#set_property PACKAGE_PIN G17 [get_ports {vgaGreen[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[2]}]

#set_property PACKAGE_PIN D17 [get_ports {vgaGreen[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[3]}]

#set_property PACKAGE_PIN P19 [get_ports Hsync]

#set_property IOSTANDARD LVCMOS33 [get_ports Hsync]

#set_property PACKAGE_PIN R19 [get_ports Vsync]

#set_property IOSTANDARD LVCMOS33 [get_ports Vsync]

##USB-RS232 Interface

#set_property PACKAGE_PIN B18 [get_ports RsRx]

#set_property IOSTANDARD LVCMOS33 [get_ports RsRx]

#set_property PACKAGE_PIN A18 [get_ports RsTx]

#set_property IOSTANDARD LVCMOS33 [get_ports RsTx]

##USB HID (PS/2)

#set_property PACKAGE_PIN C17 [get_ports PS2Clk]

#set_property IOSTANDARD LVCMOS33 [get_ports PS2Clk]

#set_property PULLUP true [get_ports PS2Clk]

#set_property PACKAGE_PIN B17 [get_ports PS2Data]

#set_property IOSTANDARD LVCMOS33 [get_ports PS2Data]

#set_property PULLUP true [get_ports PS2Data]

##Quad SPI Flash

##Note that CCLK_0 cannot be placed in 7 series devices. You can access it using the

##STARTUPE2 primitive.

#set_property PACKAGE_PIN D18 [get_ports {QspiDB[0]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[0]}]

#set_property PACKAGE_PIN D19 [get_ports {QspiDB[1]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[1]}]

#set_property PACKAGE_PIN G18 [get_ports {QspiDB[2]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[2]}]

#set_property PACKAGE_PIN F18 [get_ports {QspiDB[3]}]

#set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[3]}]

#set_property PACKAGE_PIN K19 [get_ports QspiCSn]

#set_property IOSTANDARD LVCMOS33 [get_ports QspiCSn]

六、上板演示

第一次写博客,没什么经验,主要是记录自己学习FPGA的过程及遇到的问题,希望对有需要的人有帮助,有什么问题大家共同讨论。

本文介绍了使用VHDL在Basys3开发板上实现四位数码管扫描显示的详细过程,包括硬件平台、遇到的频率、分频、信号极性等问题,以及代码、仿真和上板演示的步骤。适合FPGA初学者参考。

本文介绍了使用VHDL在Basys3开发板上实现四位数码管扫描显示的详细过程,包括硬件平台、遇到的频率、分频、信号极性等问题,以及代码、仿真和上板演示的步骤。适合FPGA初学者参考。

4211

4211