AXI和CHI握手机制

AMBA的CHI协议相比于AXI协议在一致性方面有很多扩展, 其使用场景、Channel的交互方式、上下游的信息传递、拓扑结构等都有很多不同. 本着有更多交流的目的, 分享在学习中的见解和内容.

前言

AXI采用VALID-READY握手的方式, 而CHI采用credit的方式进行上下游的交互, 同时credit的交互方式也与low power相关.

一、AXI握手机制

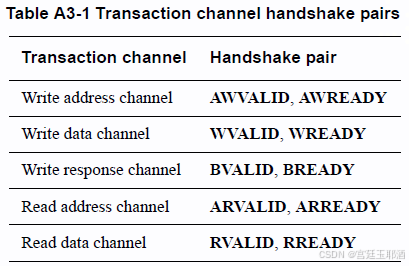

AXI采用VALID-READY的握手机制, 五个独立的Channel都有各自的握手信号, 例如AW Channel的握手信号为AWVALID/AWREADY, 如下图所示. Tx控制VALID信号, 而Rx控制READY信号.

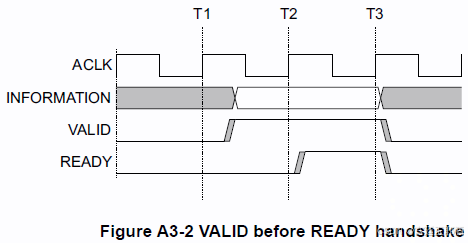

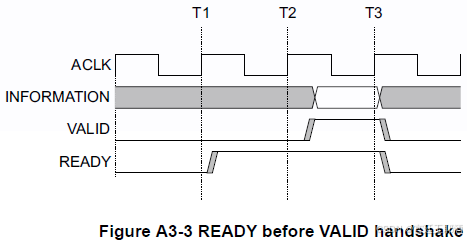

并且VALID和READY可以有任意的先后关系, Tx和Rx都在VALID-READY都为高时, 确认信息的交互成功.

为避免产生deadlock, 在同一Channel, AXI协议中规定:

- VAILD不能依赖于READY, 也就是说即便没有READY信号, VALID也可以为高.

- READY可以依赖于VALID, 但这不是必须的.

除此之外, AXI协议中还对不同Channel之间的握手有所要求.

例如ARVALID和ARREADY可以以任意顺序产生, 但是RVALID必须在ARVALID-ARREADY握手完成之后产生. 这一点很容易理解, 对于一个transaction, 只有在收到读命令之后, 才可以返回相应的数据, 不然返回的数据一定是不合法的.

在AW, W, B Channel也有类似的要求.

AXI协议的握手机制相对简单, 但是也带来了一些弊端, 因为VALID信号一旦为高, 在没有握手完成之前是不允许拉低的, 这就导致了如果Slave不能接受命令时, 会导致Master也无法释放对总线的控制. CHI协议在这方面做了改进.

二、CHI握手机制

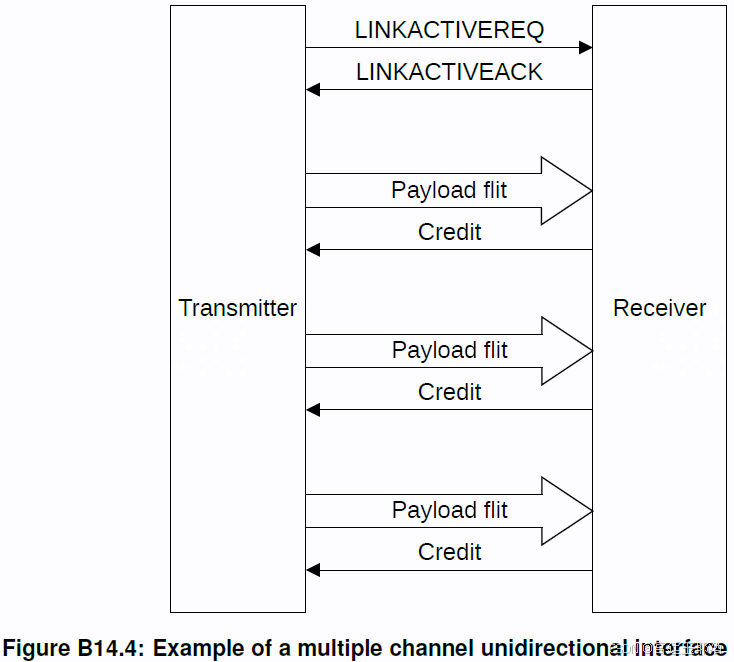

在CHI中, 与AXI类似的信息传递是在Link layer进行的, 其中flit是Link layer传输的基本单元.

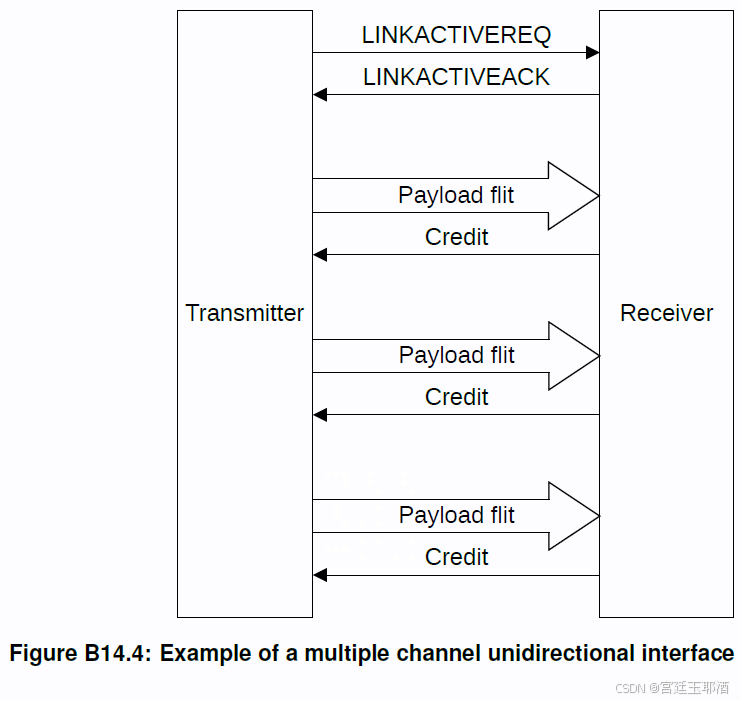

Transmitter是信息的发送方, Receiver是信息的接受方.

当链路被激活, credit(信用/资格)就在Tx和Rx直接交互, credit由Rx发出, Tx接收, 即接收方告诉发送方我可以一次性接收多少笔flit, Rx每拥有一个credit, 就可以发送一笔flit.

Tx在接收到flit之后, 再把接收到的credit随着response或者return data发出给Tx.

每个相互交互的Channel, 包括REQ/SNP/RSP/DATA都有独立的credit.

可以看出来, credit和握手最大的区别就在于, VALID-READY每次在只有在完成之后才能发送/接收下一个, 而credit是一次性发送/接收多笔.

三、CHI Low power

Flit和credit的交互方式除了能带来不阻塞总线的好处外, 还有low power的考虑, CHI在low power有三种不同levels的方式:

- Flit Level Clock Gating: 通过flitpend提前一个cycle拉高, 来实现cycle-by-cycle的clock gating.

- Link Activation: 通过Link activation和deactivation来entry/exit low power state.

- Protocol Activity Indication: Protocol layer的activity用来对transaction的传输进行low power控制.

下面分别对这几种方式进行介绍.

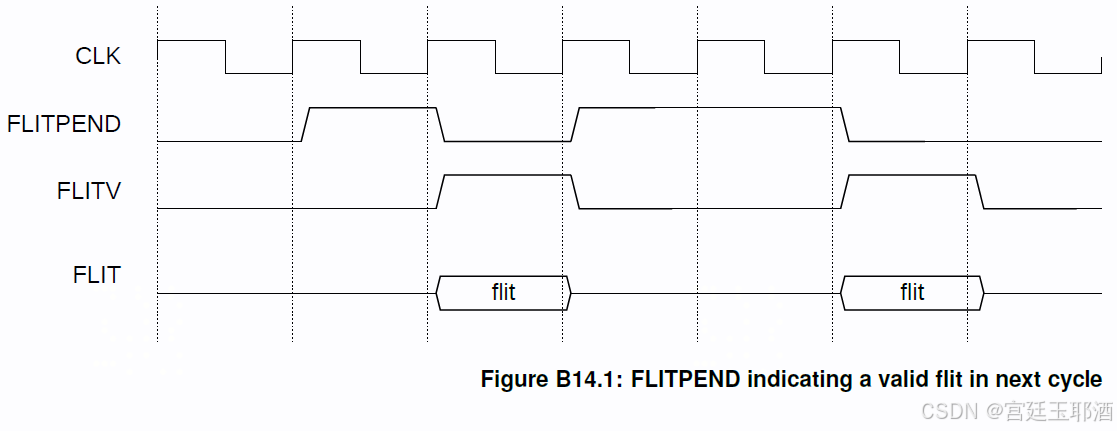

1. Flit level clock gating

FLITPEND用来指示下一个cycle可能会有有效的flit. flitpend、flit、credit是每个channel都有一组的.

FLITPEND的使用有一些要求:

- flitpend在Tx发送flit的前一个cycle必须assert.

- flitpend assert的下一个cycle不一定发送flit.

- flitpend可以一直assert, 应用于Tx不确定下个cycle是否有flit.

- flitpend assert不依赖于credit的多少或有无.

- flitpend可以在不发送flit的时候deassert.

2. Interface activation and deactivation

LINKACTIVEREQ-LINKACTIVEACK和flit-credit不同, 这对信号对于某个componet只有两组, Tx和Rx方向各有一组, 一般称为TxLINKACTIVEREQ、TxLINKACTIVEACK和RxLINKACTIVEREQ、RxLINKACTIVEACK.(Tx和Rx是相对的, 所有发送payload flit的定义为Tx, 所有发送credit的定义为Rx)

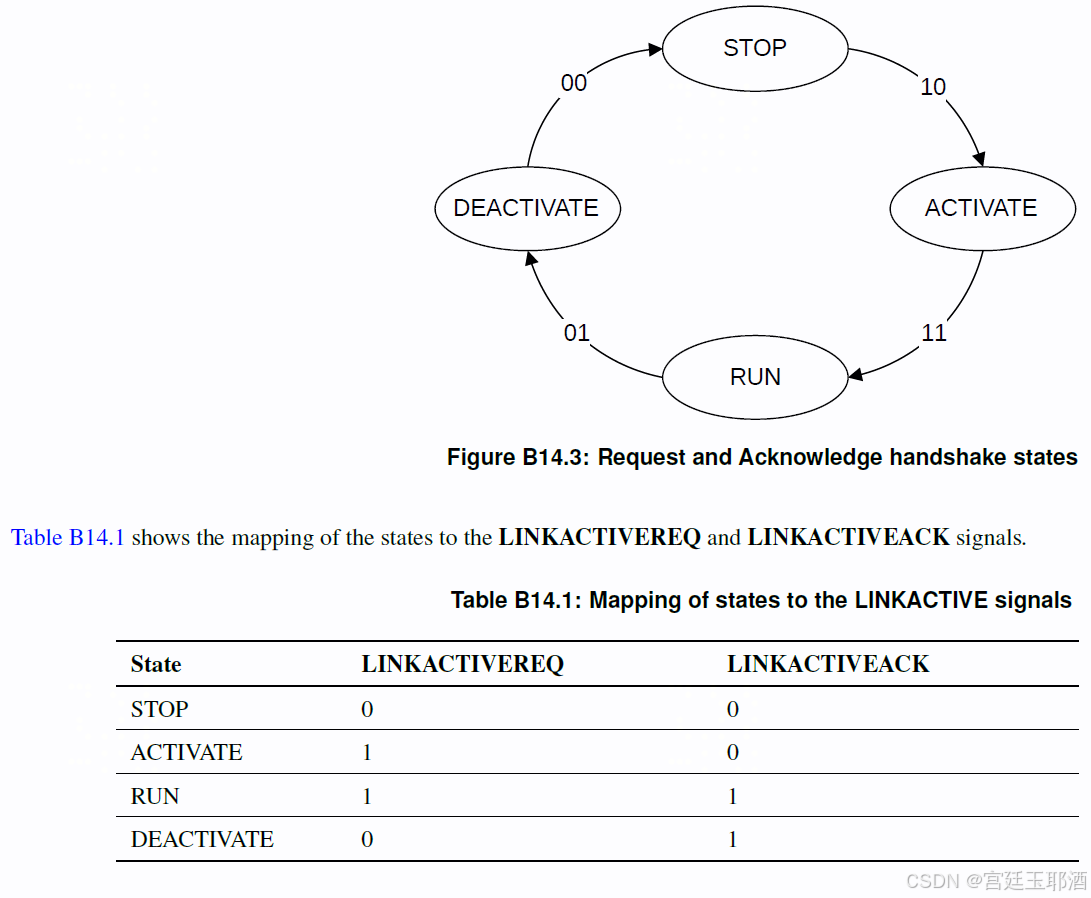

两根信号, 总共可以使Link layer工作在四个phase, 包括STOP, ACT, RUN, DEACT.

四个状态的含义:

- RUN: 两个component可以交换flits和credit.

- STOP: 处于low power状态不能有任何操作, 这时候所有的credit hold在Rx, Tx也不能发送任何flits.

- ACTIVATE: STOP到RUN的暂态. ACT状态时Tx不能发送任何flit, 但是可以接收credit, 同样的Rx可以在发送LINKACTIVEACK之前发送credit.

- DEACTIVATE: RUN到STOP的暂态.

RUN和STOP都是稳定态, 一旦进入可以保持无限长的时间.

ACTIVATE和DEACTIVATE都是暂态, 协议期待在这个状态只保持一段时间.

在退出复位时, credit都hold在Rx, 这时候Tx因为没有credit是不能发送flit的. 在正常工作期间, credit和flit是持续进行交换的. 一旦进入low power状态, Tx必须停止发送flit并将credit返还给Rx, 最终的状态与复位时一样.

四个状态的转移:

在协议中很清楚的描述了四个状态的转移.

虽然协议期待在ACTIVATE和DEACTIVATE之保持一段时间, 但并没有对这段时间有限制.

flit是Tx发的, Tx也决定了状态的切换, 因此Tx可以确保在状态切换时不发送任何payload flit, 只发送credit return flit.

credit是Rx发的, 但是状态切换不是由Rx决定的, 因此Rx可以有一段的反应时间, 在DEACT的时候仍然可以发送credit. 协议要求在DEACT到STOP的切换中收回所有credit.

即由Tx主导去使状态由RUN to STOP, or STOP to RUN. Link layer的ACT-DEACT是针对所有同方向的channel的, 因此

- 当一个状态要求Tx有能力接收credit的时候, Tx必须能在所有channel上接收credit.

- 当一个状态要求Rx有能力接收flit的时候, Rx必须能在所有channel上接收flit.

3. Protocol layer activity indication

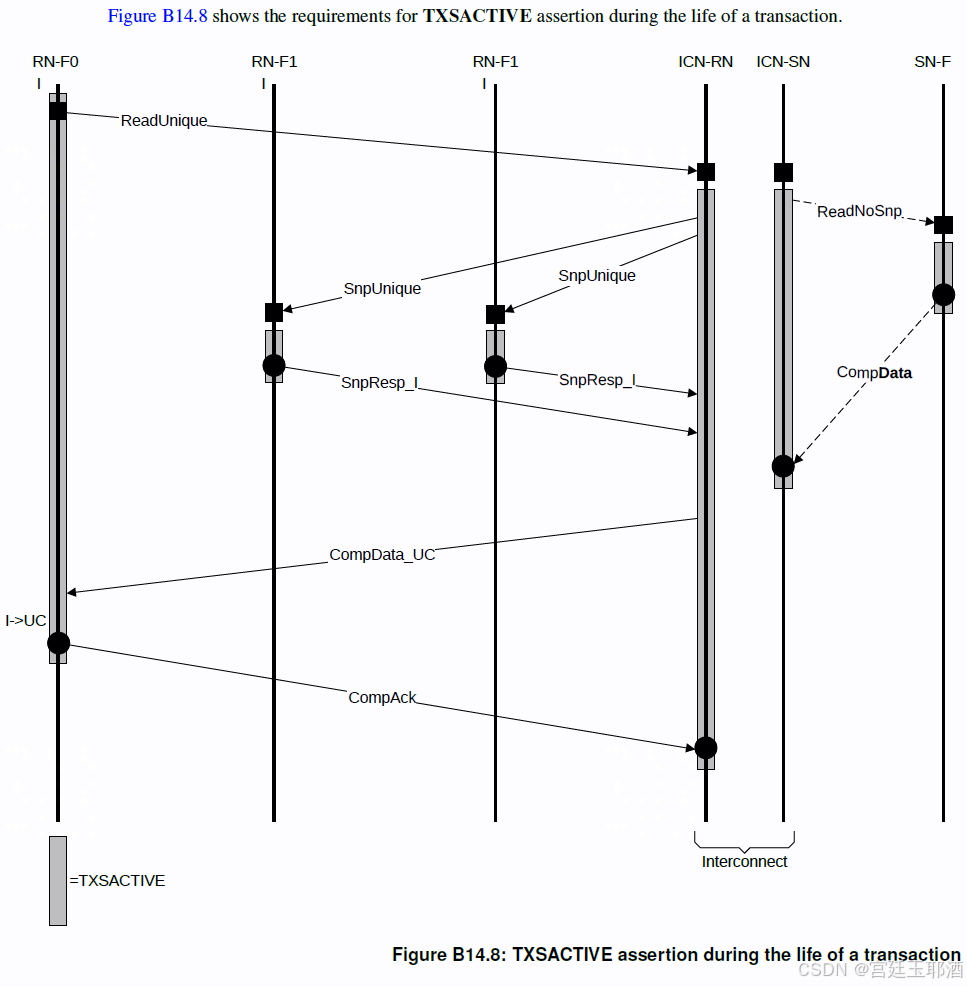

SACTIVE是用来指示transaction in process.

即在发送transaction之前必须要assert TXSACTIVE, 一直保持到所有transaction都被发送和接收.

如下图所示, TXSACTIVE对不同的componet有不同的要求.

TXSACTIVE signalng from a Request Node

当一个新的transaction被发送, RN必须assert TXSACTIVE, 并且该TXSACTIVE要至少同于或者先于TXREQFLITV assert, 一直到transaction结束.

一个transaction的完成标志取决于类型和传输方式, 比如ReadNoSnp transaction的完成响应一般是CompData的最后一笔flit, 但是如果ReadReceipt比CompData晚, 完成响应就是ReadReceipt.

TXSACTIVE signaling from a Subordinate Node

SN必须在接收TXSACTIVE之后, 在发送resp之前assert TXSACTIVE, 并在之后保持直至flit被接收.

TXSACTIVE signaling from an interconnect interface to Request Node

同样的, ICN在接收到transaction的时候assert TXSACTIVE, 直至完成resp.

RXSACTIVE signal

当Rx接收到RXSACTIVE时, 必须及时地ACT Link layer, RXSACTIVE主要是用来和TXSACTIVE结合使用, 用于entry/exit low power.

4. Relationship between SACTIVE and LINKACTIVE

SACTIVE信号是Protocol layer activity的指示. 当TXSACTIVE和RXSACTIVE都deassert时, 可以认为node是inactive的.

LINKACTIVE信号是Link layer activity的指示. 当Tx处于TxStop以及Rx处于RxStop状态时, 可以认为node或者interconnect是inactive.

但这二者是正交的, 即相互之间没有约束关系,

总结

以上就是今天要阐述的内容, 本文介绍了AXI和CHI在上下游信号交互上的区别, 以及CHI在low power方面的一些实践.

欢迎大家补充提问!

1985

1985

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?