前言

最近完成一个汉明码编码器设计的课程设计和基于Verilog语言的汉明码编译码设计 基于VHDL语言的汉明码编译码器的毕业设计的案例,对此进行了详细的总结。

目的:

通过仿真对汉明码的原理和QuartusII软件、Modelsim仿真软件、Verilog/VHDL语言的编写熟练掌握,

总体思路:

1.熟悉软件的使用

2.熟悉FPGA语言的语法和编写,仿真测试文件的编写

3.熟悉汉明码编码译码的原理和具体实现

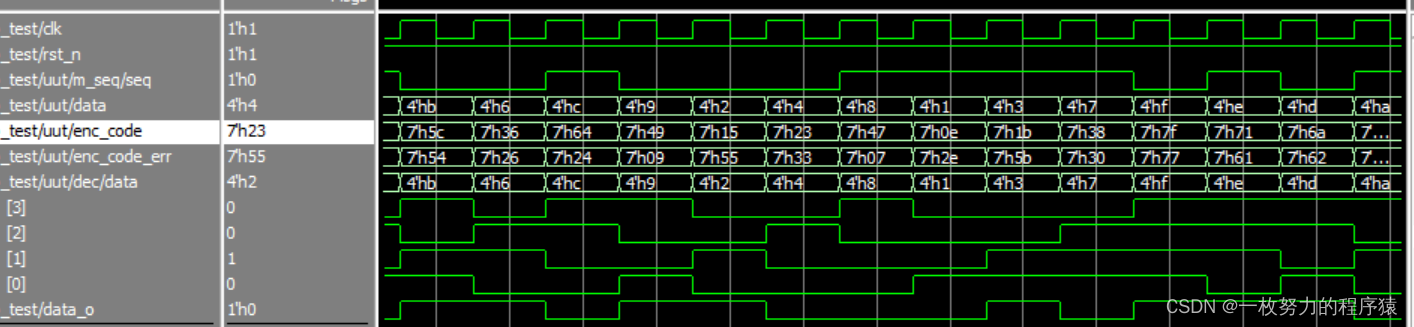

4.满足设计的要求,将输入数据(串行或者并行)输入到汉明码编码器中,随机产生一位错误,输入到汉明码的译码器中,参看输入和输出数据是否一致,验证设计方案的正确性。(根据设计需要,看是否需要并串之间的转化)

工具:

QuartusII Modelsim

仿真成果

一起学习一起成长

1247

1247

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?