国际电气、电子、信息、通信与生物信息学进展会议(AEEICB16)

基于纳米尺度的低功耗SRAM结构设计与实现

一、引言

由于晶体管微缩,纳米级SRAM模型面临多种设计问题。随着晶体管密度的增加,功耗的上升已成为当前处理器和片上系统设计中的主要问题。近年来,超大规模集成电路领域快速发展,导致器件结构尺寸减小,集成电路中的晶体管数量增多,电路复杂度提高。这类设计消耗更多的功率,并产生更多的热量。由于这些问题,电路设计人员逐渐认识到在各个设计层面上限制功耗并提高能效的重要性。

近年来,由于笔记本电脑、智能手机、手持通信设备和IC存储卡的需求不断增长,静态随机存取存储器结构在低功耗、低电压存储器设计方面经历了快速的变革。低功耗设计直接导致这些便携式设备的运行时间延长。

除此之外,还有多种原因:

1. 器件尺寸缩小

2. 便携性提升

3. 可靠性/精确性

4. 电池面积

这项工作的基本思路是研究一种静态随机存取存储器设计,该设计相较于相同技术下的传统单元将消耗更少的功率。

II. 核心单元

A. SRAM 6T单元

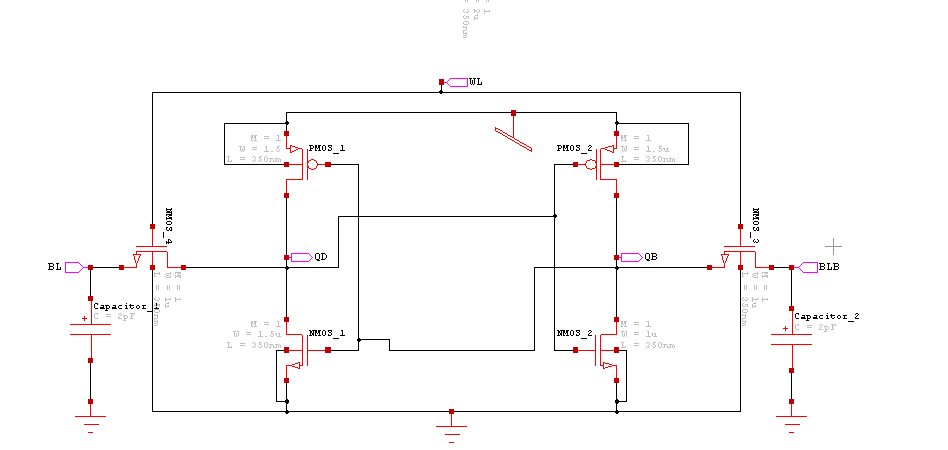

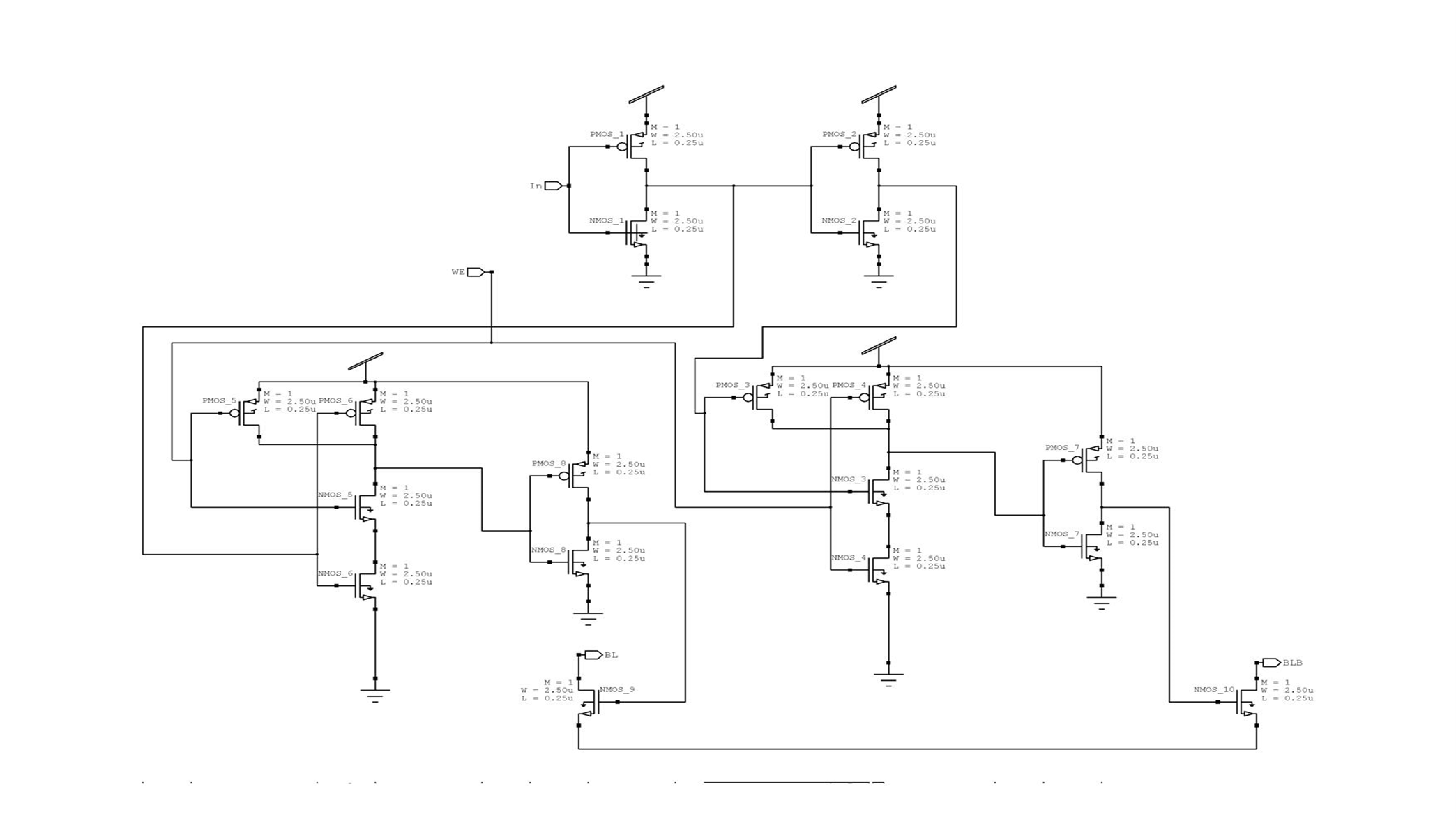

传统的SRAM 6T单元由两个交叉耦合的CMOS反相器和连接到位线的两个访问晶体管组成。图1显示了SRAM 6T单元的电路图。

B. 读操作

预充电位线(BL)、BLB(位线反)至VDD。打开WL(字线)。根据存储节点QD和QB的状态,位线或BLB将被拉低。

C. 写操作

驱动位线(BL)、位线反(BLB)并赋予必要的值(0,1 或 1,0)。打开字线,位线(BL 或 BLB)将用新值覆盖单元。

D. SRAM 11T 单元

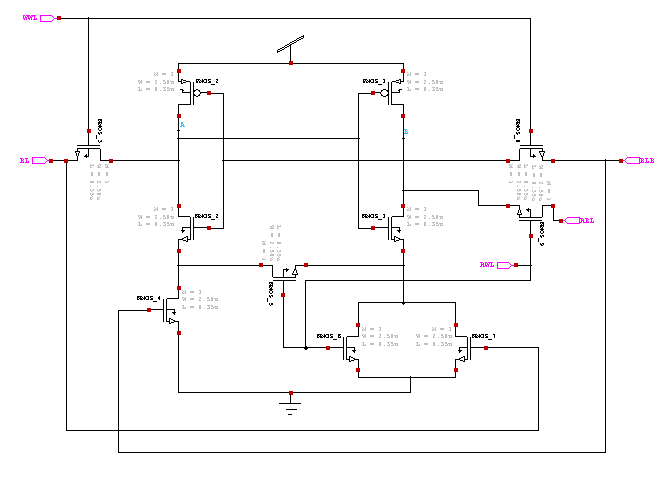

图2中显示了一个11T SRAM晶体管单元/设计。在此电路设计中,存在两个交叉耦合反相器,以及一个由读字线(RWL)访问的晶体管,用于读操作,另外两个晶体管由写字线(WWL)控制,用于写操作。

1. 读操作

在读操作期间,无需保持写字线(WWL)开启。进行读操作时,读字线(RWL)被打开,此时根据节点B处存储的数据,可执行读“1”或读“0”操作。读操作的输出通过读位线(RBL)获取。在SRAM 11T单元中,由于读操作期间位线不会放电,因此节省了大量功率。

2. 写操作

写操作通过写字线(RWL)执行,RWL可设置为零值,具体取决于执行的是写0操作还是写1操作。选择适当的位线(BL)和BLB的值。在写0操作和写1操作中,位线(BL)和BLB均不进行充电或放电,因此在写1和写0操作期间节省了大量功率。

E. SRAM 8T单元

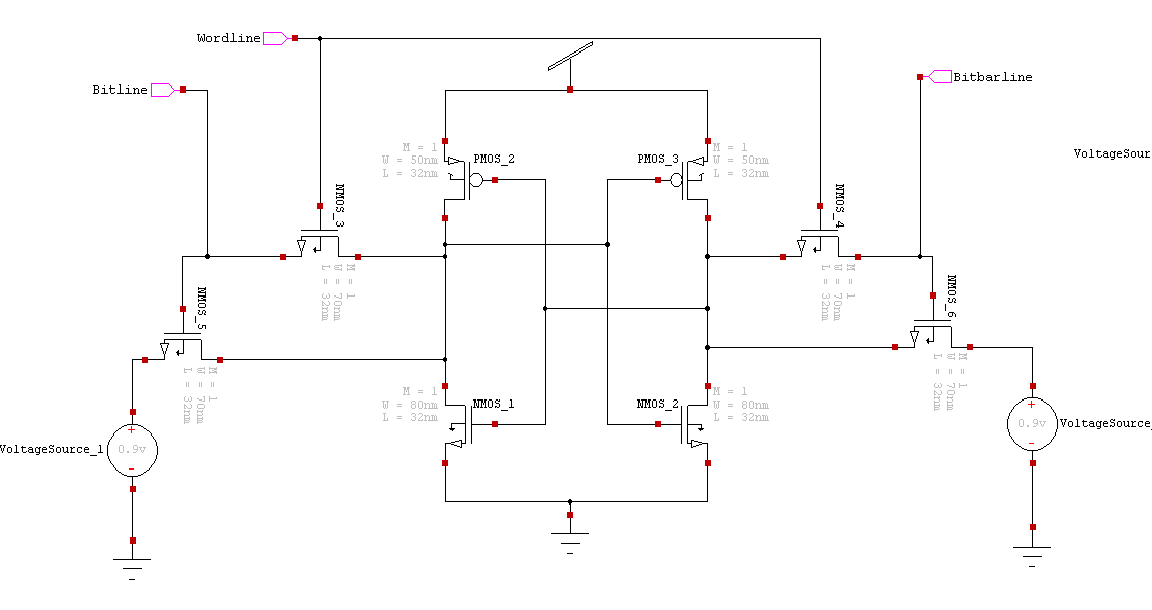

在8T SRAM晶体管单元中,S1和S2用作两个电压源,其中一个连接到位线(BL)的输出,另一个连接到位反线(BLB)。两个NMOS(N型沟道金属氧化物半导体)晶体管分别与位线(BL)和位线反相线(BLB)的输入相连,用于在写(0,1)操作期间直接控制电源的导通与关断。

SRAM 8T单元如下图3所示。这些电源在写操作期间减小了输出节点电压摆幅。

1. 读操作

在SRAM单元中执行读操作时,使用了预充电电路和灵敏放大器。预充电电路在读操作开始之前执行预充电操作。灵敏放大器将在读操作期间产生位线和位反线之间的电压差,并放大信号。

2. 写操作

在写0操作期间,位线(BL)为低电平,位反线为高电平。因此晶体管TN6导通,而TN5晶体管关断。于是电压源S2迫使位反线输出端的电压摆幅降低。同样,当执行写1操作时,TN5导通而TN6关断,因此电压源S1降低了位线输出端的电压摆幅。

III. 测量结果

A. 温度与功耗

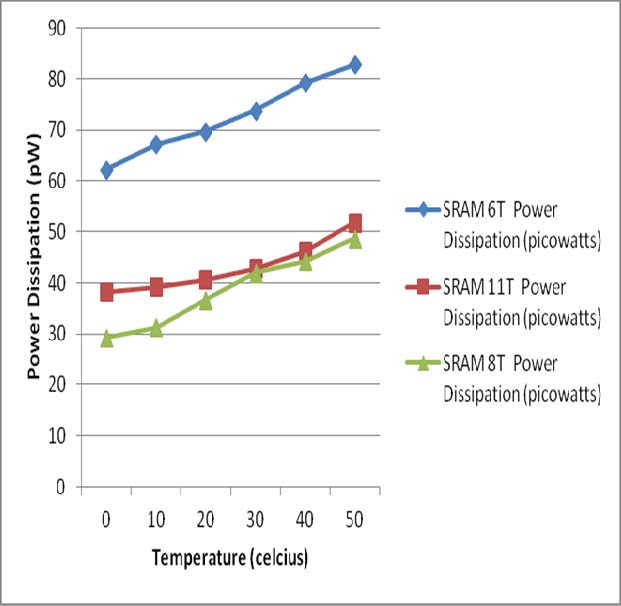

表1表示不同SRAM单元的功耗随温度的变化情况。观察发现,在高温下,SRAM 8T的功耗低于SRAM 6T和SRAM 11T单元。

| 温度(摄氏度) | SRAM 6T 功耗(皮瓦) | SRAM 11T 功耗(皮瓦) | SRAM 8T 功耗(皮瓦) |

|---|---|---|---|

| 0 | 62.166 | 38.271 | 29.379 |

| 10 | 67.352 | 39.231 | 31.251 |

| 20 | 69.578 | 40.698 | 36.389 |

| 30 | 73.810 | 42.702 | 41.972 |

| 40 | 79.163 | 46.144 | 44.274 |

| 50 | 82.771 | 51.570 | 48.678 |

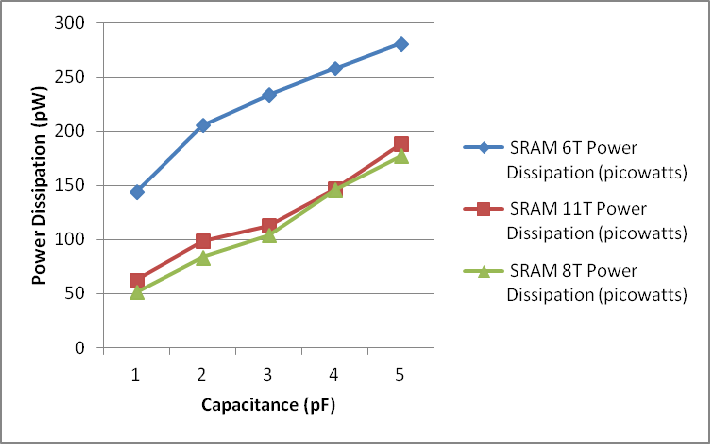

B. 电容与功耗

表2显示了功率消耗随位线(BL)电容的变化情况。随着位线电容器值的增加,功耗也随之增加。

| 电容 (pF) | SRAM 6T 功耗(皮瓦) | SRAM 11T 功耗(皮瓦) | SRAM 8T 功耗(皮瓦) |

|---|---|---|---|

| 1.0 | 143.650 | 62.530 | 51.354 |

| 2.0 | 205.413 | 98.591 | 83.493 |

| 3.0 | 233.717 | 112.437 | 103.157 |

| 4.0 | 258.406 | 146.424 | 145.411 |

| 5.0 | 281.364 | 188.316 | 177.460 |

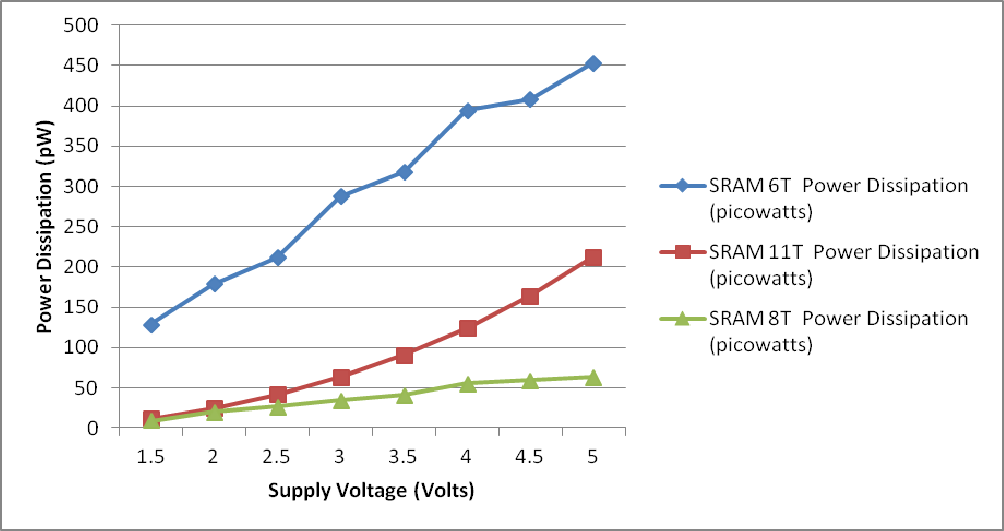

C. 供电电压与功耗

表3显示了功耗随供电电压的变化情况。由于动态功率与电源电压的平方成正比,因此随着供电电压的降低,功耗也随之减少。

| 供电电压(伏特) | SRAM 6T 功耗(皮瓦) | SRAM 11T 功耗(皮瓦) | SRAM 8T 功耗(皮瓦) |

|---|---|---|---|

| 1.5 | 128.968 | 11.838 | 8.943 |

| 2 | 179.493 | 24.633 | 19.938 |

| 2.5 | 211.650 | 41.350 | 26.551 |

| 3 | 287.717 | 63.467 | 34.754 |

| 3.5 | 318.103 | 91.243 | 41.131 |

| 4 | 394.418 | 124.300 | 55.409 |

| 4.5 | 408.433 | 164.537 | 59.265 |

| 5 | 453.360 | 212.563 | 63.236 |

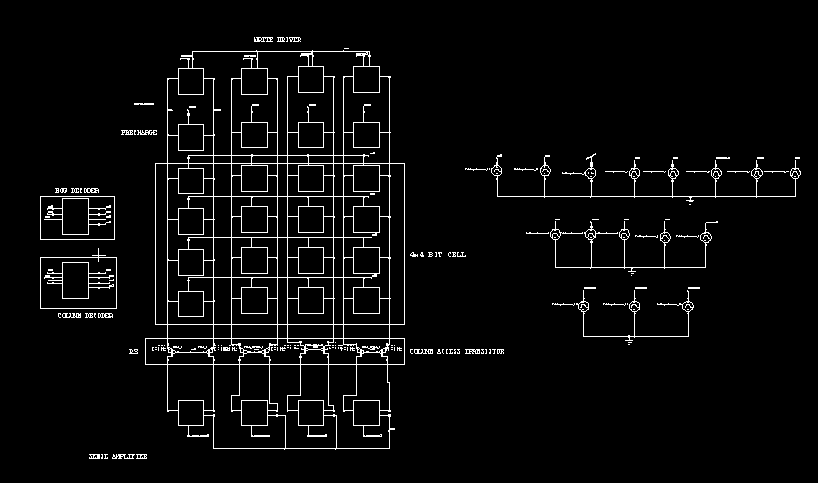

IV. 16位存储器设计

在对不同单元结构进行仿真后,我们发现SRAM 8T单元的功耗相较于SRAM 6T和SRAM 11T单元均较低。借助SRAM 8T单元,我们设计了一个16位SRAM存储单元及其外围电路。

A. 外围电路

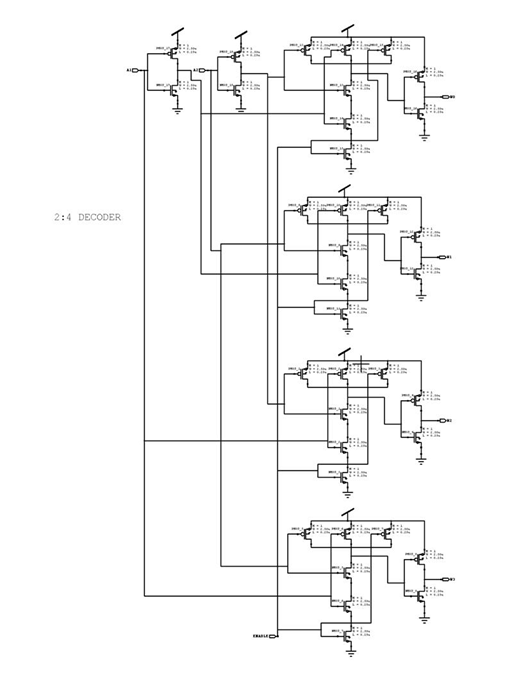

1. 译码器

图7 显示了2:4译码器的原理图。

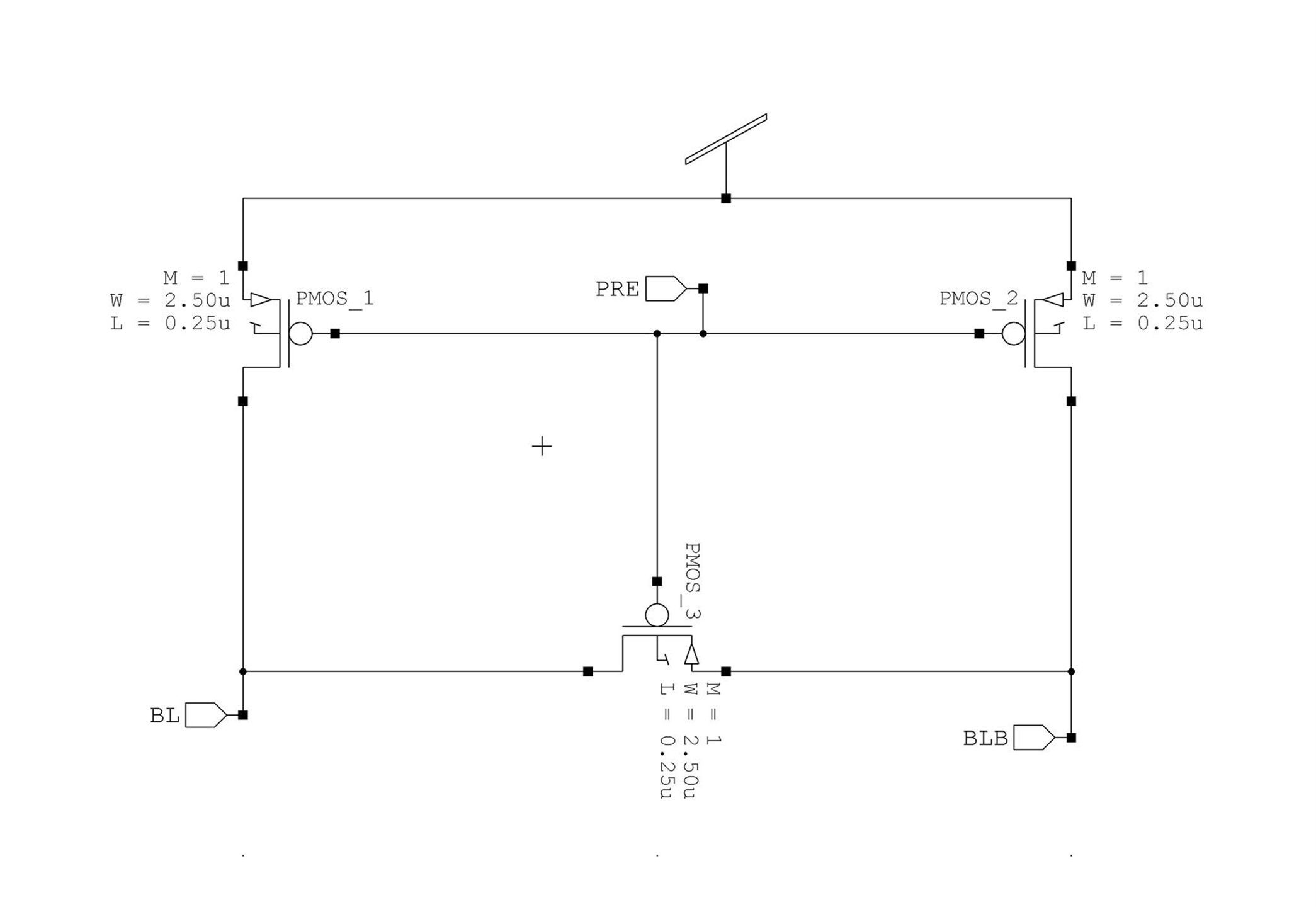

2. 预充电电路

图8 显示了预充电电路的原理图。

3. 写驱动电路

图9 显示了写入驱动电路的原理图。

4. 灵敏放大器电路

图10 显示了灵敏放大器电路的原理图。

5. 16位存储器电路

为了实现16位SRAM存储器,使用了2-4行译码器和2-4列译码器。它以4x4矩阵(SRAM 8T单元)的形式排列。此处,行译码器的输出连接到SRAM单元的字线‘wl’,所有单元的位线连接到列译码器。当译码器输入为00时,第一行的字线‘wl’变为高电平,所有SRAM单元都连接到位线。但根据列译码器的地址,将选择其中一列。通过这种方式,可选中SRAM存储器阵列中的特定单元。例如,如果行译码器和列译码器的地址均为‘00’,则位于存储器阵列‘00’位置的特定单元将被选中。如果行译码器的地址为‘00’,而列译码器的地址为‘01’,则选中第一行的第二个SRAM单元。图11显示了16位SRAM单元的原理图。

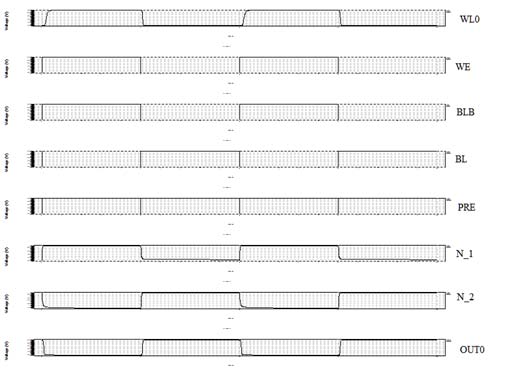

如下图12所示的读写波形。

五、结论

当温度升高时,SRAM 8T单元的功耗低于6T晶体管SRAM和11T晶体管SRAM单元。在不同的电源电压下,8T晶体管SRAM单元的功耗也低于SRAM 11T和SRAM 6T单元。随着供电电压的降低,功耗也随之减少。在较高的位线电容下,8T晶体管SRAM的功耗低于SRAM 6T晶体管和11T晶体管SRAM单元。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?