想学习FPGA的朋友,但苦于找不着优质的项目,这篇文章希望可以帮到你,以下四个项目不仅是github的高⭐项目,在学习的过程中自己也收益匪浅,已帮大家筛选

基于FPGA的CNN(卷积神经网络)加速

引言:

CNN(卷积神经网络)是一种深度学习架构,广泛应用于图像识别、分类和处理任务。它通过卷积层提取图像中的局部特征,利用池化层降低特征维度,再通过全连接层进行分类或回归。CNN能够自动学习图像中的特征,无需人工提取,具有强大的表征能力。其典型结构包括输入层、多个卷积层和池化层,以及输出层。常见的CNN模型有LeNet、AlexNet、VGG、ResNet等。

项目链接:

https://github.com/hunterlew/convolution_network_on_FPGA

1.项目描述

该项目是使用 ISE 14.7 软件和 vertix-7 FPGA 构建的。它执行具有某些加速策略的 7 层网络前向计算。首先,使用 MatConvNet 在 MSTAR 数据集上训练 SAR 目标分类网络并使用early-stop。然后,使用 Matlab 生成的COE 文件将权重和输入转换为 FPGA。接下来,设计原生 verilog 编写的模型来完成前向计算。该系统使用 16 位固定点数据来保持精度。结果证明,每张图像的成本不到 1ms,性能优于其他计算平台。

2.加速方案

为了在 FPGA 资源和速度之间进行权衡,考虑到第一个卷积层中 inputs 的大小和权重更大,第一个卷积 层使用 shift-register 结构进行加速。其他卷积层层仅使用 pipe-line 结构。请注意,有 18 个文件以 m_conv_1 命名,表示第一个卷积层中有 18 个 shift-registers。对于带宽限制,第二个卷积层使用通道分组并行化方案。我使用 v7-415t 和 v7-485t FPGA 进行比较,它们根据不同的资源量使用不同的组号(4 vs 1)。您可能会注意到文件 CNN_top.v 中的方案,其中信号 'ram_ready' 控制通道分组和合并。

3.推荐原因

学习该项目可以详细了解FPGA实现CNN网络加速的过程,设计过程中要考虑的量化、流水线划分、并行结构设计,如何平衡速度和面积等等都有涉及

基于FPGA的FOC电机控制算法

引言:

FOC(磁场定向控制)是一种先进的电机控制技术,主要用于三相交流电机(如无刷直流电机 和永磁同步电机)。其核心是将电机的定子电流分解为磁通分量(d轴电流)和转矩分量(q轴电流),并通过Park和Clark变换将三相交流系统转换为直流系统(dq域),实现独立控制,其广泛应用于电动汽车、工业自动化、机器人等领域

项目链接:

https://github.com/WangXuan95/FPGA-FOC

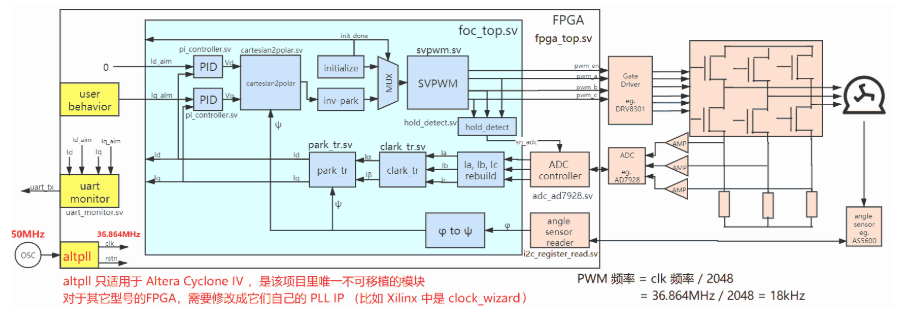

1.项目描述

该项目基于FPGA实现 FOC(磁场定向控制 )。它使用角度传感器(如磁性编码器)实现了一个完整的电流回路,可以执行扭矩控制,可用于驱动永磁同步电机 (PMSM) 或无刷直流电机 (BLDC)。

项目系统图

2.推荐原因

项目涉及SPI,I2C等低速接口协议设计,还有丰富的电机控制算法的verilog实现,诸如PID、SVPWM、正余弦计算、PARK变换等等。所有代码都是用纯 RTL 编写的,可以很容易移植到任意厂家的FPGA。

基于AXI4接口的UART协议模块

引言:

UART是一种用于设备间串行通信的协议。它通过两条数据线(RX接收、TX发送)实现数据的异步传输,无需共享时钟信号。数据以帧的形式发送,包含起始位、数据位(通常为8位)、可选的校验位和停止位。UART适用于低速应用,配置简单,支持全双工通信。

AXI是AMBA协议家族中的一种高性能总线标准,用于SoC设计中连接高速组件。它支持多个独立通道(如写地址、写数据、写响应、读地址、读数据),允许突发传输和多个未完成事务,从而提高数据传输效率。

项目链接:

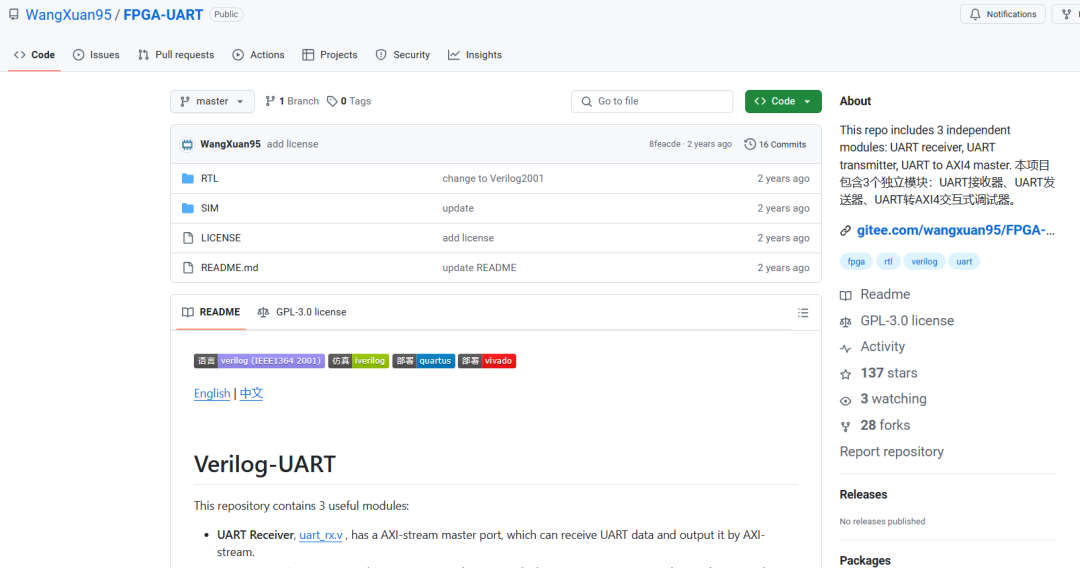

https://github.com/WangXuan95/FPGA-UART

1.项目描述

该项目设计了3个核心模块:

-

UART 接收器 (uart_rx.v): 具有 AXI-stream 主端口,可以接收 UART 数据并通过 AXI-stream 协议输出。

-

UART 发射器 (uart_tx.v): 具有 AXI-stream从端口,可以接收 AXI 流数据并通过 UART 输出。

-

UART 转 AXI4_FULL协议(uart2axi4.v): 它可以从主机 PC 接收 UART 命令,进行 AXI4 总线读写,并将结果反馈给主机 PC。它是调试 SoC 系统的强大工具。

2.推荐原因

UART是常用的调试接口,基础但是重要,AXI是SOC系统互联总线协议,学习该项目可以同时掌握UART协议收发逻辑设计以及AXI4总线协议。

基于ZYNQ的ISP图像处理

引言:

图像信号处理器(Image Signal Processor,简称 ISP)是一种专门用于处理图像信号的芯片或电路模块。

项目链接:

https://github.com/bxinquan/zynq_cam_isp_demo

1.项目描述

基于zynq-7020(正点原子启明星+OV5640)实现了ISP图像处理(将ov5640的ISP关闭,在7020上实现ISP功能),输出到LCD和HDMI。

涉及的处理模块包括坏点校正、黑电平校正、拜耳降噪、数字增益、去马赛克、白平衡增益、色彩校正矩阵、色彩空间转换、Gamma校正、2d降噪、边缘增强。

2.推荐原因

ISP(图像信号处理器)是图像处理的关键组件,负责将传感器的RAW数据转换为高质量的图像。本项目较全面实现了ISP的算法模块,并且这些模块在FPGA板上成功运行,利用FPGA的并行处理能力,显著提升了图像处理的效率和质量。

8701

8701

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?