硬件开发——LPDDR5x

小狼@http://blog.youkuaiyun.com/xiaolangyangyang

1、LPDDR5(x)命令

- DES:deselect

- NOP:no operation

- PDE:power down entry

- ACT-1:activate-1

- ACT-2:activate-2

- PRE:precharg

- REF:refresh

- MWR:mask write

- WR:write

- WR32:write32

- RD:read

- RD32:read32

- CAS:WCK到CK时钟对齐

- MPC:multi purpose command

- SRE:self refresh entry

- SRX:self refresh exit

- MRW-1:mode register write-1

- MRW-2:mode register write-2

- MRR:mode register read

- WFF:write fifo

- RFF:read fifo

- RDC:read DQ calibration

从DDR5开始,地址线总线与命令总线混合编码,ACT指令带有bank地址和row地址,WR/WR32/RD/RD32指令带有column地址。

2、DDR结构

3、模式寄存器

DDR3有4个MR寄存器,DDR5有256个MR寄存器。

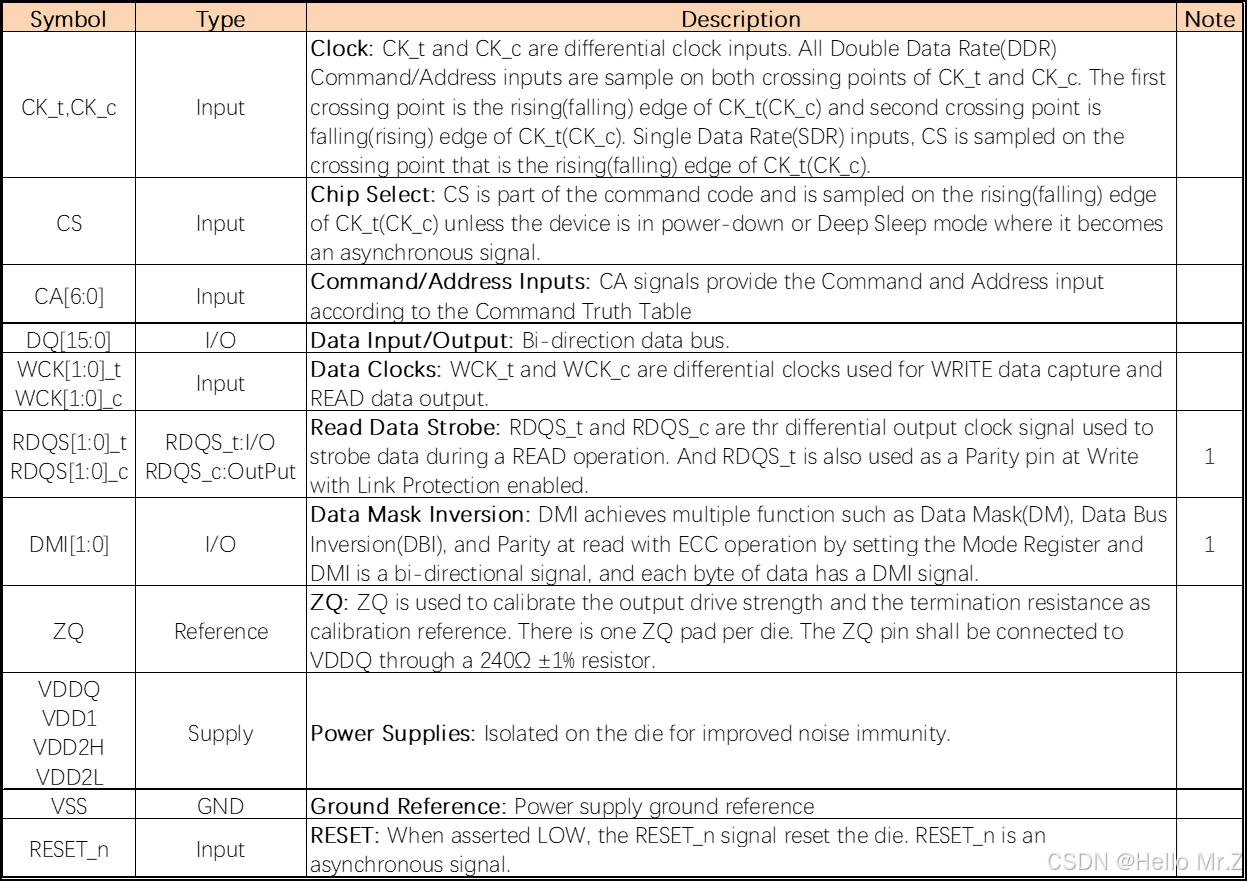

4、LPDDR5(x)芯片引脚定义

5、DDR4/DDR5内存条引脚定义

6、DFI5.1信号定义

7、Training

- CA Training:

- CS Training:

- Write leveling:PCB采用Fly-By拓扑结构时,控制信号与数据信号线长不一致(一般控制信号新更长),用于调整控制信号延时,方法是写DRAM寄存器使其进入training模式(此时DRAM会将CK信号作为数据返回给host),host发出CK和控制信号,读取接收数据是否为1(DRAM回复的CK高电平),如果不是说明控制信号高电平时,CK还未回复,加大CK延时继续测试,直到收到数据为1。涉及到的延时包括tDQSS/tDSS/tDSH/tWLMRD/tWLO/tWLOE。

- VrefCA Training:

- VrefCS Training:

- VrefDQS Training:

8、延时参数

- Xilinx PS使用DDR4需配置的延时参数:tCL/tRCD/tRP/tCWL/tRC/tRAS/tFAW/tAL

- DDR5 write leveling涉及的延时参数:tDQSS/tDSS/tDSH/tWLMRD/tWLO/tWLOE

- Uboot DDR驱动需配置的延时参数:

tREF:内存刷新周期

tCL:CAS延时

tDQSS:写入DQS时间

tMRD:模式寄存器命令时间

tRAS:RAS到预充电延时

tRC:同一bank打开不同Row的最短延时

tRCD:RAS到CAS最小延时

tRFC:自动刷新命令时间

tRP:预充电到RAS延时

tRRD:不同bank打开不同Row的最短延时

tWR:写到预充电延时

tWTR:写到读延时

tXP:退出下电命令时间

tXSR:退出自刷新命令时间

tESR:自刷新命令时间

9、tuning过程

tuning过程使用ddrphy自带的控制器PMU运行tuning固件实现,分为A~K这几个过程:

(A) Bring up VDD, VDDQ, VDD2H and VAA

The first step for initializing the PHY is to apply power. The power supplies can come up and stabilize in any order. While the power supplies are coming up, all outputs will be unknown and the values of the inputs are don't cares. Once the

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1476

1476

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?