名称:序列发生器和序列检测器设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

序列发生器和序列检测器

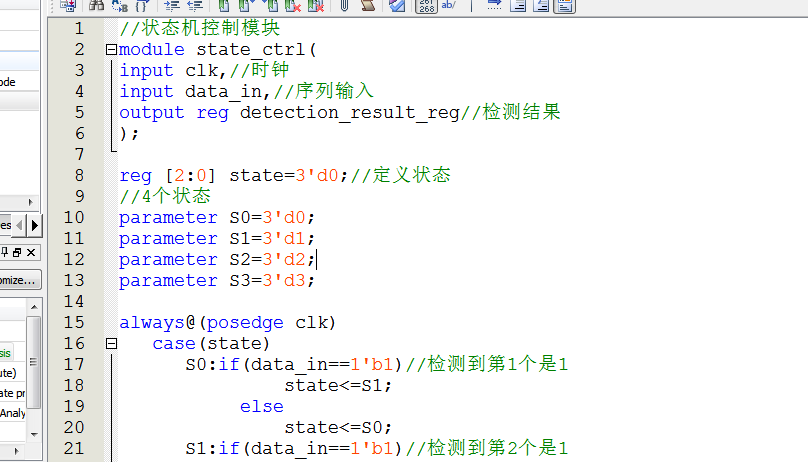

1、使用状态机的方法设计序列检测器,检测“1100”序列

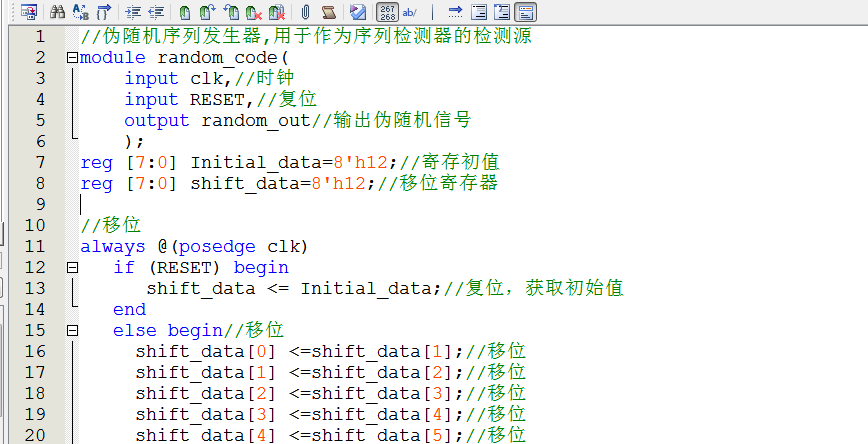

2、设计伪随机序列发生器,用于作为序列检测器的检测源

3、通过触发器输出检测结果

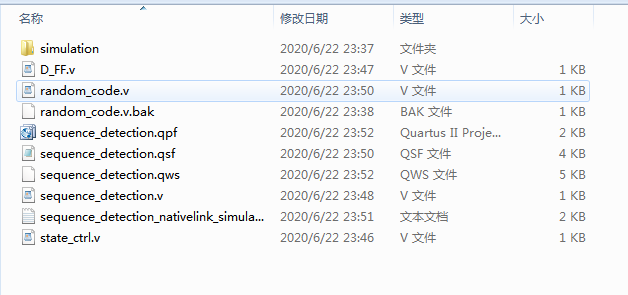

1. 工程文件

2. 程序文件

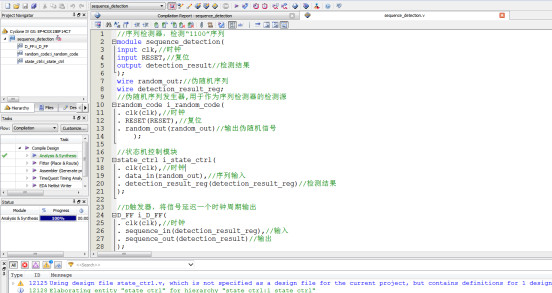

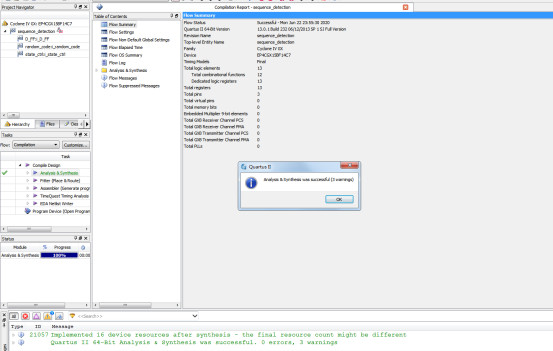

3. 程序编译

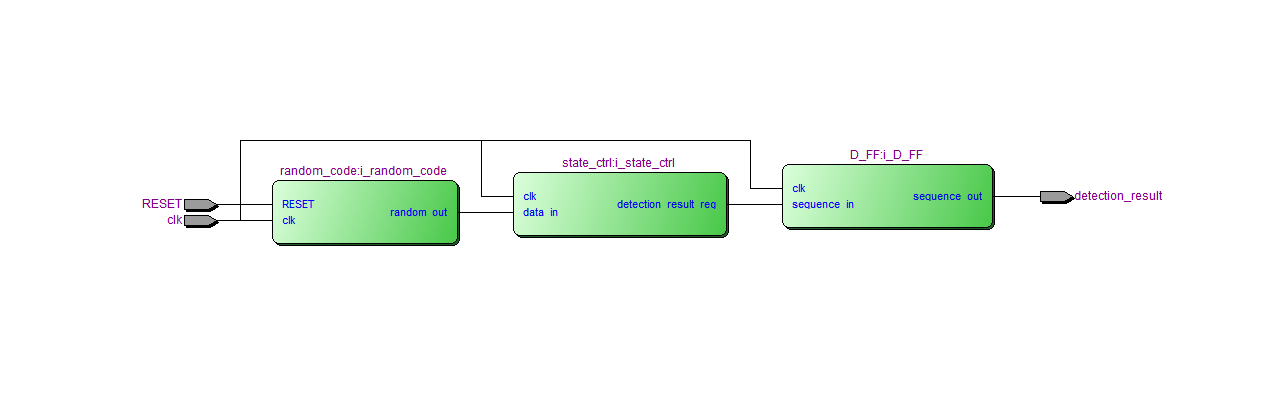

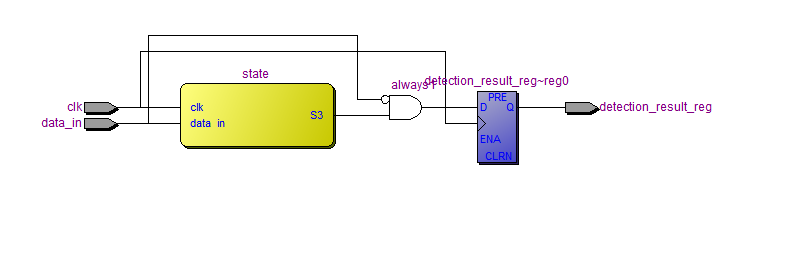

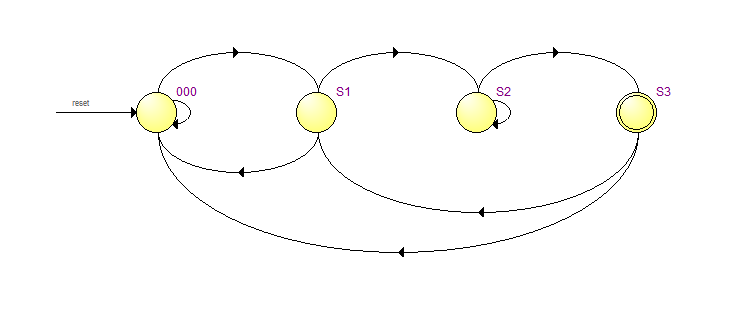

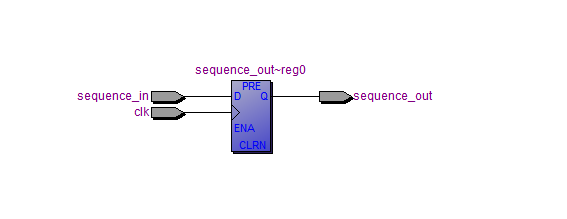

4. RTL图

整体RTL

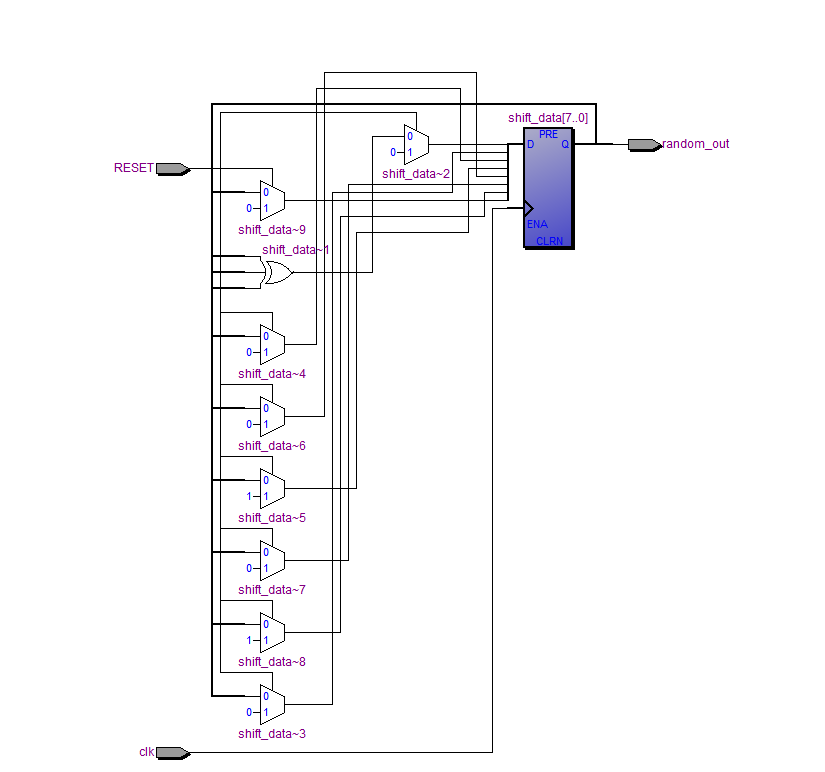

M序列RTL

状态控制模块RTL

状态机视图

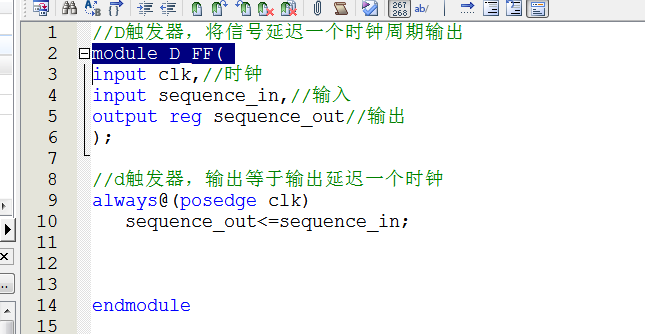

D触发器模块RTL

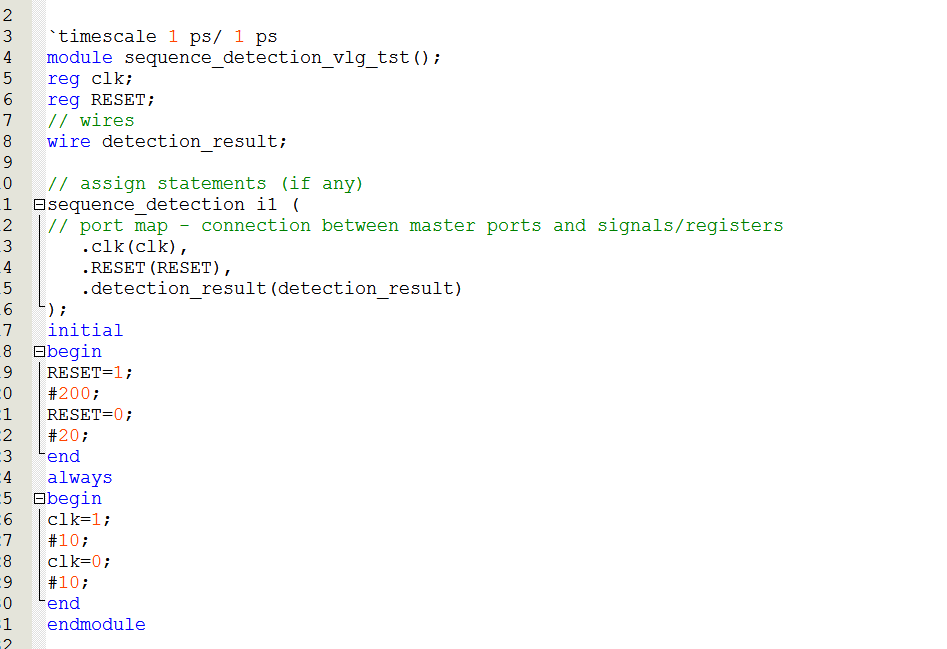

5. Testbench

6. 仿真图

整体仿真

M序列仿真

状态控制模块仿真

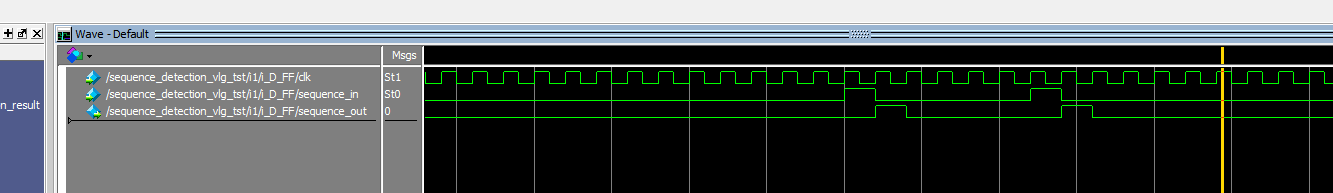

D触发器模块仿真

部分代码展示:

//序列检测器,检测“1100”序列 module sequence_detection( input clk,//时钟 input RESET,//复位 output detection_result//检测结果 ); wire random_out;//伪随机序列 wire detection_result_reg; //伪随机序列发生器,用于作为序列检测器的检测源 random_code i_random_code( . clk(clk),//时钟 . RESET(RESET),//复位 . random_out(random_out)//输出伪随机信号 ); //状态机控制模块 state_ctrl i_state_ctrl( . clk(clk),//时钟 . data_in(random_out),//序列输入 . detection_result_reg(detection_result_reg)//检测结果 );

源代码

点击下方的公众号卡片获取

1722

1722

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?