名称:QPSK调制解调实现设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

QPSK调制解调实现

1、设计正弦波载波模块

2、进行QPSK调制

3、进行QPSK解调,要求解调出的信号与原始信号一致

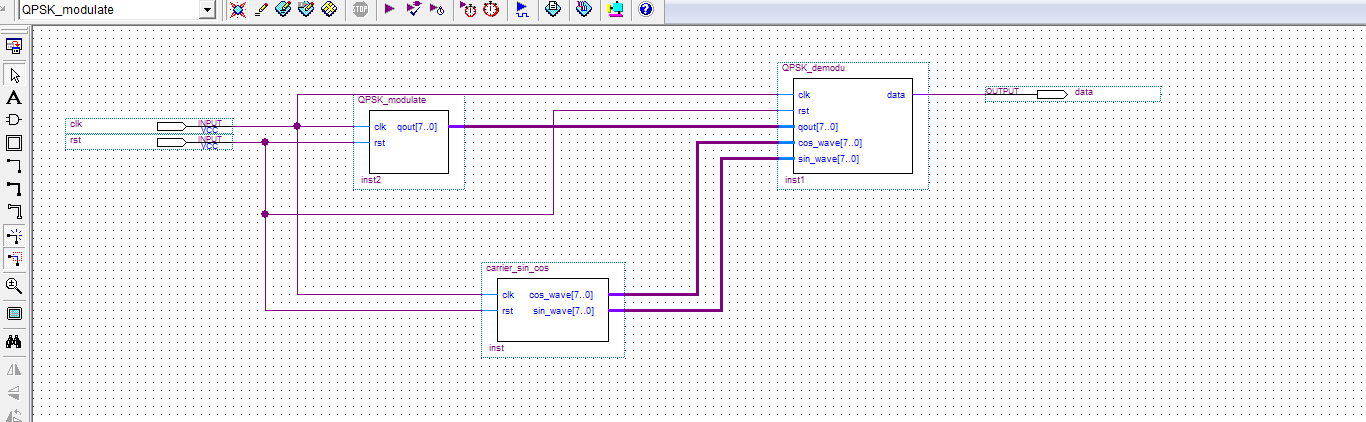

1. 工程文件

quartusII 9.0版本

2. 程序文件

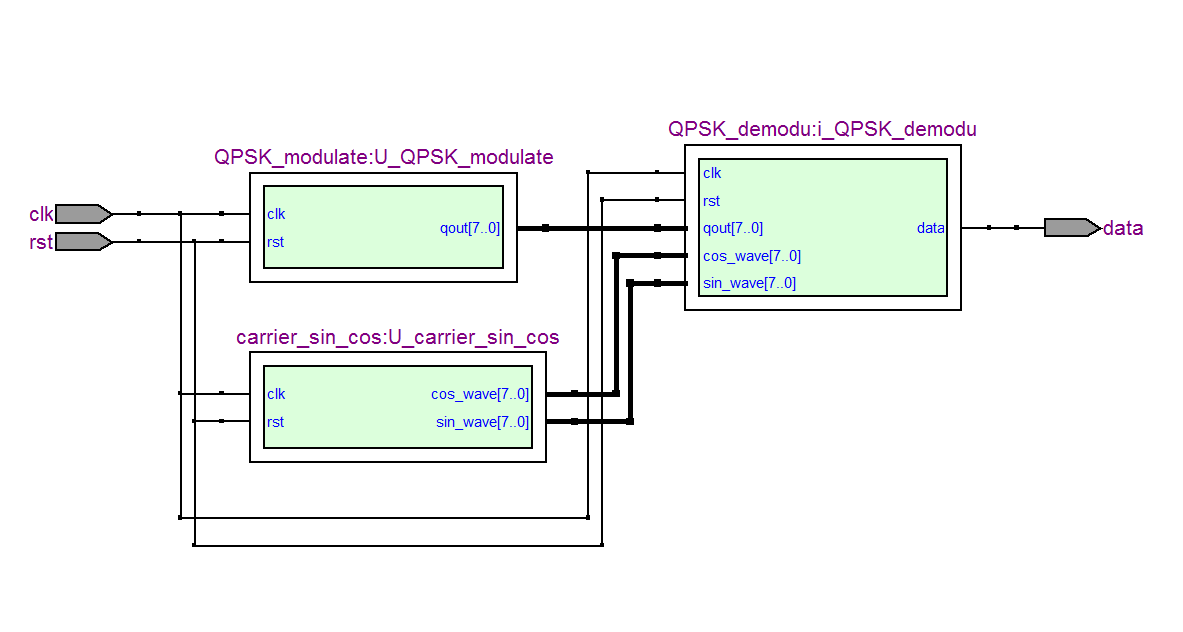

顶层原理图

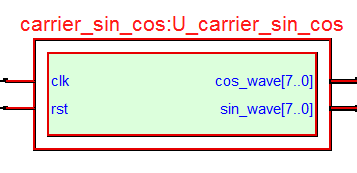

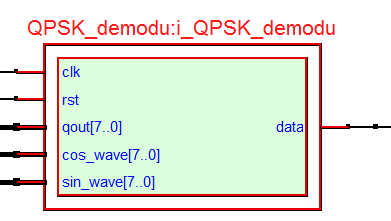

模块框图

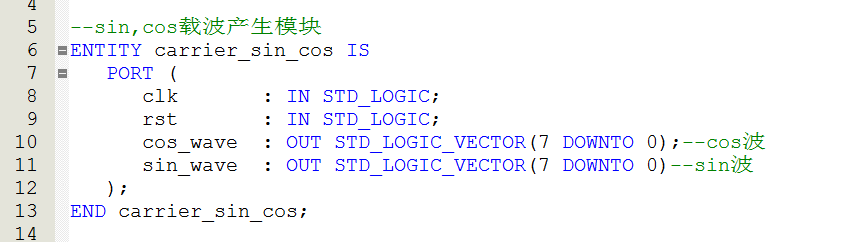

载波模块

解调模块

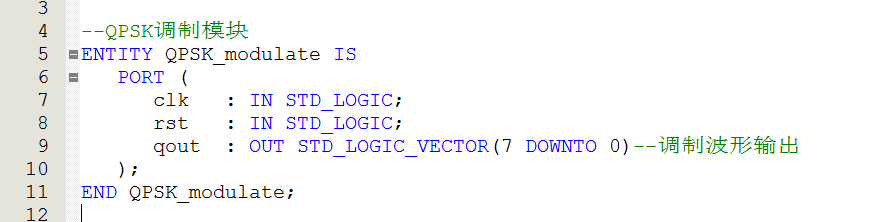

调制模块

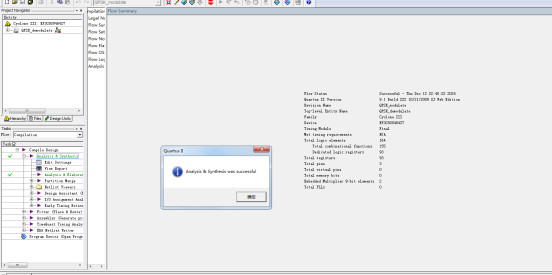

3. 程序编译

4. 程序RTL图

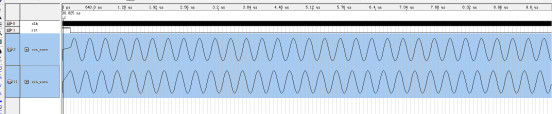

5. 仿真图

5.1 调制模块

5.2 载波产生模块

6.3 解调模块

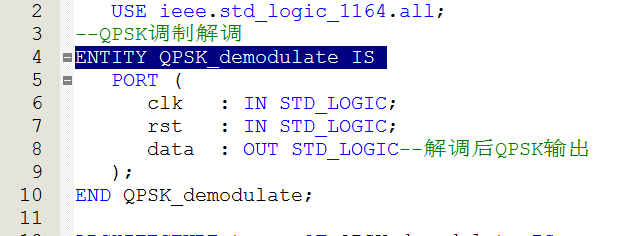

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --sin,cos载波产生模块 ENTITY carrier_sin_cos IS PORT ( clk : IN STD_LOGIC; rst : IN STD_LOGIC; cos_wave : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--cos波 sin_wave : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--sin波 ); END carrier_sin_cos; ARCHITECTURE trans OF carrier_sin_cos IS SIGNAL valu : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000"; SIGNAL count : STD_LOGIC_VECTOR(4 DOWNTO 0) := "00000"; SIGNAL valu_2 : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000"; SIGNAL count_2 : STD_LOGIC_VECTOR(4 DOWNTO 0) := "00000"; BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN IF (rst = '1') THEN count <= "00000"; ELSIF (count = "11111") THEN count <= "00000"; ELSE count <= count + "00001";--波形地址累加器 END IF; END IF; END PROCESS; PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN IF (rst = '1') THEN valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu valu <= "11011010"; END CASE; END IF; END IF; END PROCESS; PROCESS (clk) BEGIN

源代码

点击下方的公众号卡片获取

596

596

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?