名称:12/24小时进制的电子时钟设计Verilog代码Quartus 小梅哥AC620开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

12/24小时进制的电子时钟

1、可以切换12/24小时进制

2、具有调节小时和分钟的按键

3、小时和分钟同时按下秒清零

4、具有整点报时功能

5、数码管显示时分秒

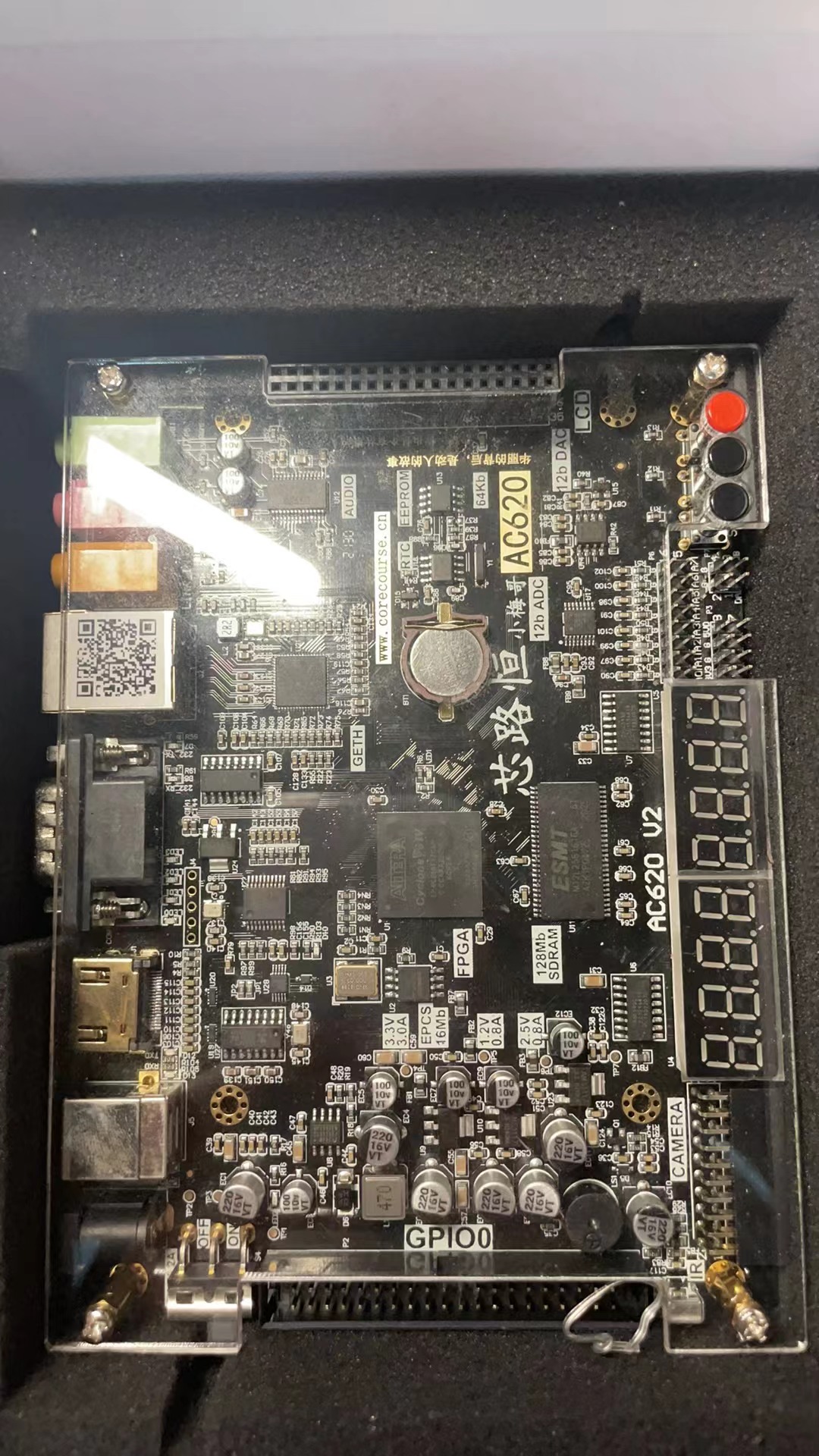

本代码已在小梅哥AC620开发板验证,小梅哥AC620开发板如下,其他开发板可以修改管脚适配:

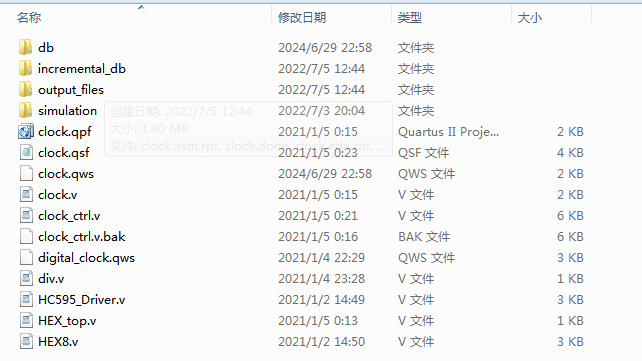

1.工程文件

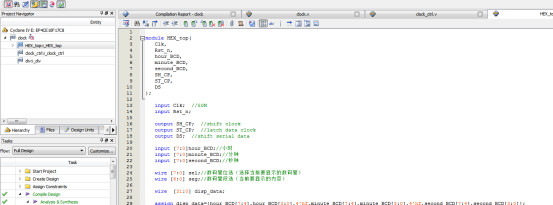

2.程序文件

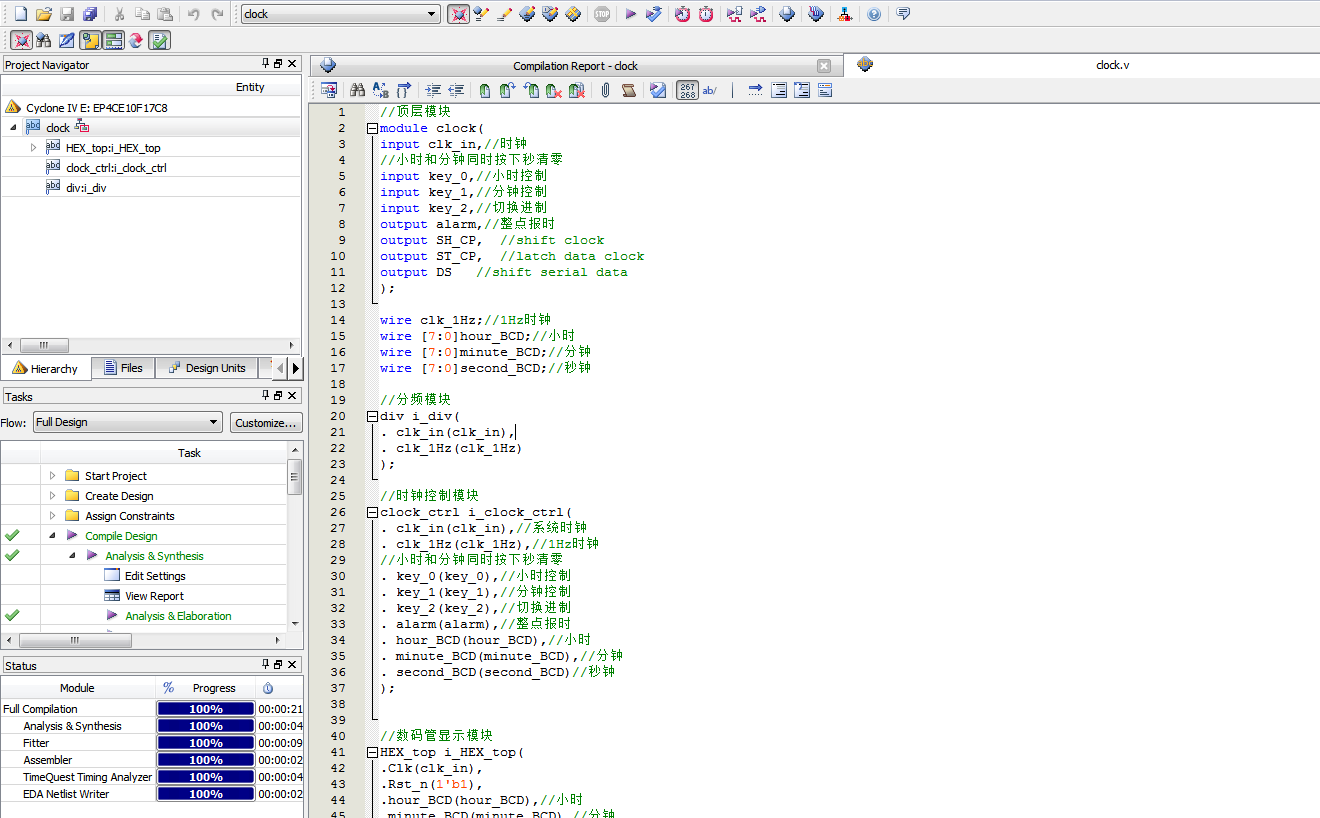

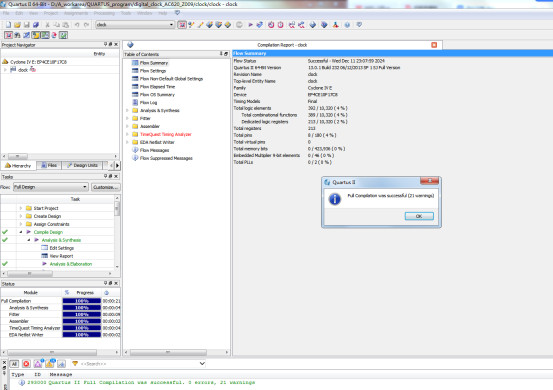

3.程序编译

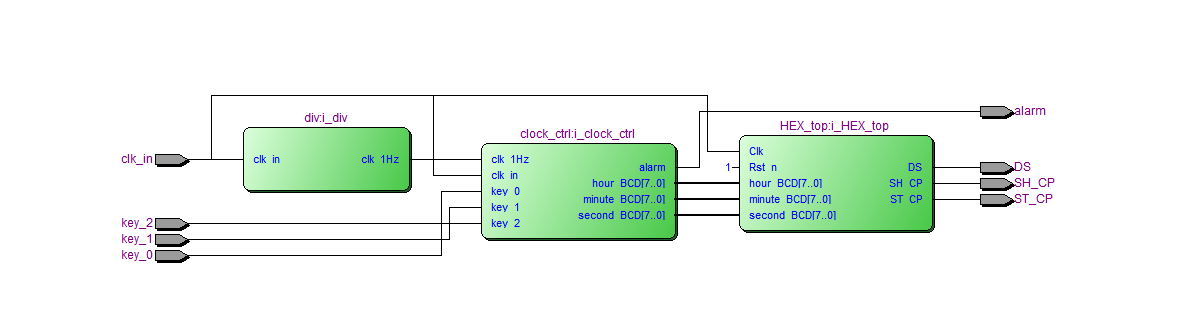

4.RTL图

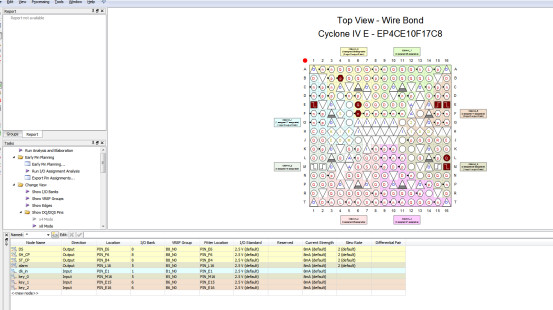

5.管脚分配

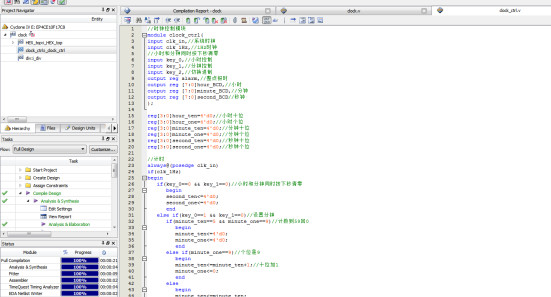

部分代码展示:

//顶层模块 module clock( input clk_in,//时钟 //小时和分钟同时按下秒清零 input key_0,//小时控制 input key_1,//分钟控制 input key_2,//切换进制 output alarm,//整点报时 output SH_CP,//shift clock output ST_CP,//latch data clock output DS//shift serial data ); wire clk_1Hz;//1Hz时钟 wire [7:0]hour_BCD;//小时 wire [7:0]minute_BCD;//分钟 wire [7:0]second_BCD;//秒钟 //分频模块 div i_div( . clk_in(clk_in), . clk_1Hz(clk_1Hz) ); //时钟控制模块 clock_ctrl i_clock_ctrl( . clk_in(clk_in),//系统时钟 . clk_1Hz(clk_1Hz),//1Hz时钟 //小时和分钟同时按下秒清零 . key_0(key_0),//小时控制 . key_1(key_1),//分钟控制 . key_2(key_2),//切换进制 . alarm(alarm),//整点报时 . hour_BCD(hour_BCD),//小时 . minute_BCD(minute_BCD),//分钟 . second_BCD(second_BCD)//秒钟 );

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?