名称:IP核实现fir滤波器设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

IP核实现fir滤波器

设计fir滤波器,使用VIVADO的滤波器IP核,利用fir compiler 实现

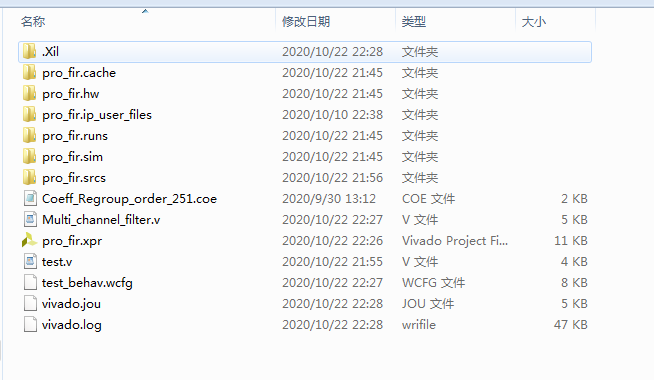

1. 工程文件

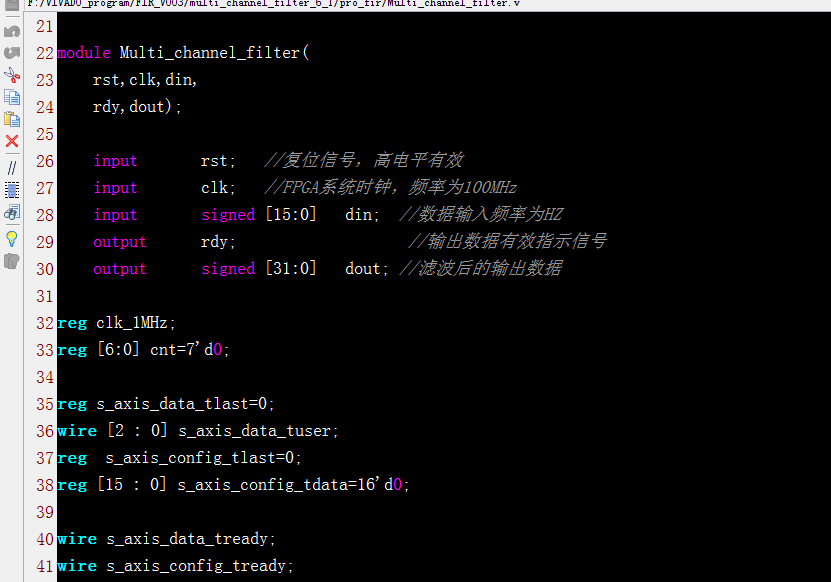

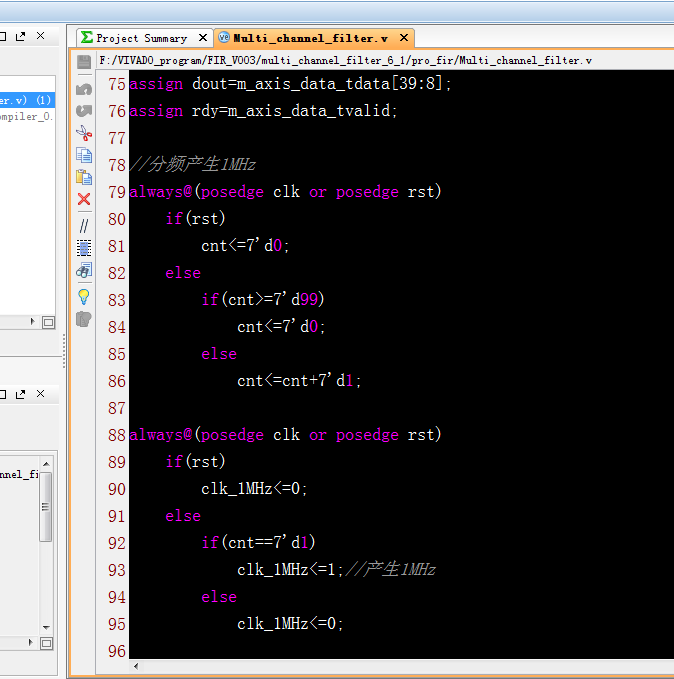

2. 程序文件

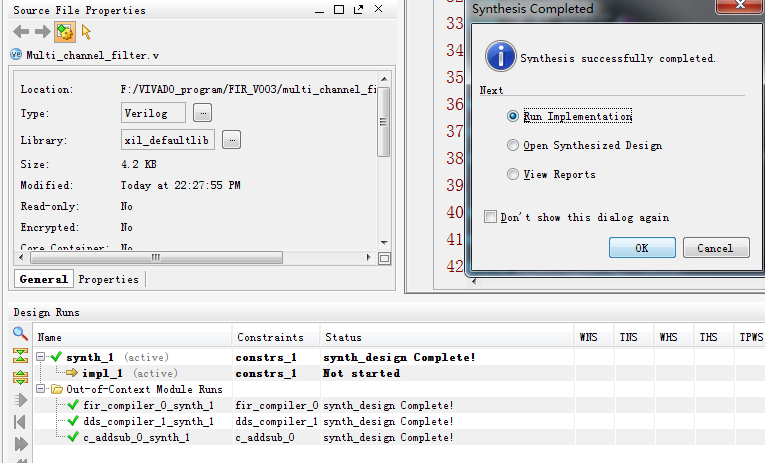

3. 程序编译

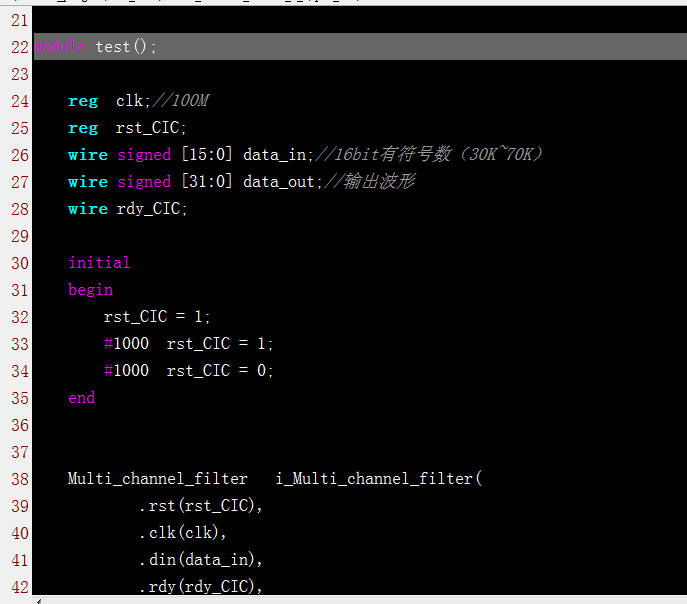

4. Testbench

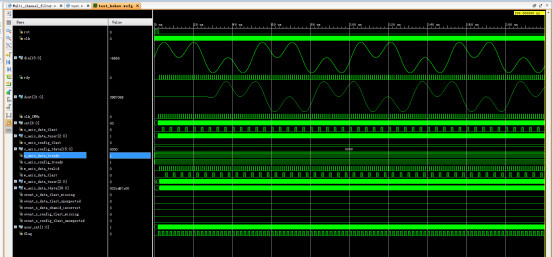

5. 仿真图

附:

调用IP核时的一些技巧

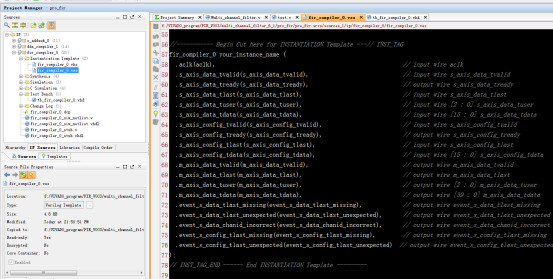

1. 设置完IP核后,点击下图,可以找到软件自动生成的例化代码,可以直接复制到代码中,避免自己写繁琐且易出错。

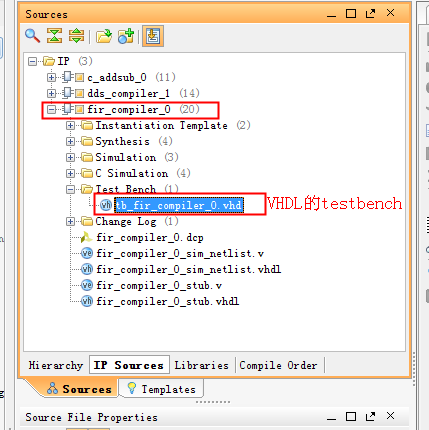

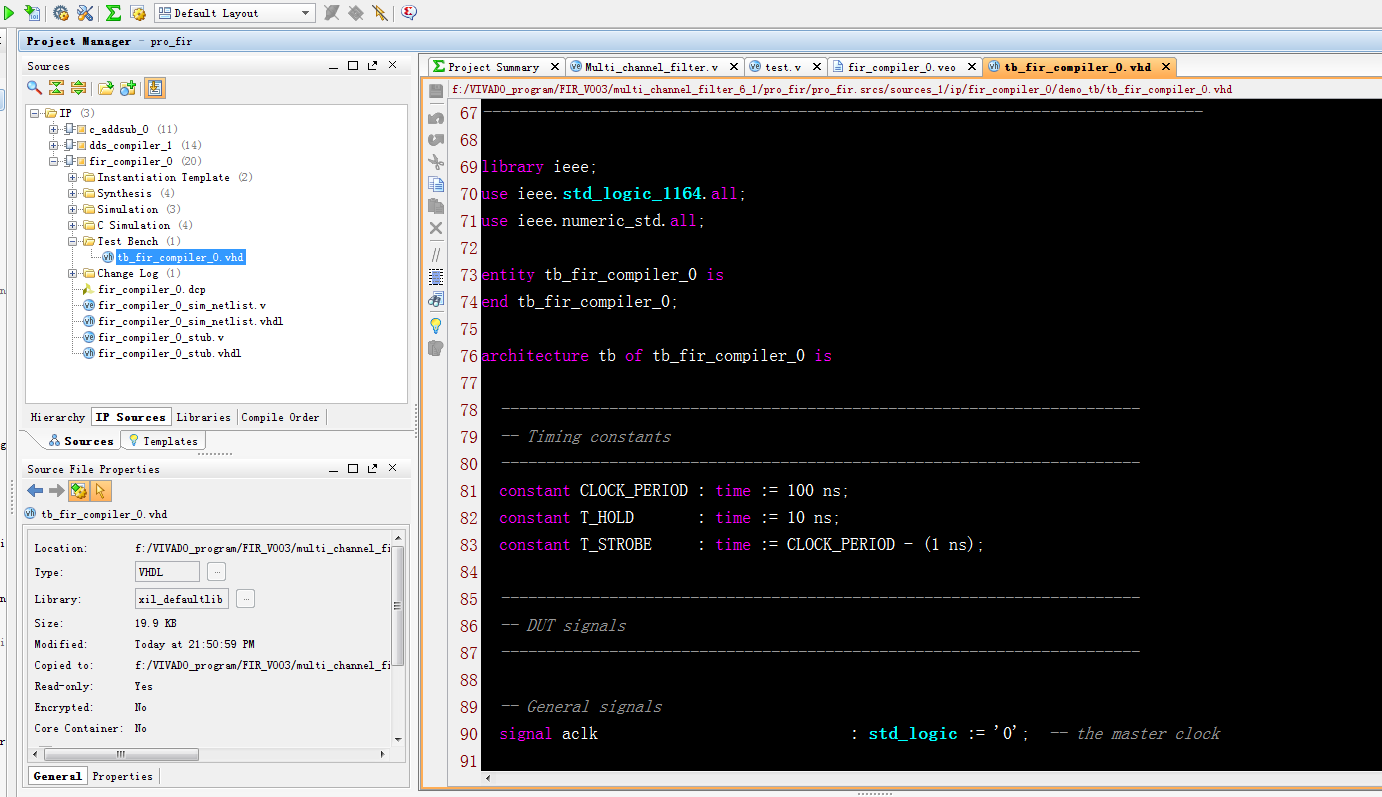

2. Vivado会针对一些IP核自动生成testbench,一般自动生成的testbench是VHDL写的,可以用来参考IP核的时序。如下图

可以新建VHDL的测试文件将自动生成的testbench复制过去,仿真一下看看控制时序。

部分代码展示:

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2020/09/30 05:04:08 // Design Name: // Module Name: Multi_channel_filter // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module Multi_channel_filter( rst,clk,din, rdy,dout); inputrst; //复位信号,高电平有效 inputclk; //FPGA系统时钟,频率为100MHz input signed [15:0]din; //数据输入频率为HZ output rdy; //输出数据有效指示信号 output signed [31:0]dout; //滤波后的输出数据 reg clk_1MHz; reg [6:0] cnt=7'd0; reg s_axis_data_tlast=0; wire [2 : 0] s_axis_data_tuser; reg s_axis_config_tlast=0; reg [15 : 0] s_axis_config_tdata=16'd0; wire s_axis_data_tready; wire s_axis_config_tready; wire m_axis_data_tvalid; wire m_axis_data_tlast; wire [2 : 0] m_axis_data_tuser; wire [39 : 0] m_axis_data_tdata; wire event_s_data_tlast_missing; wire event_s_data_tlast_unexpected; wire event_s_data_chanid_incorrect; wire event_s_config_tlast_missing; wire event_s_config_tlast_unexpected; //调用IP核 fir_compiler_0 i_fir_compiler_0 ( .aclk(clk), // input wire aclk .s_axis_data_tvalid(clk_1MHz), // input wire s_axis_data_tvalid .s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready .s_axis_data_tlast(s_axis_data_tlast), // input wire s_axis_data_tlast .s_axis_data_tuser(s_axis_data_tuser), // input wire [2 : 0] s_axis_data_tuser .s_axis_data_tdata(din), // input wire [15 : 0] s_axis_data_tdata .s_axis_config_tvalid(1'b0), // input wire s_axis_config_tvalid .s_axis_config_tready(s_axis_config_tready), // output wire s_axis_config_tready .s_axis_config_tlast(s_axis_config_tlast), // input wire s_axis_config_tlast .s_axis_config_tdata(s_axis_config_tdata), // input wire [15 : 0] s_axis_config_tdata .m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid .m_axis_data_tlast(m_axis_data_tlast),

源代码

点击下方的公众号卡片获取

3741

3741

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?