名称:可调时分的数字钟设计VHDL代码VIVADO仿真(文末获取)

软件:VIVADO

语言:VHDL

代码功能:

可调时分的数字钟

任务是实现一个数字时钟,在4位7段上显示时间。时钟有两种操作模式:“SET”和“GO”。中央板上的按钮在两者之间切换。在“SET”模式下,允许用户设置初始值以小时和分钟为单位的时间(秒始终为0)。可以使用上下按钮在0到24或0到60的范围内增加或减少小时/分钟。左边和右边按钮可用于切换小时/分钟。如果分钟的当前值与零,按下向上按钮将移动到下一个整数小时数(四舍五入),同时按下向下按钮移动到上一个整数小时数(四舍五入)。在“GO”模式下,计时器应从当前值开始以大约1秒的速率递增。您可以使用7段显示器上的最后一个小数点,用于显示秒计数。

例如,假设计时器当前显示12.07,用户可以设置初始时间至14.06:

a) 按下中央按钮进入“SET”模式;

b) 按左键选择小时

c) 按下顶部按钮显示13.00

d) 按下顶部按钮显示14.00

e) 按右键选择分钟

f) 按下向下按钮显示14.06

g) 按下中央按钮开始计数。然后,显示器应显示序列14.06、14.07...。切换到“SET”模式不应自动将秒数设置为零(重置仅在按下向上/向下时发生),以便可以使用中央按钮暂停和

继续计数。

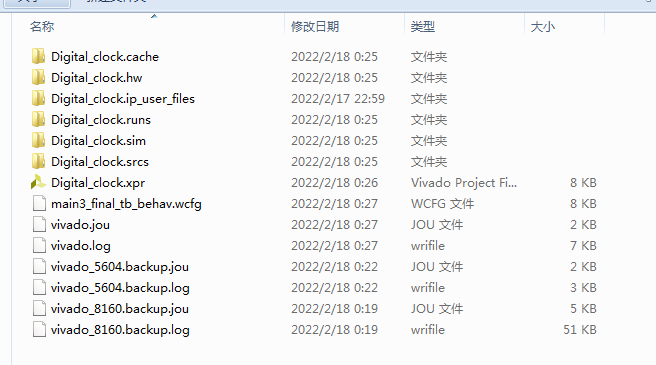

1. 工程文件

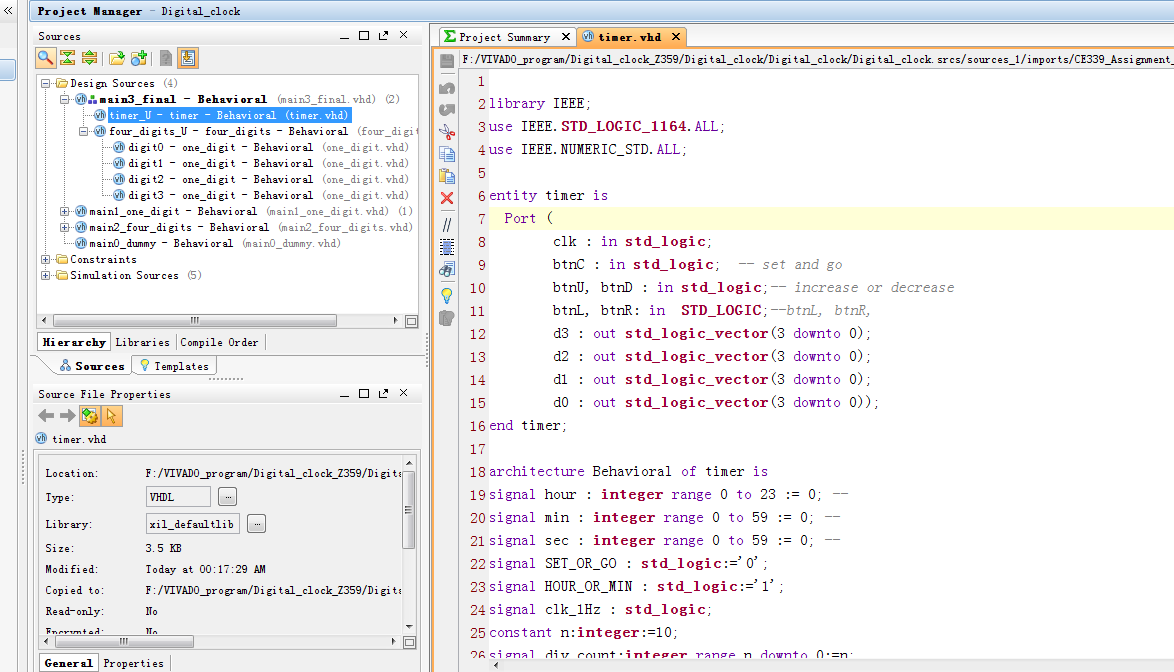

2. 程序文件

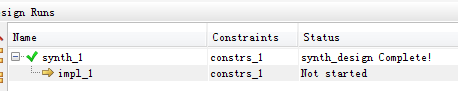

3. 程序编译

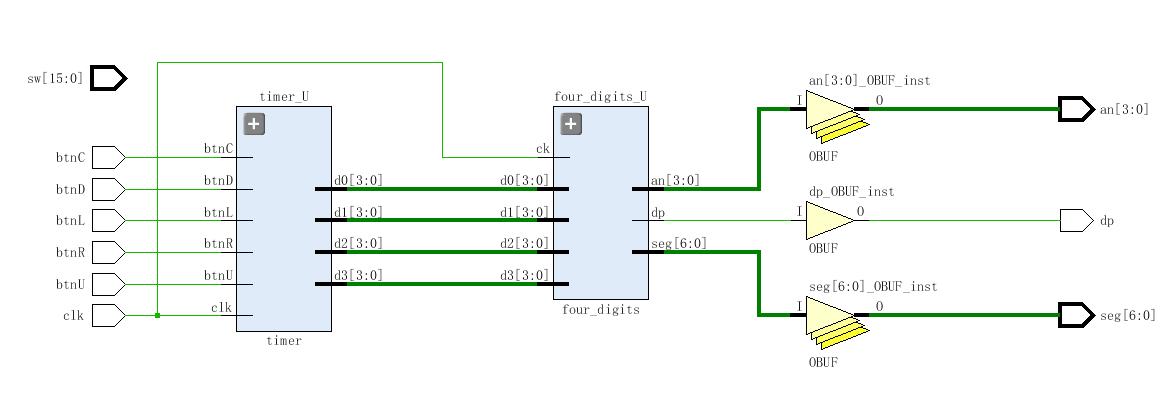

4. RTL图

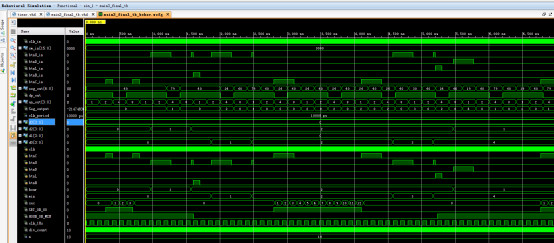

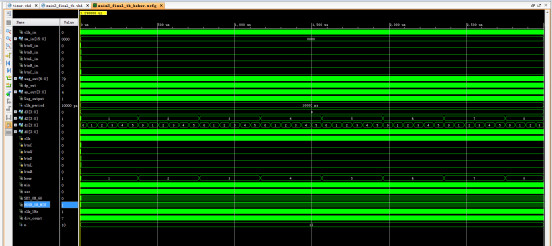

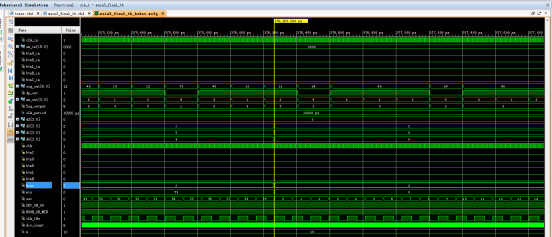

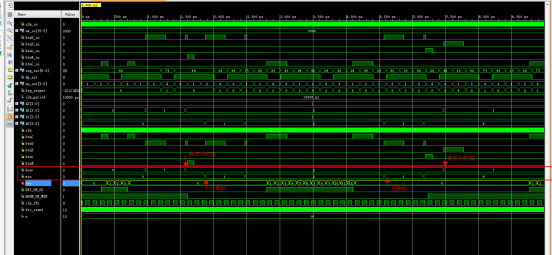

5. 仿真图

部分代码展示:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity main1_one_digit is Port ( sw : in STD_LOGIC_VECTOR (15 downto 0); seg : out STD_LOGIC_VECTOR (6 downto 0); dp : out STD_LOGIC; an : out STD_LOGIC_VECTOR (3 downto 0)); end main1_one_digit; architecture Behavioral of main1_one_digit is begin -- instantiate one one_digit decoder that will decode the active digit one_digit_unit : entity work.one_digit(Behavioral) Port map (digit => sw(3 downto 0), seg => seg); an <= sw(15 downto 12); dp <= sw(5);

源代码

点击下方的公众号卡片获取

244

244

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?