名称:基于FPGA的乘累加模块设计VHDL代码ISE仿真(文末获取)

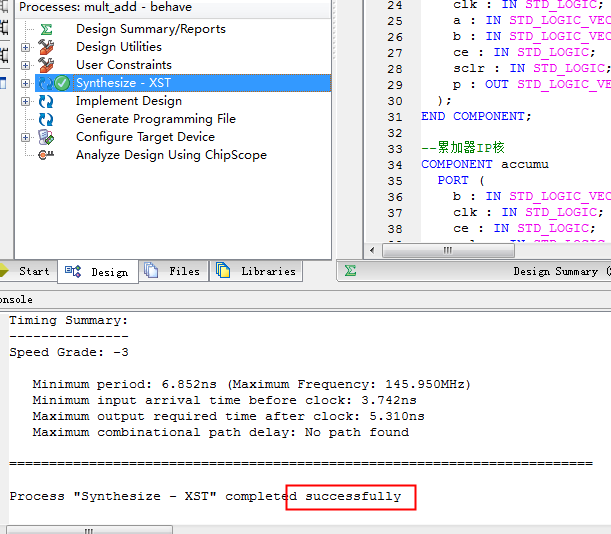

软件:ISE

语言:Verilog

代码功能:

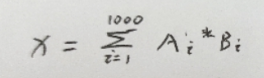

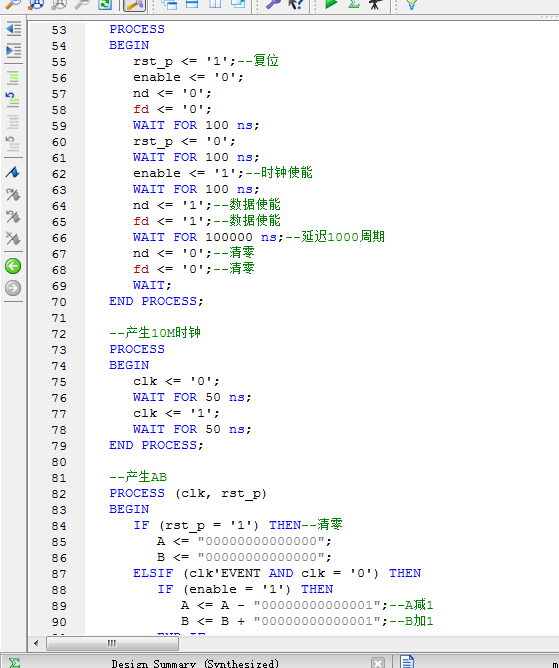

乘累加模块

A.B分别输入两种正弦波形

在1000个时钟周期对AB同时采样样并计算

控制要求:存在时钟使能信号和复位信号且当控制信号nd,fd同时为“1”时模块运行,运行完成后,rdy返回“1”

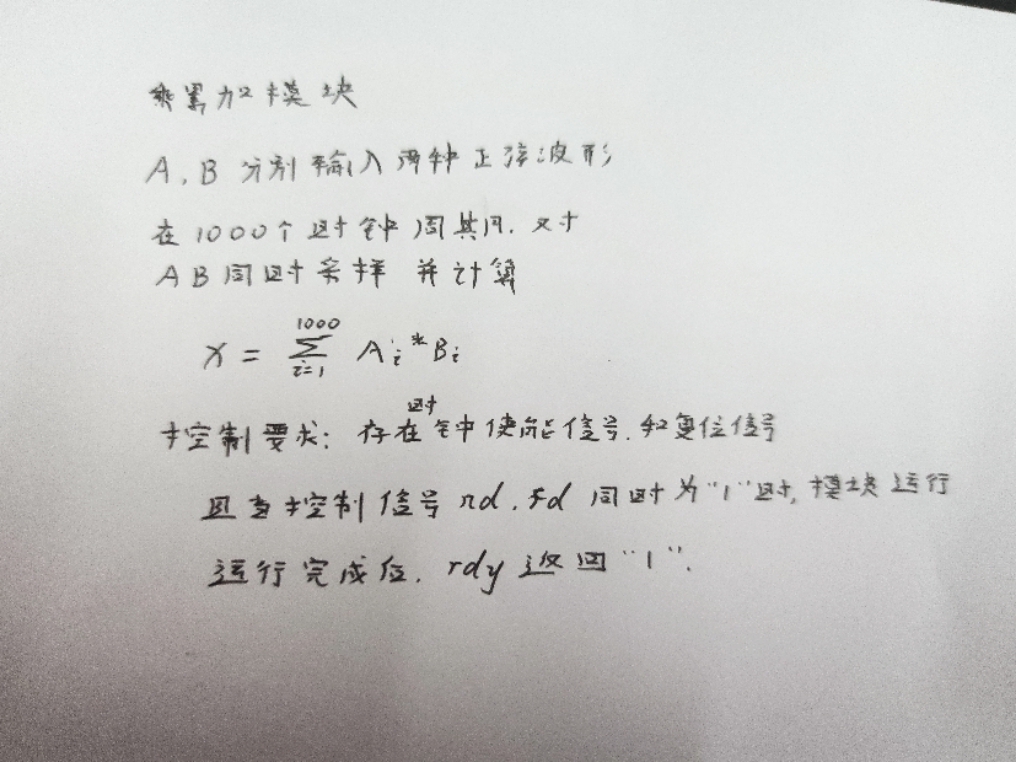

1. 工程文件

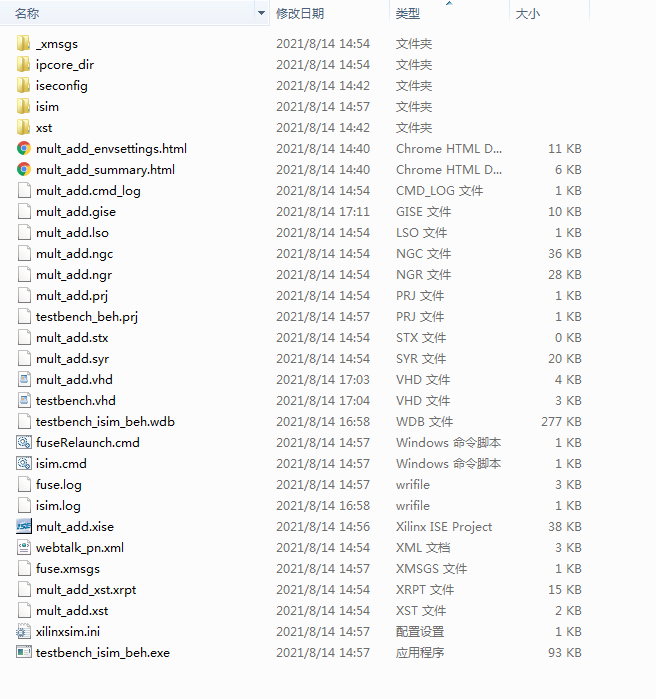

2. 程序文件

3. 程序编译

4. Testbench

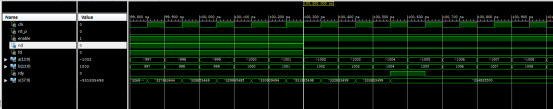

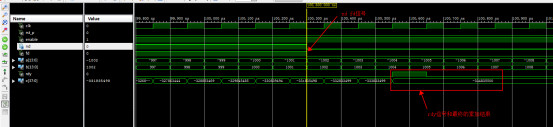

5. 仿真图

部分代码展示:

module mult_add( input clk,//10M input rst_p, input enable, input nd,fd, input [13:0]A, input [13:0]B, output rdy, output [37:0]X ); reg ce; reg [9:0] count=10'd0; always@(posedge clk or posedge rst_p) if(rst_p) count<=10'd0; else if(enable)begin if(nd & fd) if(count>10'd1000) count<=count; else count<=count+10'd1; else count<=10'd0; end else count<=count; always@(posedge clk) if(count>0 && count<=1000) ce<=1; else ce<=0; reg [13:0]A_buf0; reg [13:0]B_buf0; reg [13:0]A_buf1; reg [13:0]B_buf1;

源代码

扫描文章末尾的公众号二维码

2774

2774

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?