目录

文章总目录请点这里:《FPGA接口与协议》专栏的说明与导航

1、框架

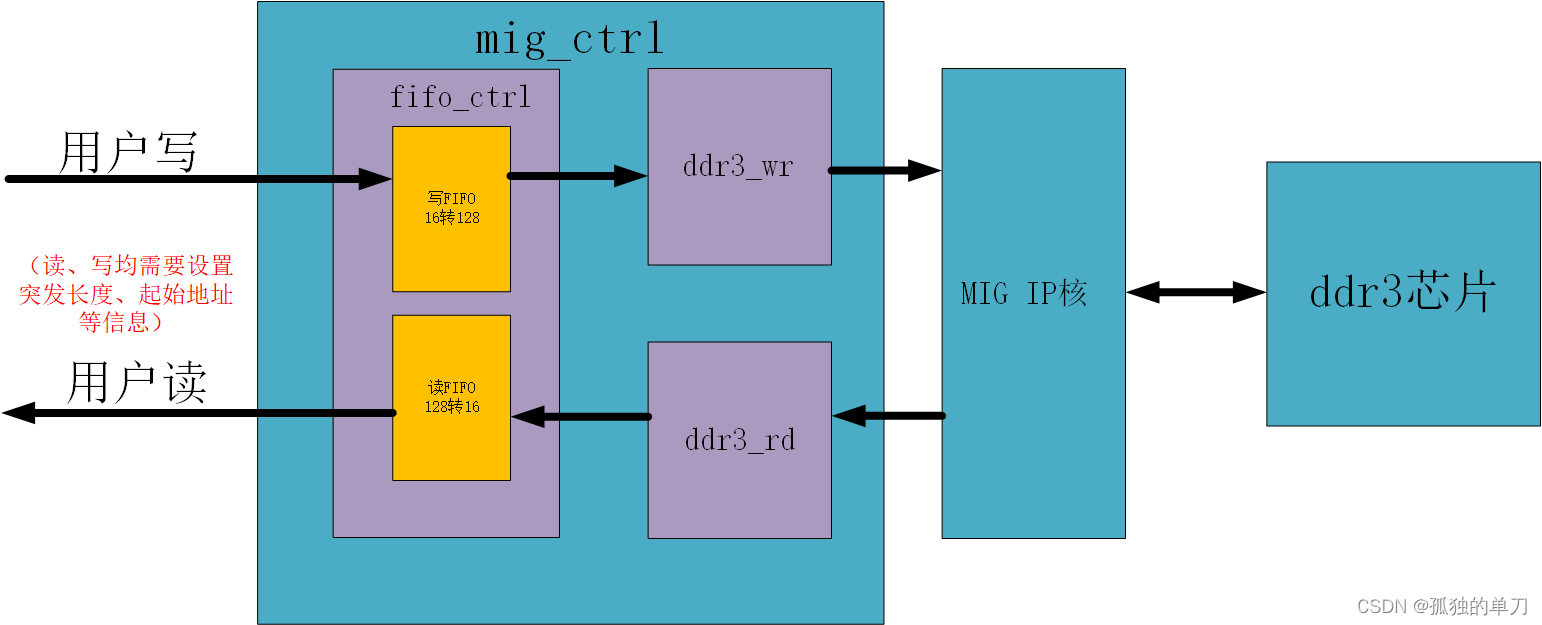

这个类FIFO模块主要由以下几个部分组成:

mig_ctrl:顶层模块,使用该模块通过控制MIG IP核间接实现对DDR3芯片的突发写、突发读。分为用户接口与DDR3控制接口,用于只需要控制用户接口即可实现对DDR3芯片的突发写、突发读。用户接口的应用类似FIFO接口,用户只需要提供写使能信号与写入的数据即可实现突发写操作(实际上还需要提供其他信息:如突发长度、起止地址等信息);用户只需要提供读使能信号即可实现突发读操作(实际上还需要提供其他信息:如突发长度、起止地址等信息)。

该博客介绍了如何将Xilinx DDR3 MIG IP核封装成类FIFO模块,实现突发写和突发读操作。通过写FIFO和读FIFO缓存数据,控制MIG IP进行DDR3的突发读写,详细阐述了突发写模块ddr3_wr和突发读模块ddr3_rd的工作原理,并提供了Testbench的仿真结果以验证设计的正确性。

该博客介绍了如何将Xilinx DDR3 MIG IP核封装成类FIFO模块,实现突发写和突发读操作。通过写FIFO和读FIFO缓存数据,控制MIG IP进行DDR3的突发读写,详细阐述了突发写模块ddr3_wr和突发读模块ddr3_rd的工作原理,并提供了Testbench的仿真结果以验证设计的正确性。

订阅专栏 解锁全文

订阅专栏 解锁全文

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?