个人在使用hls生成IP核时,并没有出现报错的问题,当我将自己的IP加入到vivado block design时,综合也并没有任何的问题出现,但当跑到implementation时,出现以下的一些错误,

[DRC REQP-21] enum_AREG_2_connects_CEA1_GND_connects_CEA2_GND_connects_CEA1_connects_CEA2: (马赛克…)mfYi_DSP48_2_U/p: When the DSP48E1 AREG attribute is set to 2, the CEA1 and CEA2 input pins cannot be unconnected or tied to GND.

一开始我也很疑惑HLS明明编译过了怎么还会有IP核出现问题,

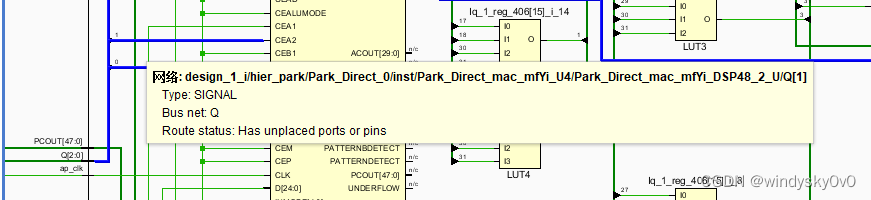

可以看到这里的布线提示没有链接,这就很奇怪了。

现在问题解决了,是采用的HLS封装的IP核出现的问题。封装时我选择的主控芯片是zynq-7030,但是到使用时我这个工程是zynq-7045的,重新封装后就解决了。(PS. 我使用其他的IP核封装时主控为7010,但用在7045上却没报错,蛮奇怪的)。

vivado design initialization error

这是另外出现的一个问题。本来工程跑的好好的,当我更改了一个IP核后从新运作工程时出现了这个错误。这个错误出现在开始跑opt—design的时候,但很奇怪的是,error没有任何提示以及编号,为此我尝试过reset project,但是并没有什么用。

解决:我关闭工程后,将runs文件夹下的impl文件删除,让工程重新编译一次,终于通过了,之前网上和xilinx 社区都没有提到,所以记录下。

在使用HLS生成的IP核集成到Vivadoblockdesign中,虽然编译和综合无误,但在implementation阶段遇到[DRCREQP-21]错误,提示DSP48E1的CEA1和CEA2输入引脚不能未连接或接地。问题根源在于HLS封装时使用的主控芯片型号(Zynq-7030)与实际工程中的芯片型号(Zynq-7045)不匹配。重新封装IP核以匹配7045后,问题得到解决。另外,同样的IP核在7010上使用却未报错,显示了芯片间兼容性的差异。

在使用HLS生成的IP核集成到Vivadoblockdesign中,虽然编译和综合无误,但在implementation阶段遇到[DRCREQP-21]错误,提示DSP48E1的CEA1和CEA2输入引脚不能未连接或接地。问题根源在于HLS封装时使用的主控芯片型号(Zynq-7030)与实际工程中的芯片型号(Zynq-7045)不匹配。重新封装IP核以匹配7045后,问题得到解决。另外,同样的IP核在7010上使用却未报错,显示了芯片间兼容性的差异。

977

977

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?