一、学习内容

1.超前进位加法器

利用组合逻辑算出每一位进位,因为计算公式中的变量都是已知输入,故可以无延时得到每一位的进位结果,提高电路频率,但会增加电路面积。

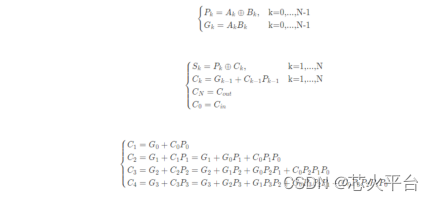

以四位超前进位为例,其进位以及和的结果计算逻辑公式如下:

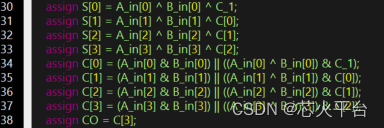

反映到代码如下:

2.时序约束

2.1.系统时钟约束

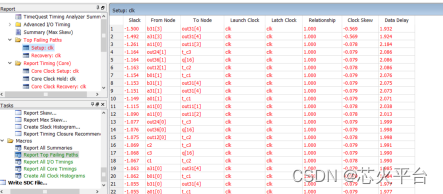

a.编译完工程后点击时序仿真,再创建时序网表

此时未对时钟进行约束,其默认为1000Mhz时钟,可以看到其建立时间已经违规。

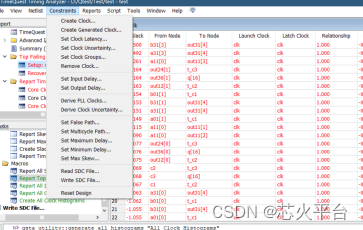

b.创建约束时钟

点击第一个,即可对我们设计的时钟进行约束

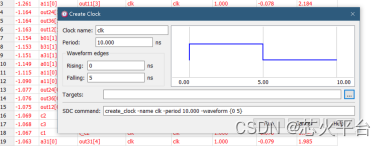

命名好时钟名字,设置好周期与占空比分别为10ns和50%,对应100Mhz频率

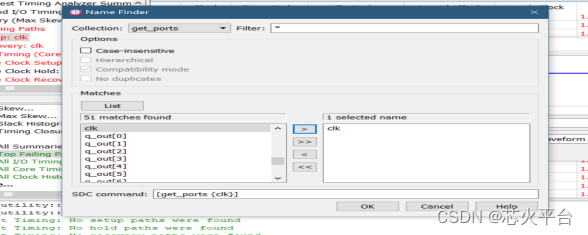

绑定好设计需要约束的时钟

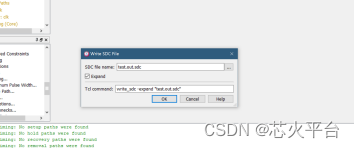

保存时序约束文件并加入设计项目中

约束文档中标明了时序约束具体内容,可以更改

本文介绍了FPGA开发中的超前进位加法器原理,详细讲解了时序约束的各个方面,包括系统时钟约束、时钟延迟和不确定性约束,以及如何处理握手信号。此外,还探讨了AXI4协议的基础概念和读写操作流程。

本文介绍了FPGA开发中的超前进位加法器原理,详细讲解了时序约束的各个方面,包括系统时钟约束、时钟延迟和不确定性约束,以及如何处理握手信号。此外,还探讨了AXI4协议的基础概念和读写操作流程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?