1.总线适配器 寄存器模型生成时并不随之生成adapter,因为adapter的转换上层是UVM的寄存器标准包,转换下层可能是不同的总线UVC(比如ahb apb 的VIP),所以adapter的开发责任就落到总线UVC上(上层是寄存器模型块,发出的数据位宽等等可能跟标准总线的不一样,所以就要有adapter)

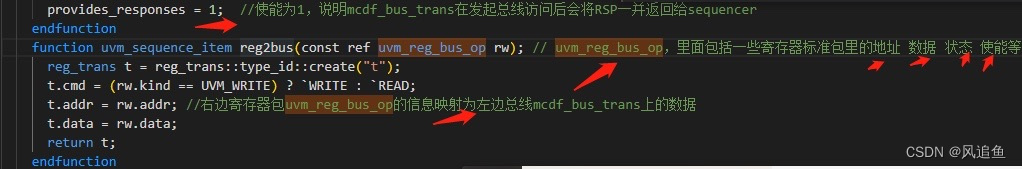

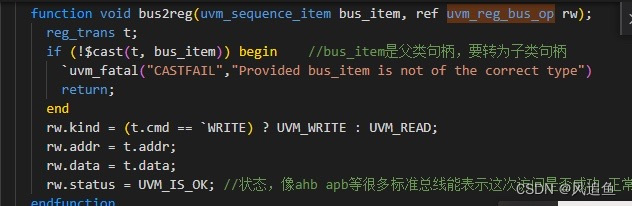

2.寄存器序列将带有目标寄存器的相关信息存储到uvm_reg_item实例中,送往adapter,adapter接收到uvm_reg_item后,从中抽取总线UVC需要的信息,生成总线UVC需要的bus_trans_item送往总线UVC

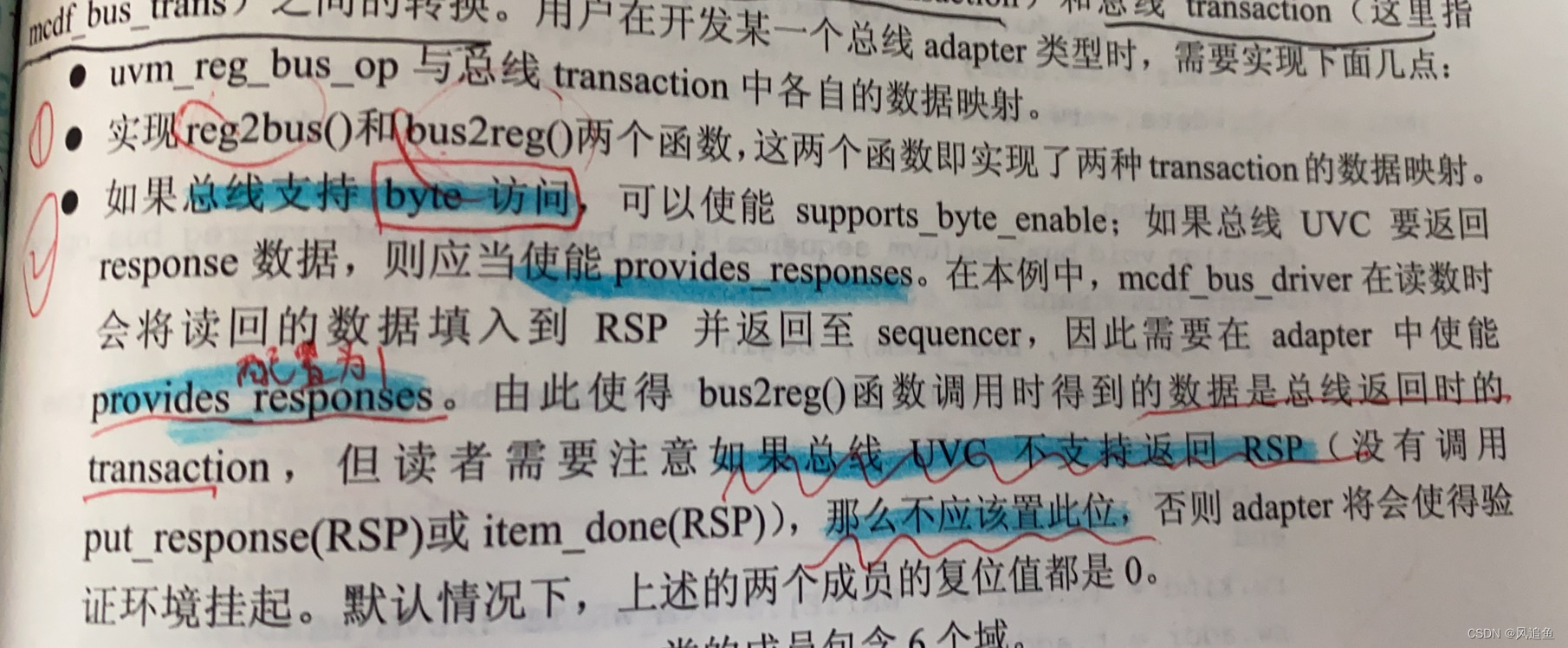

3.adapter要实现2个函数,并且如果总线支持返回RSP,则要在adapter中使能provide_responses

4513

4513

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?