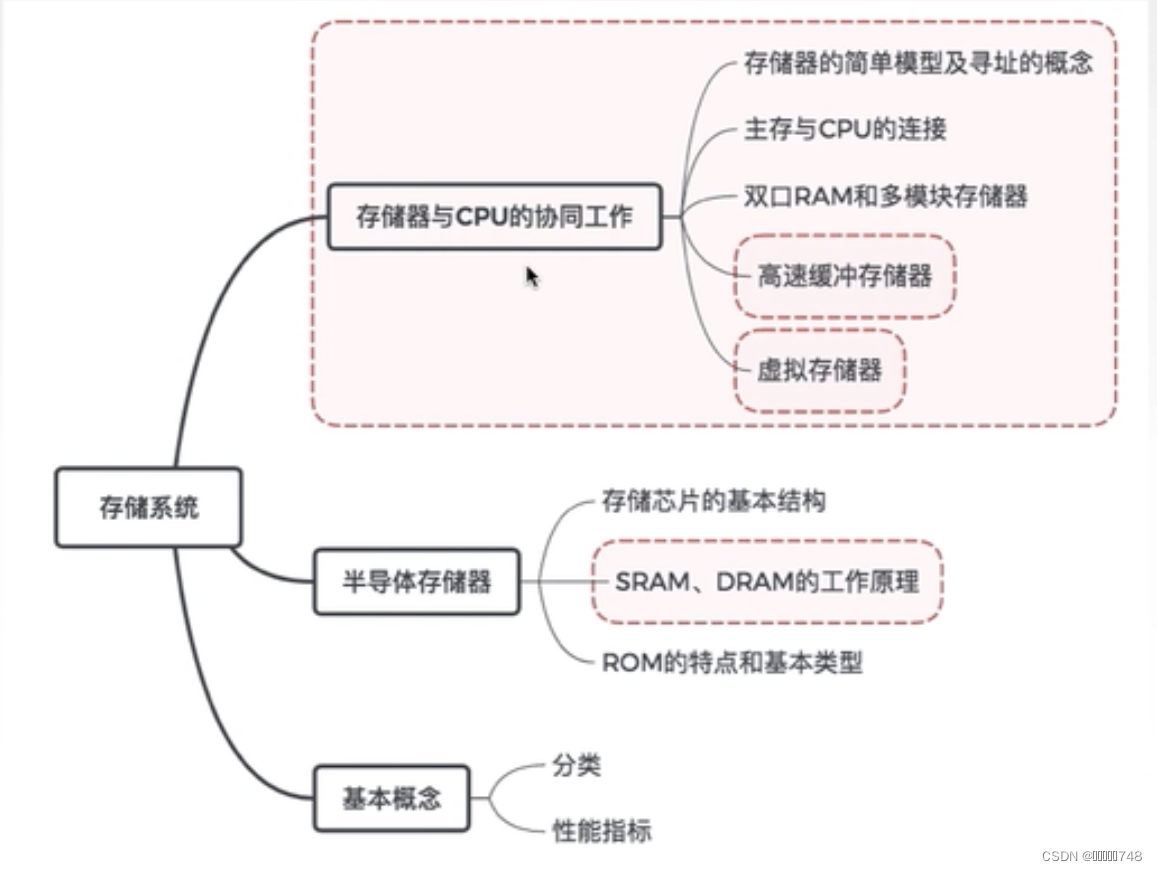

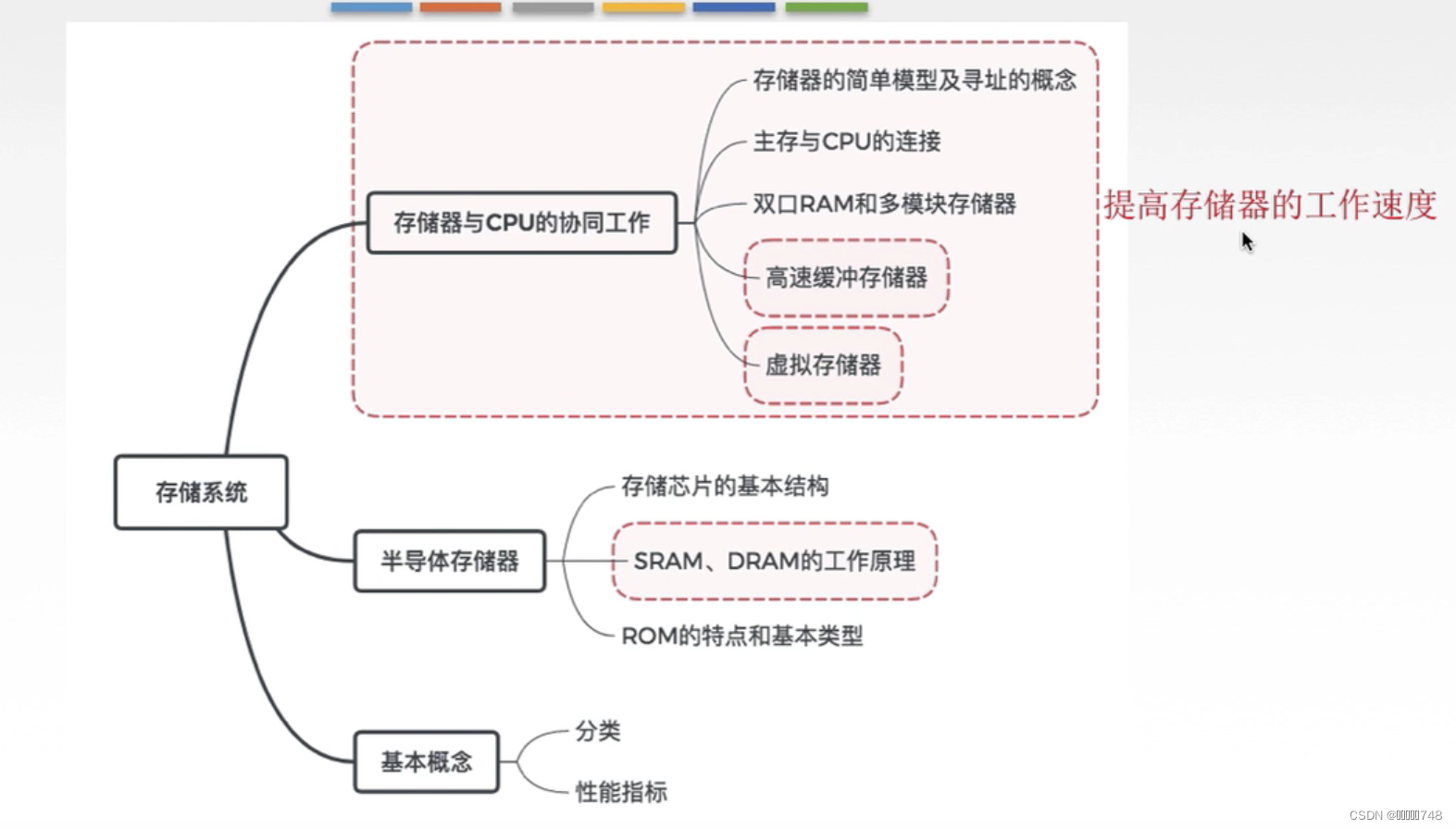

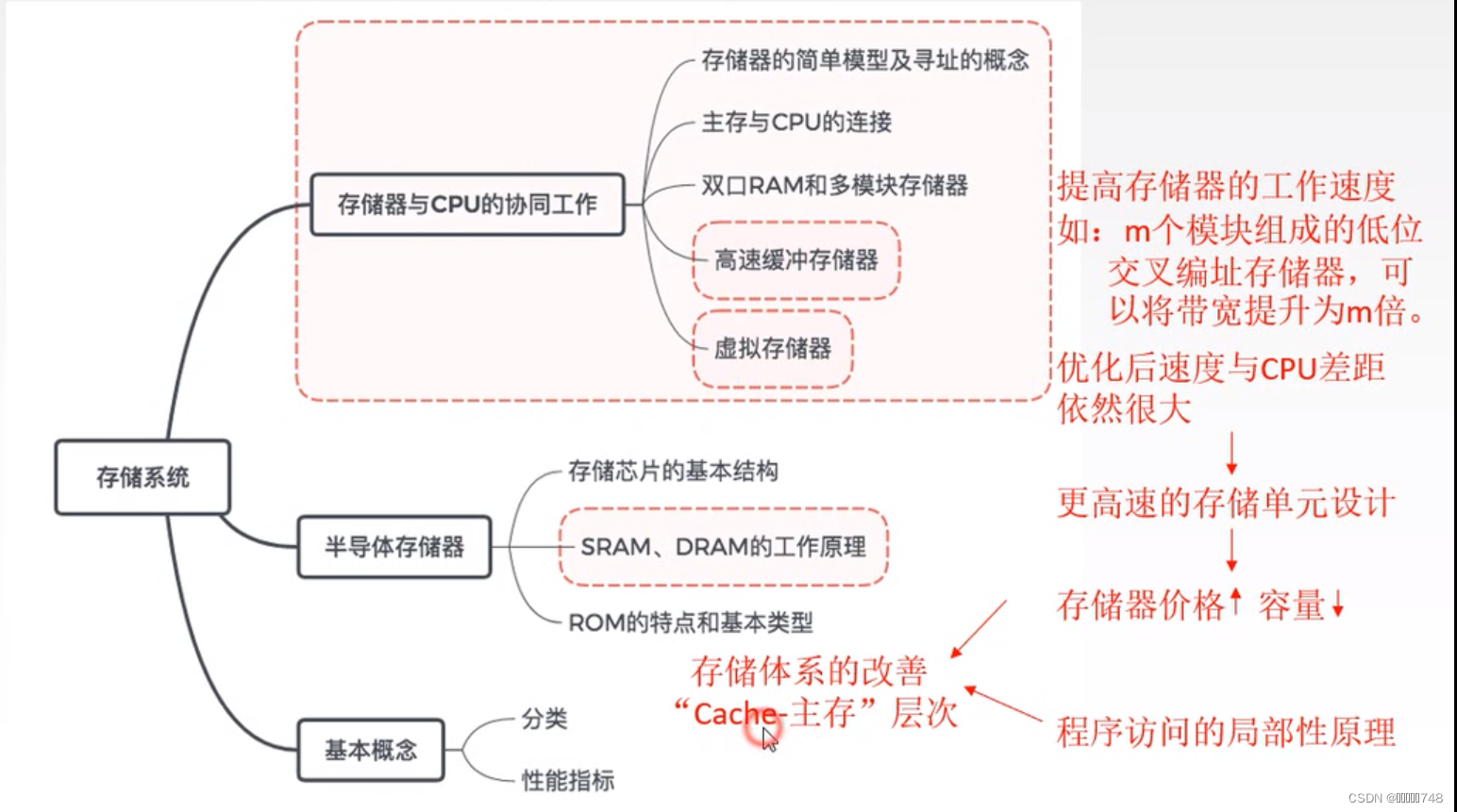

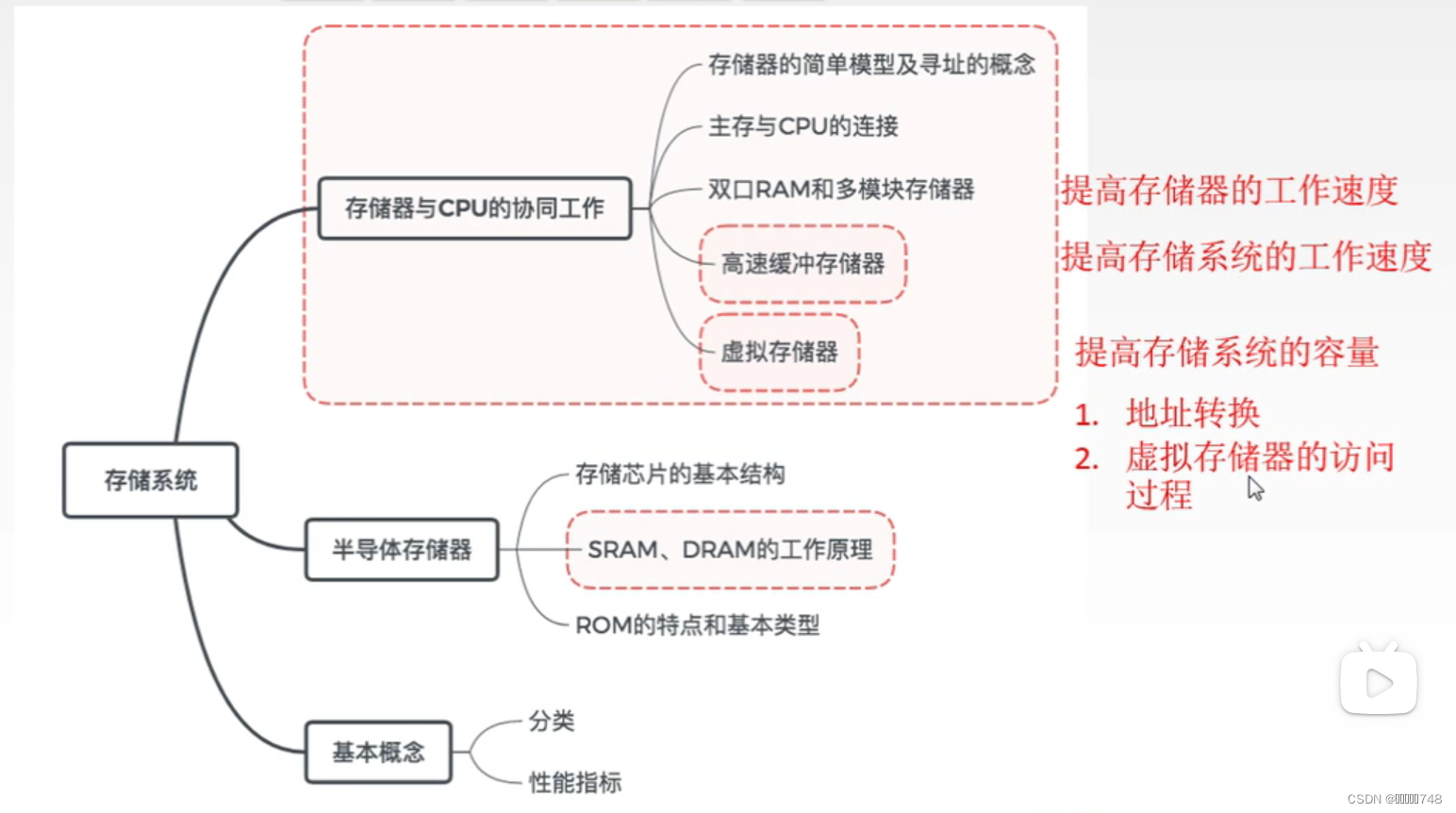

章节总览

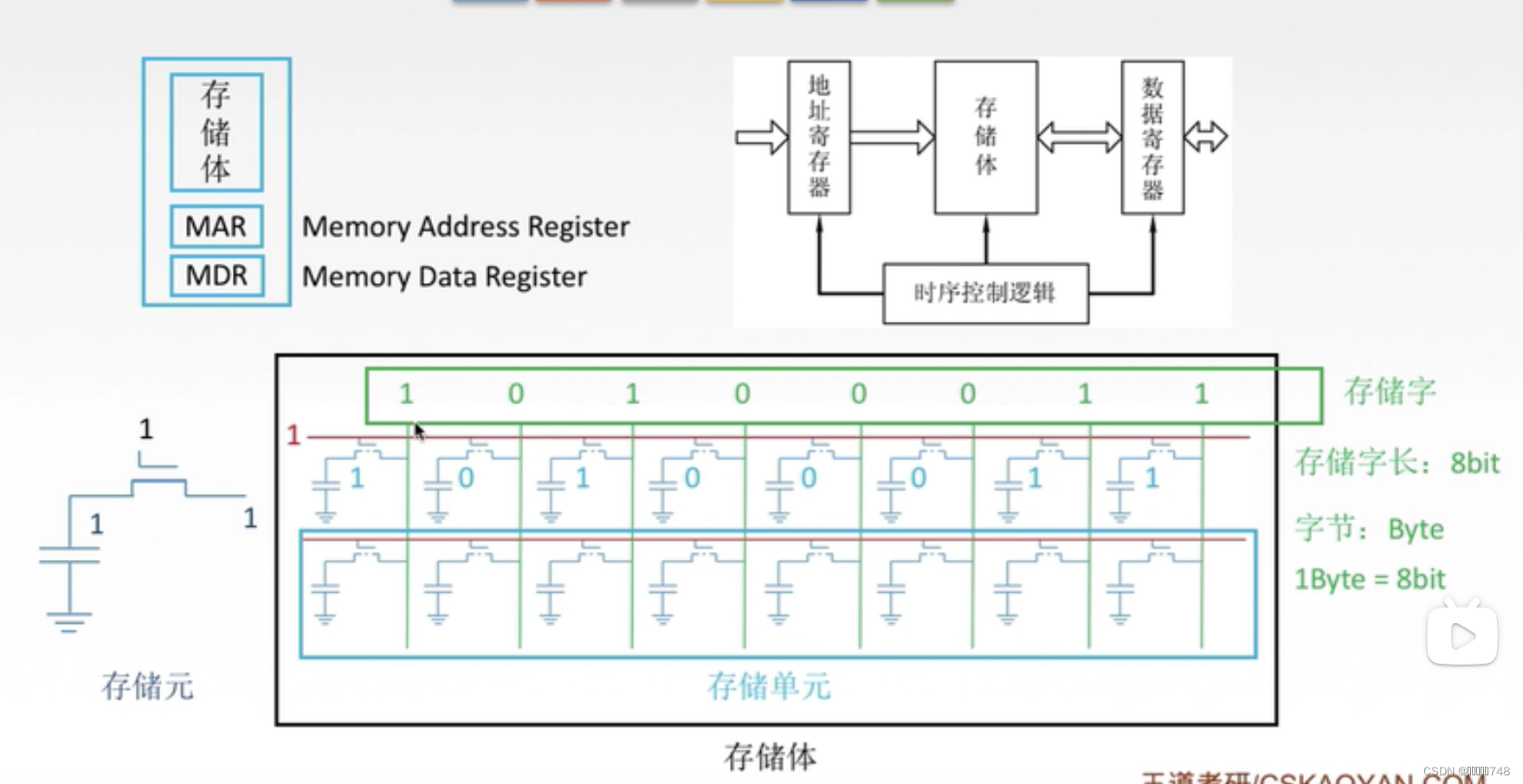

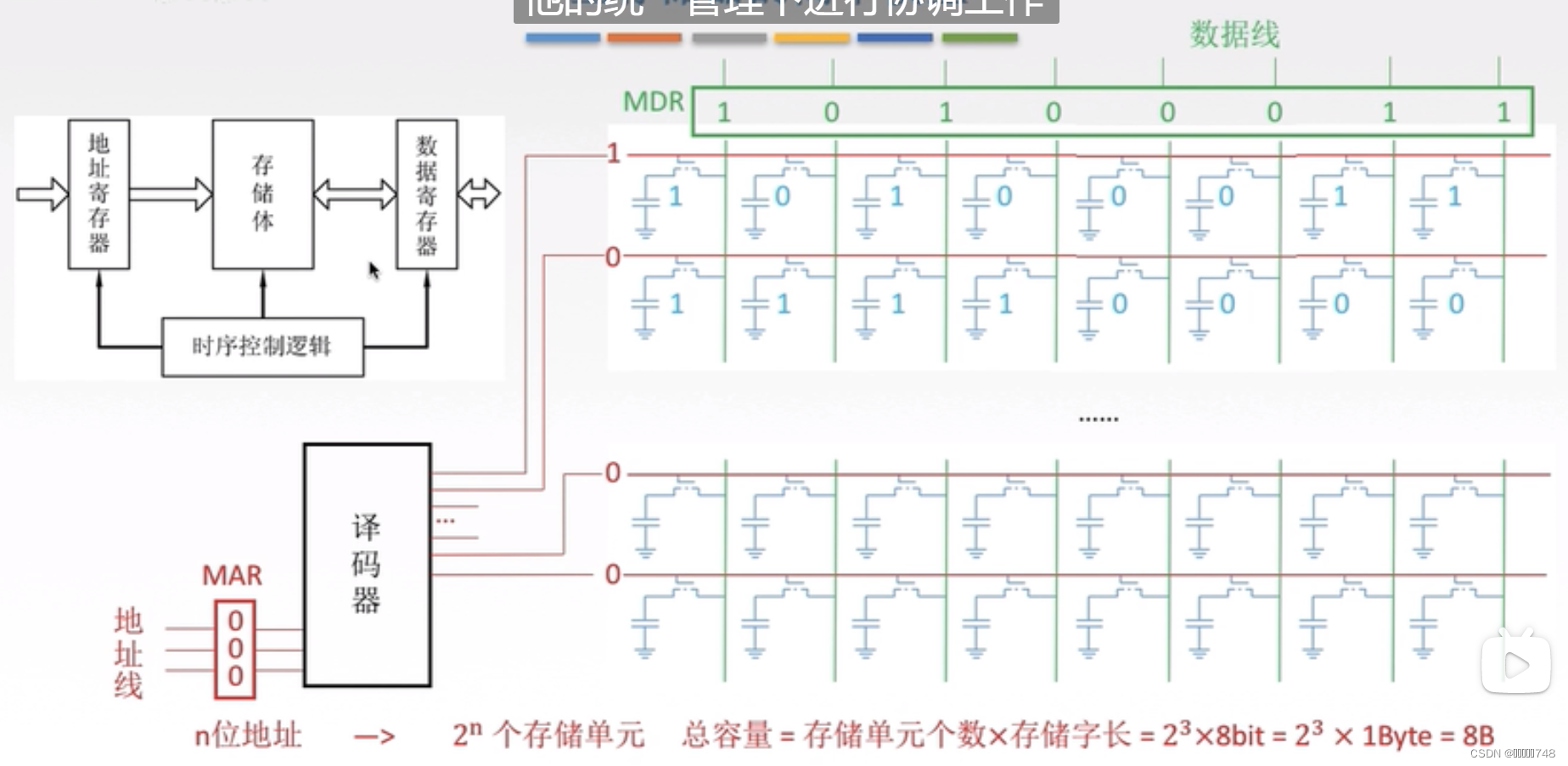

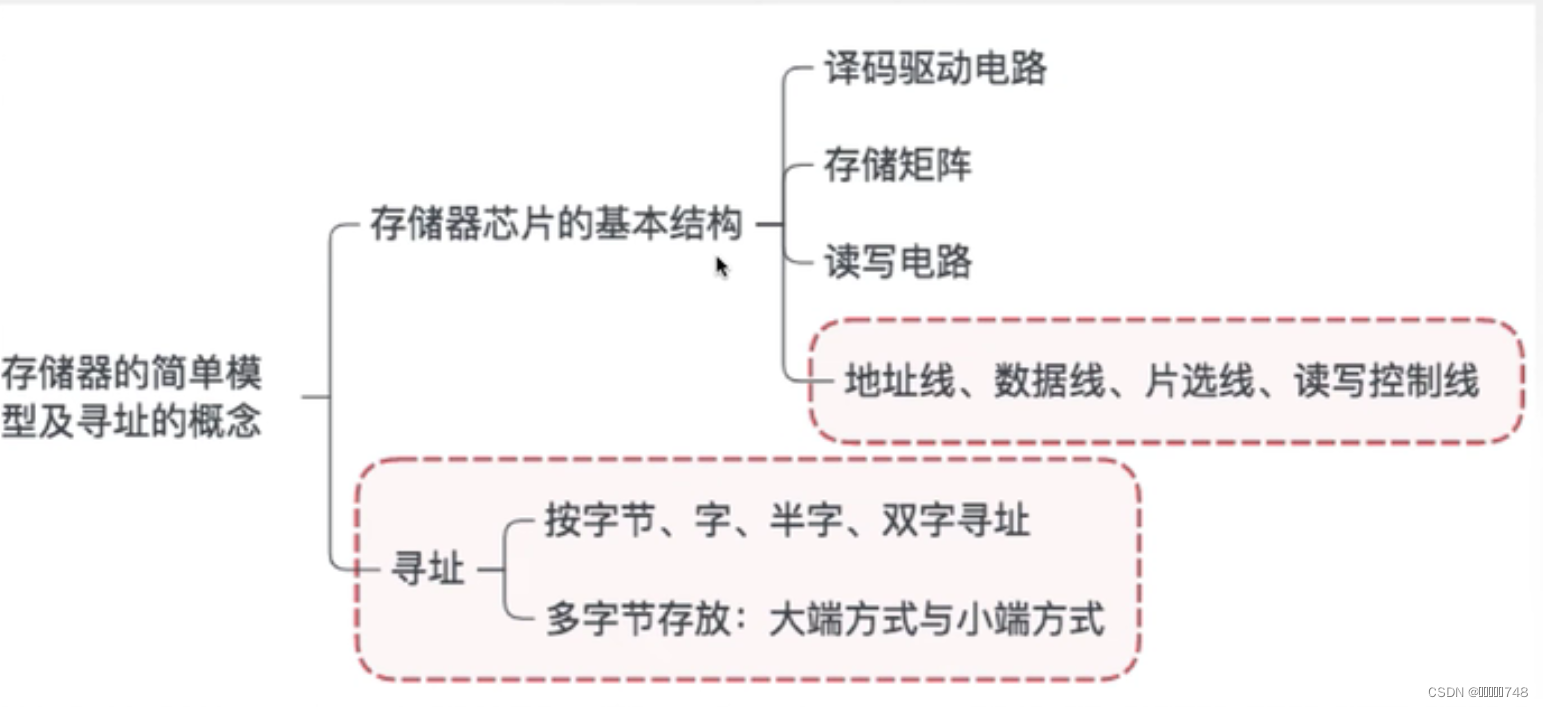

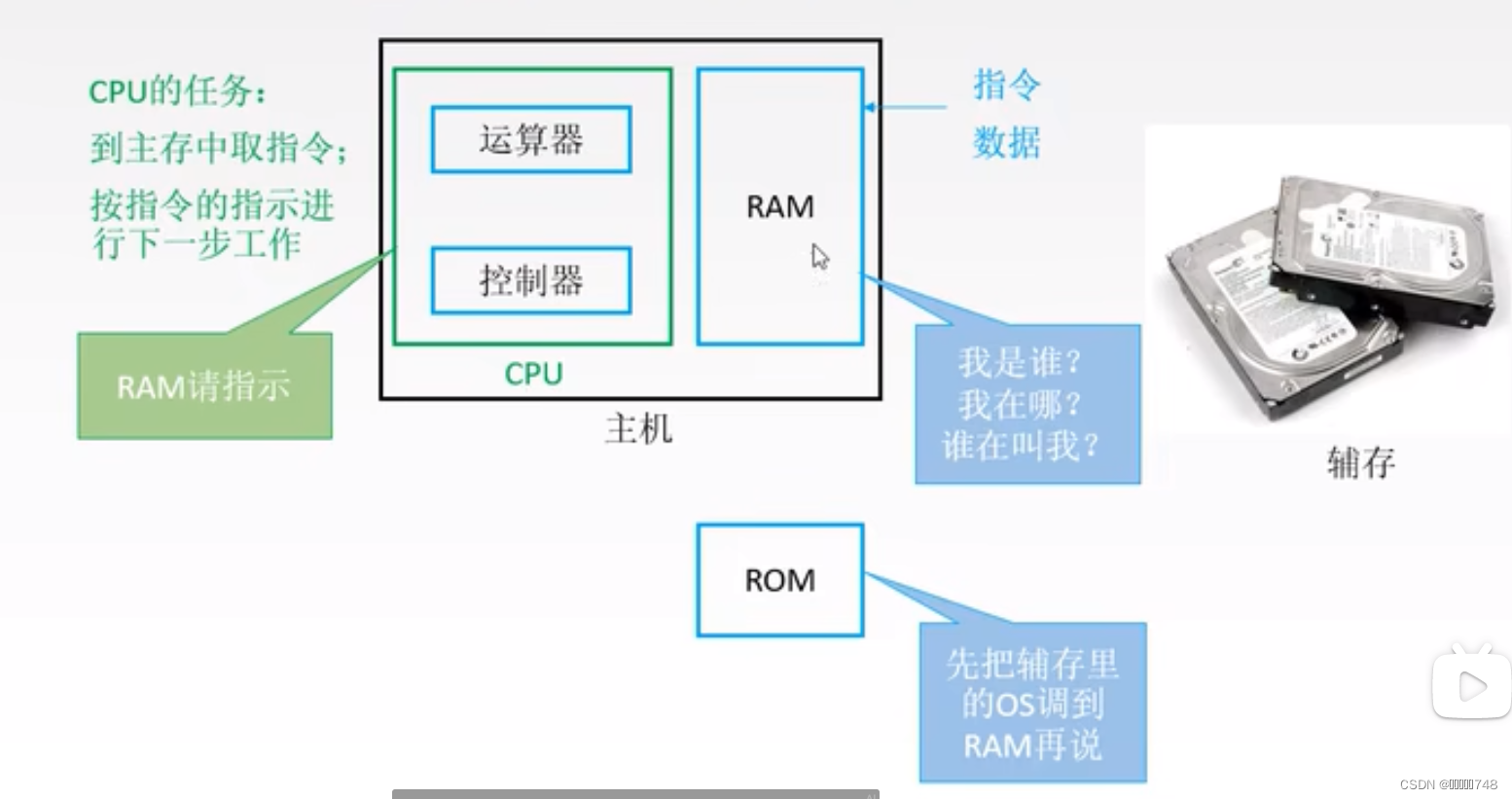

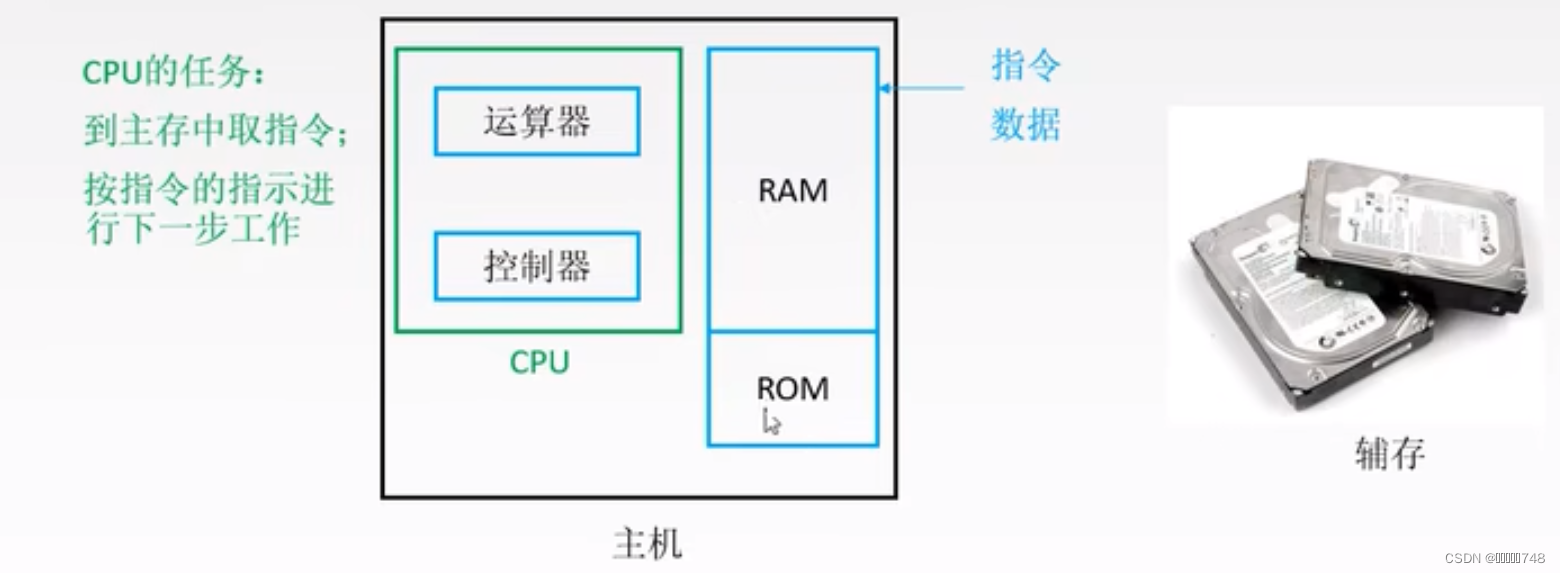

主存的简单模型

基本结构

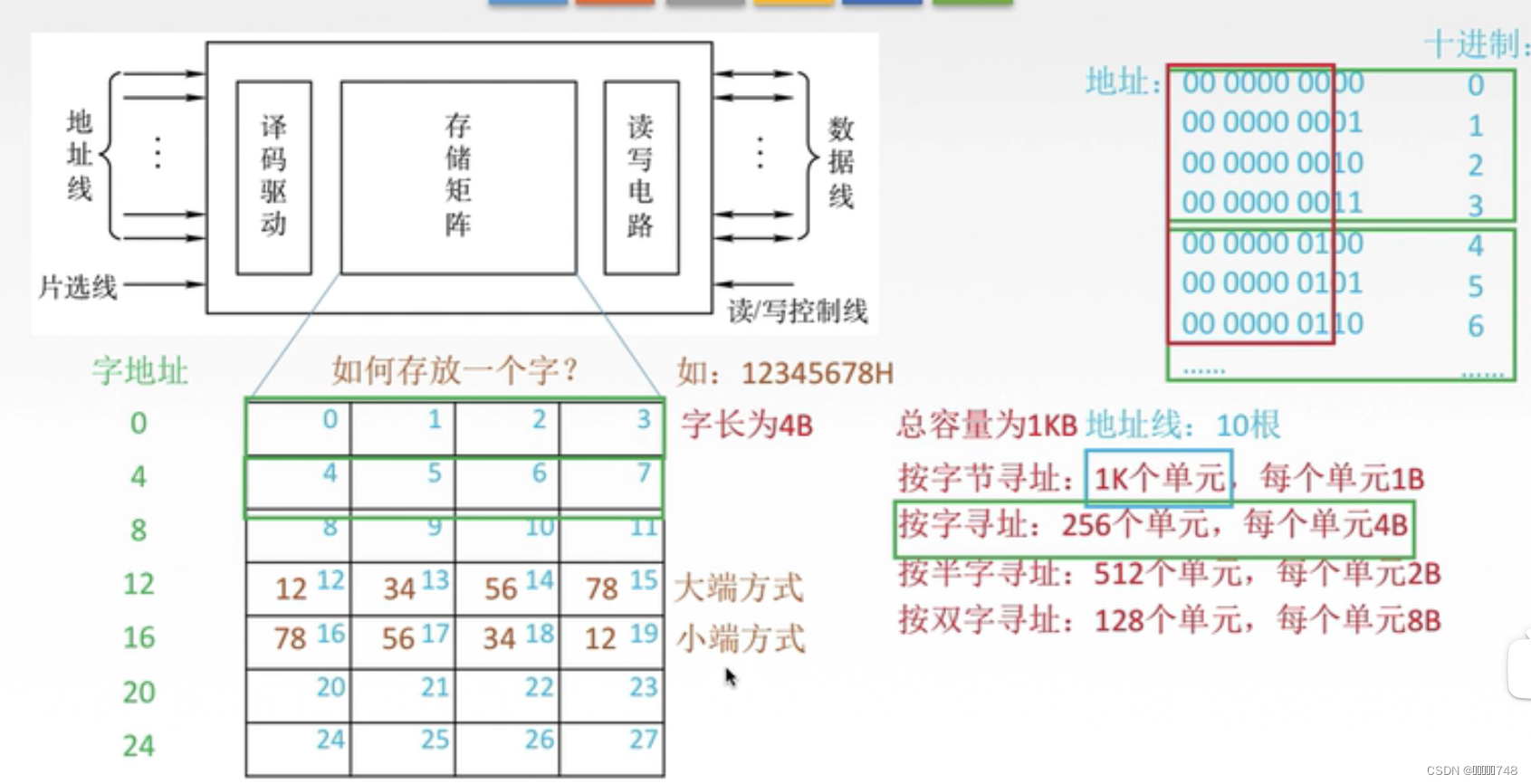

寻址

总结

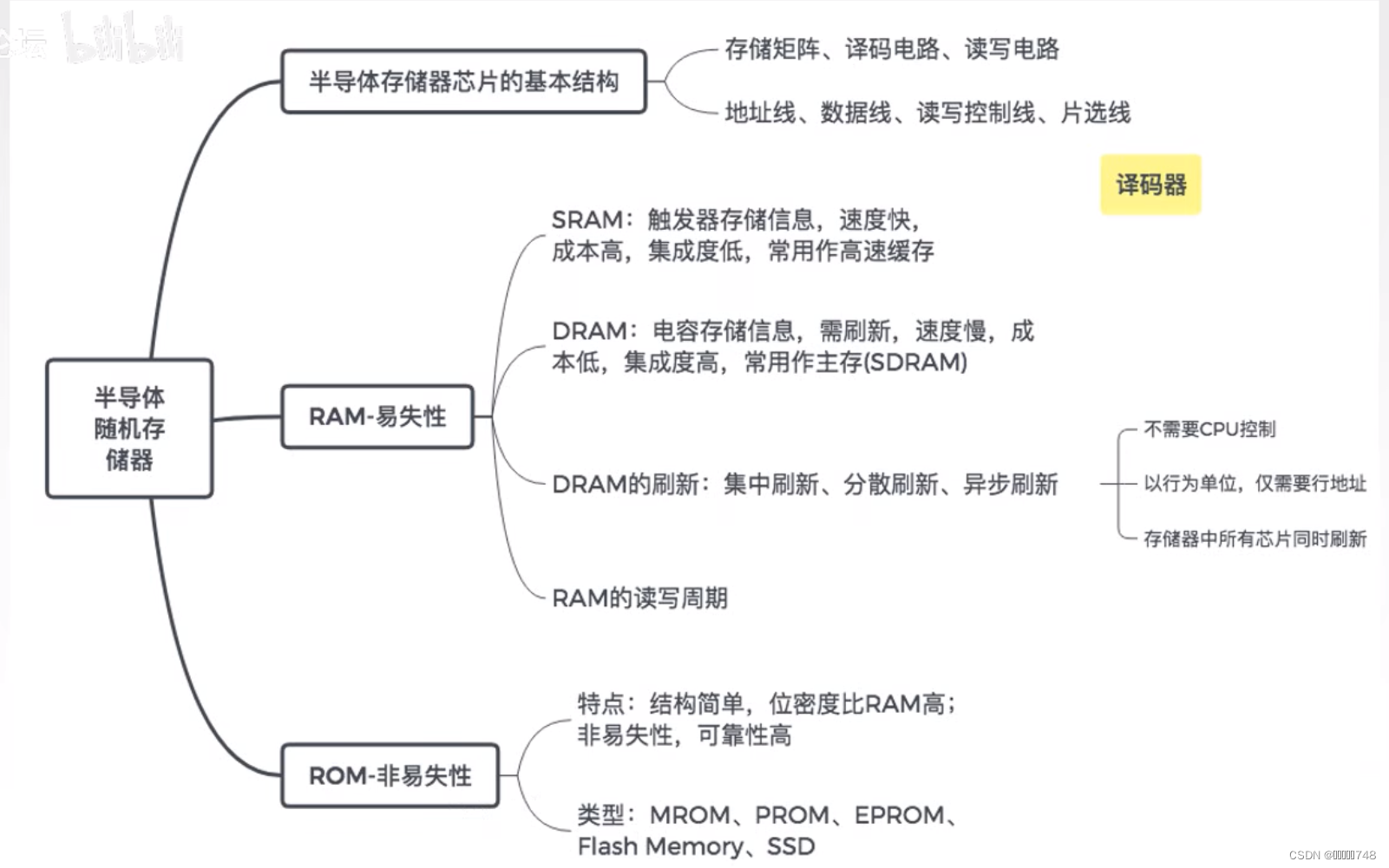

半导体存储器

基本结构

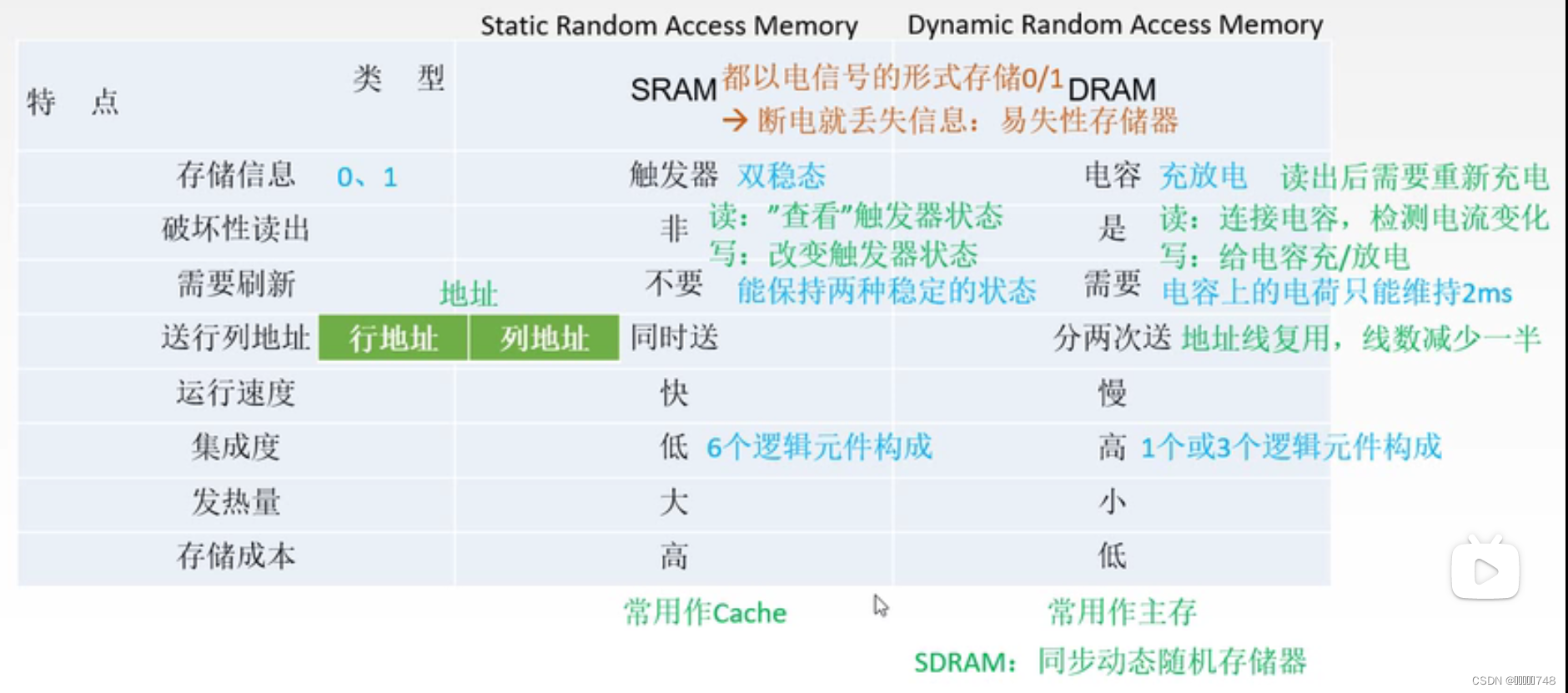

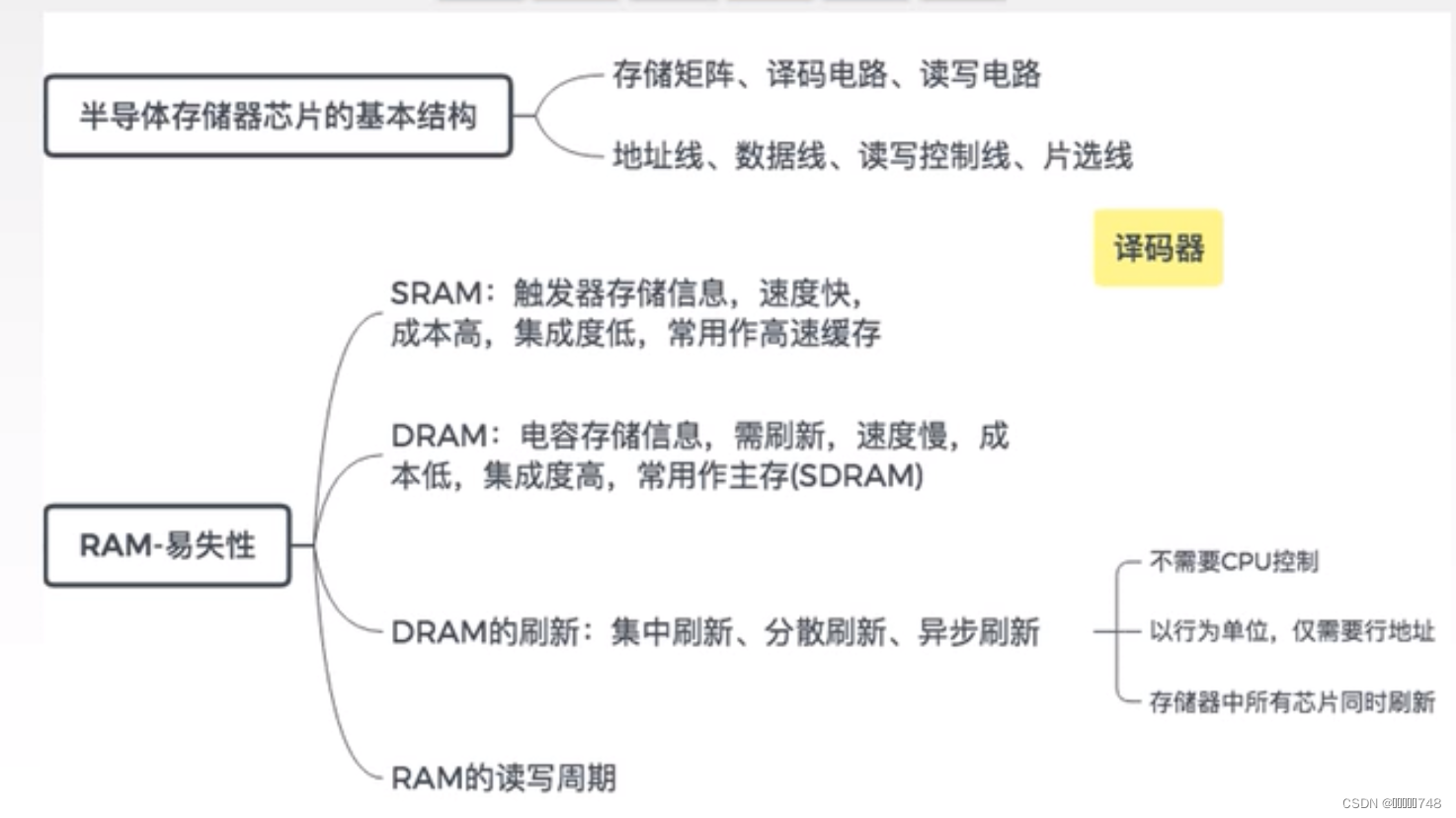

半导体存储器RAM

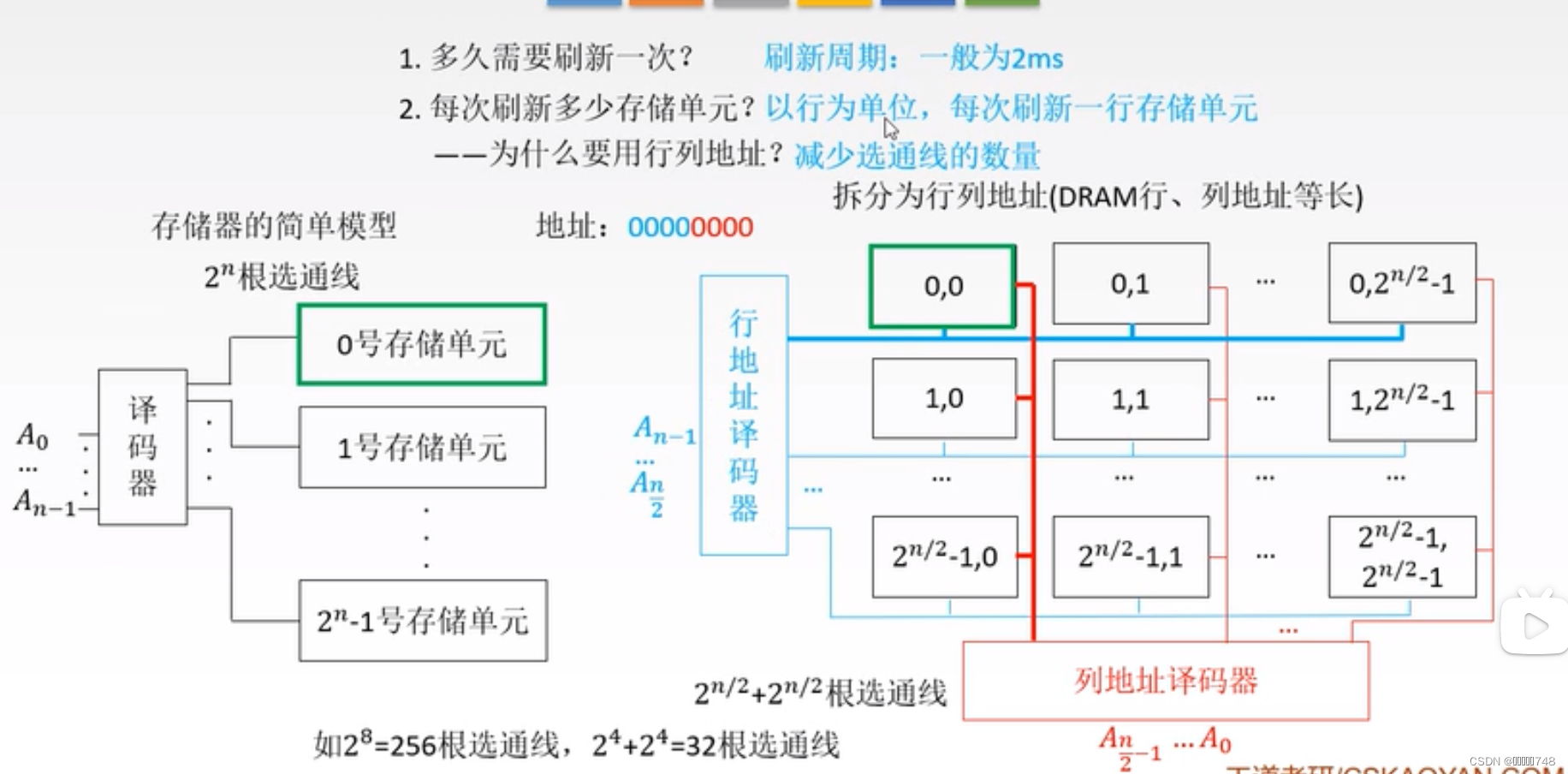

DRAM的刷新

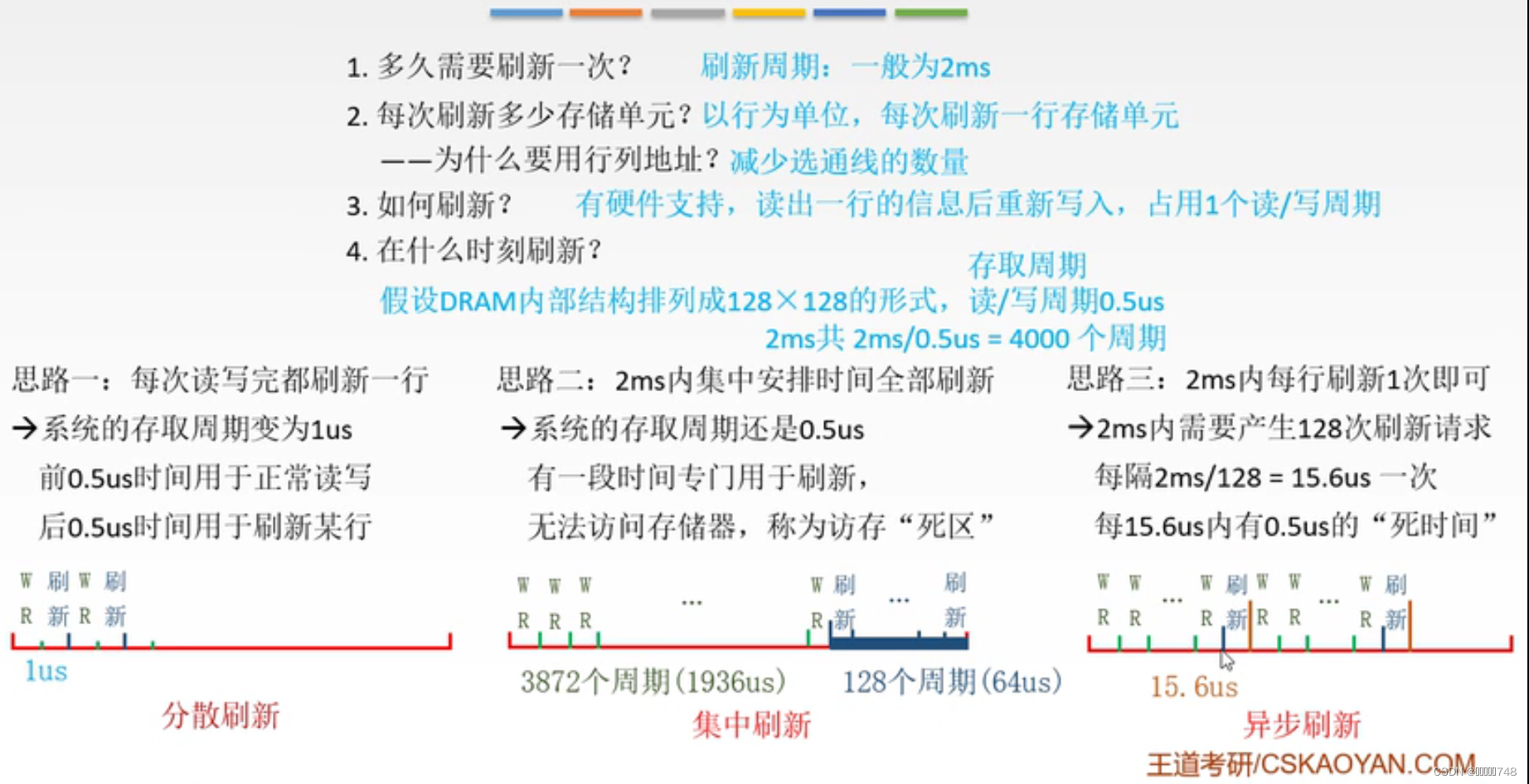

SRAM的读周期

SRAM的写周期

总结

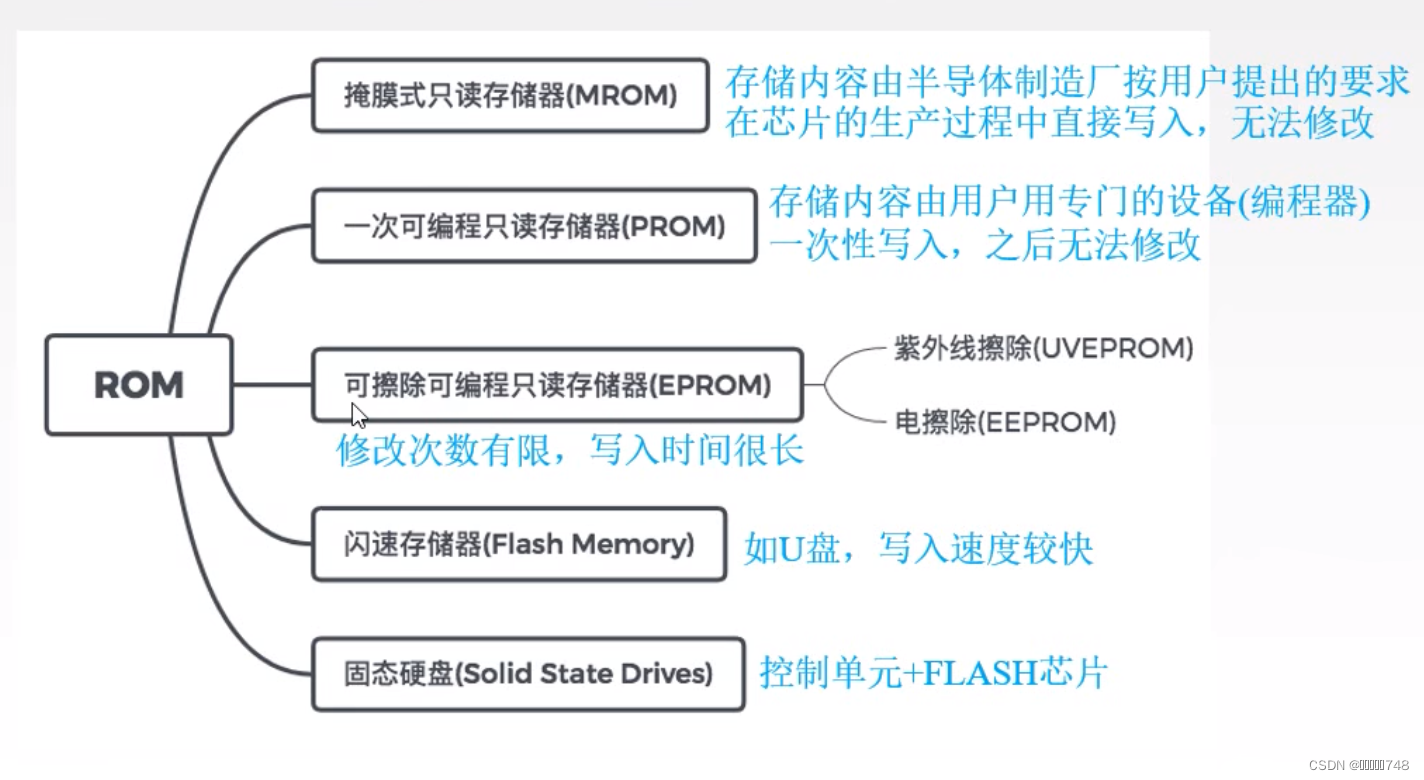

半导体存储器ROM

RAM易失性存储性

只读存储器

总结

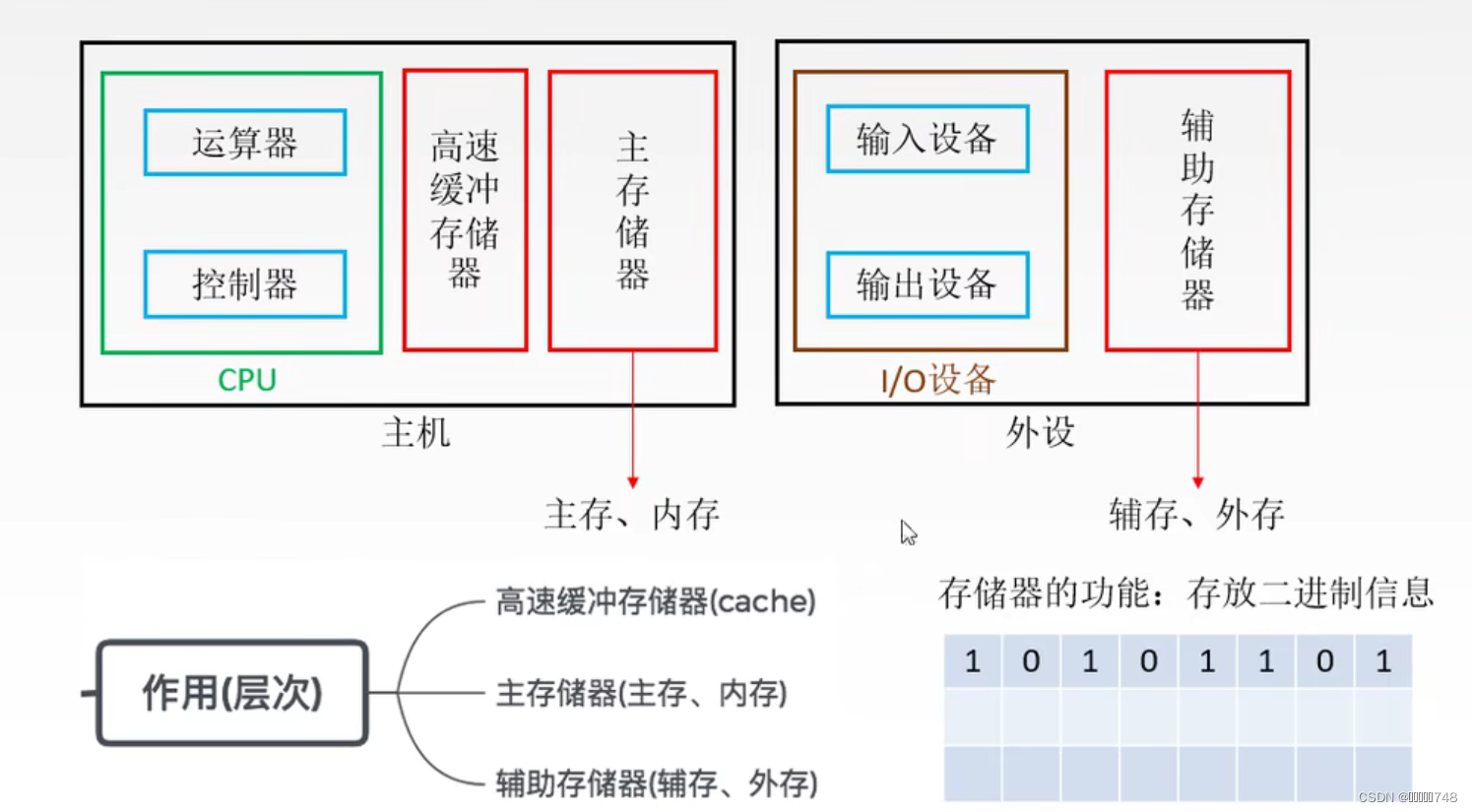

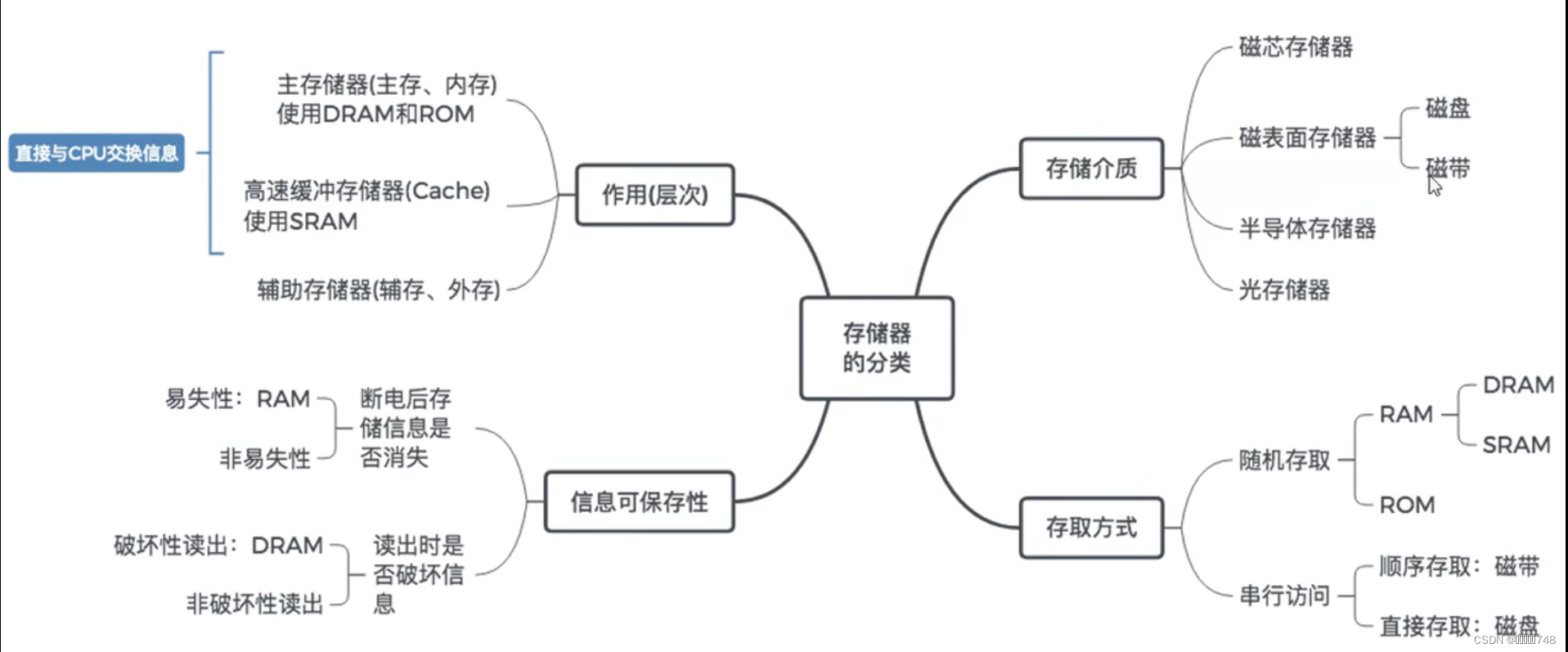

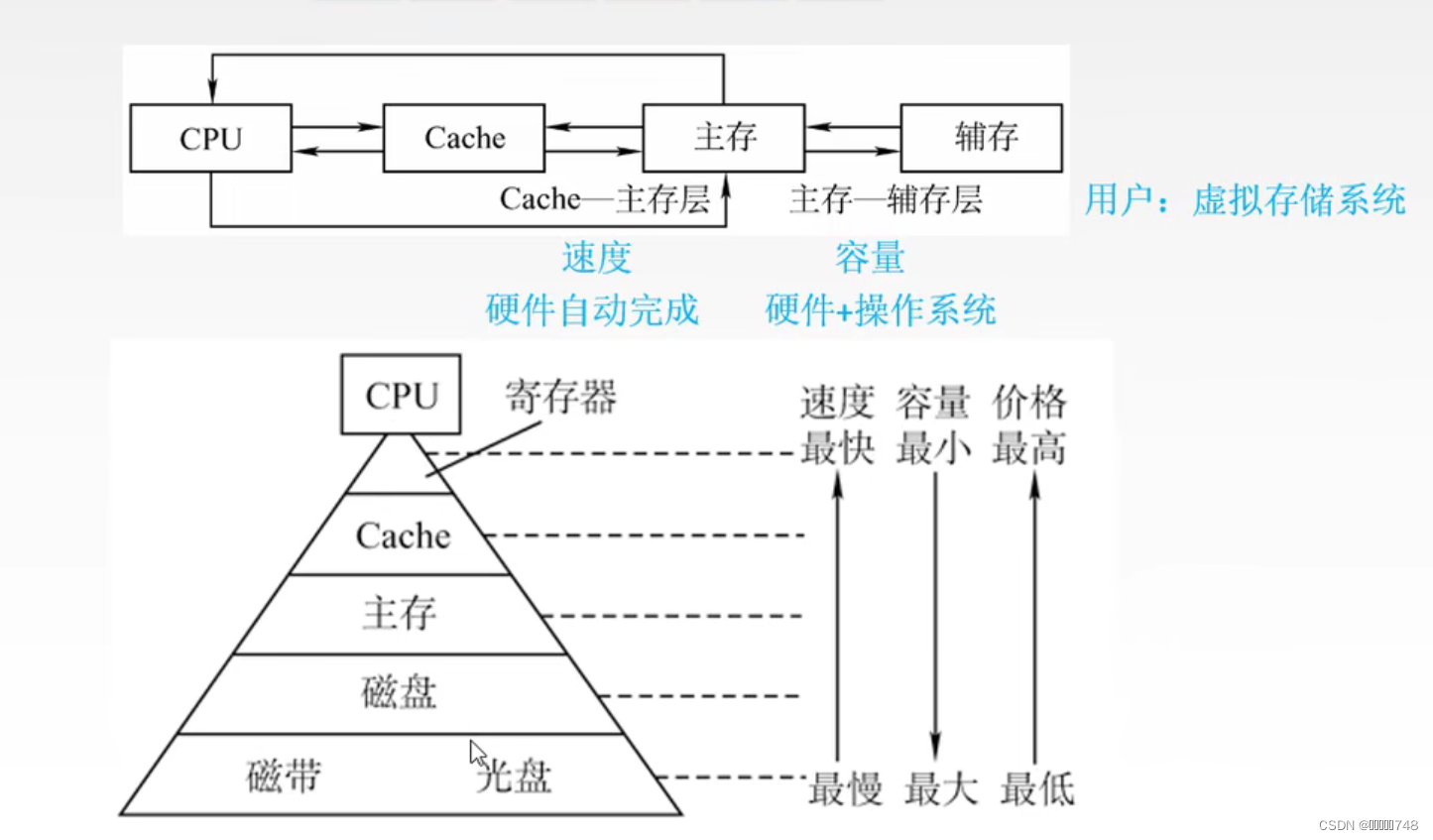

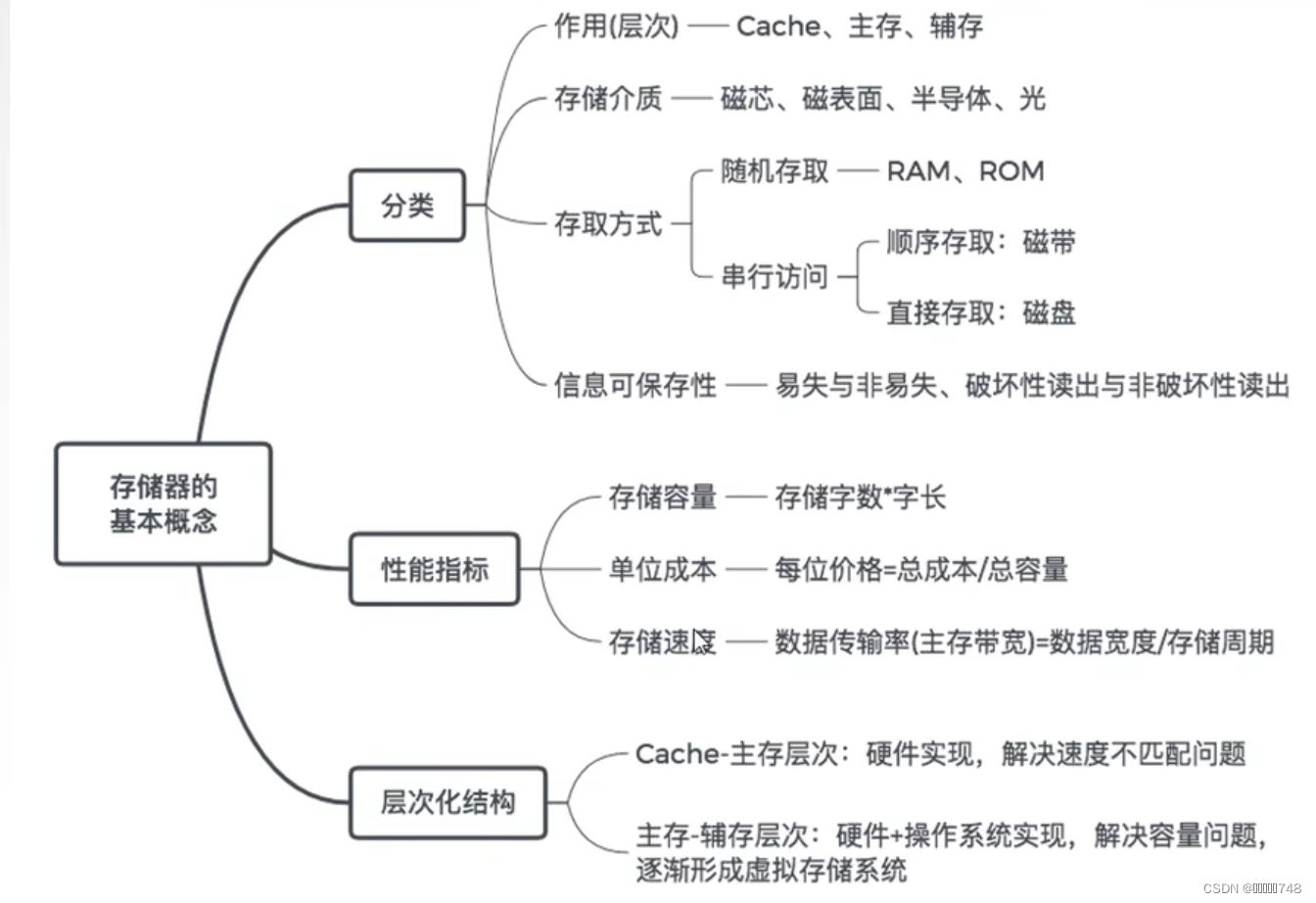

存储器的基本概念

存储器的分类

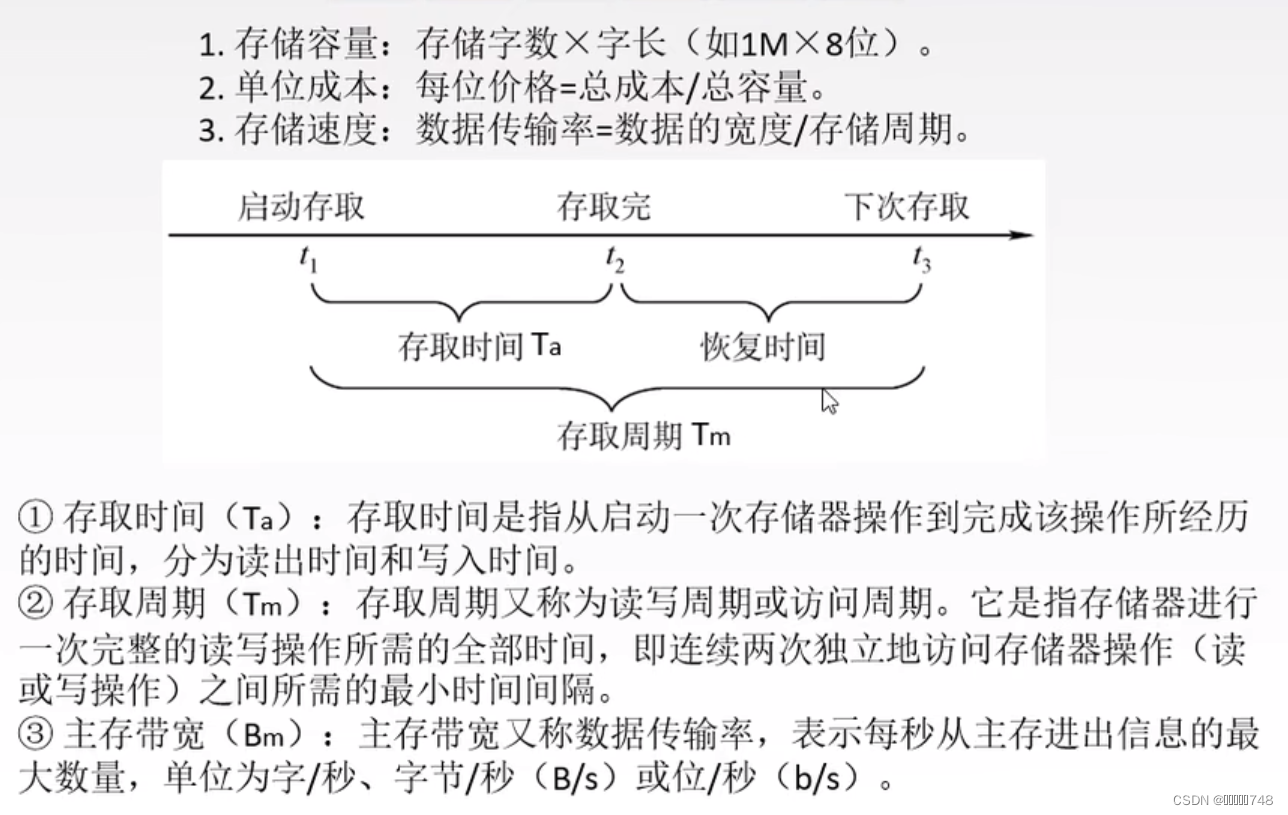

存储器的性能指标

存储器层次化结构

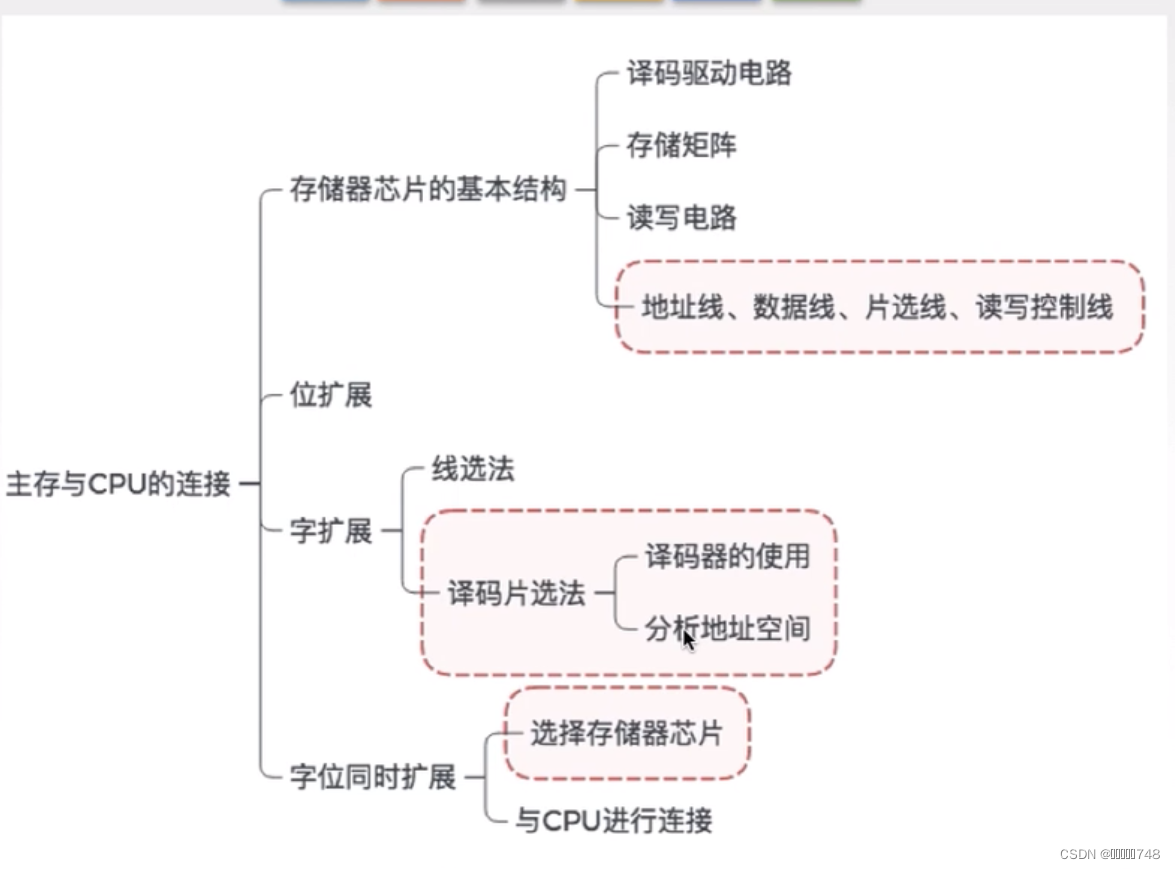

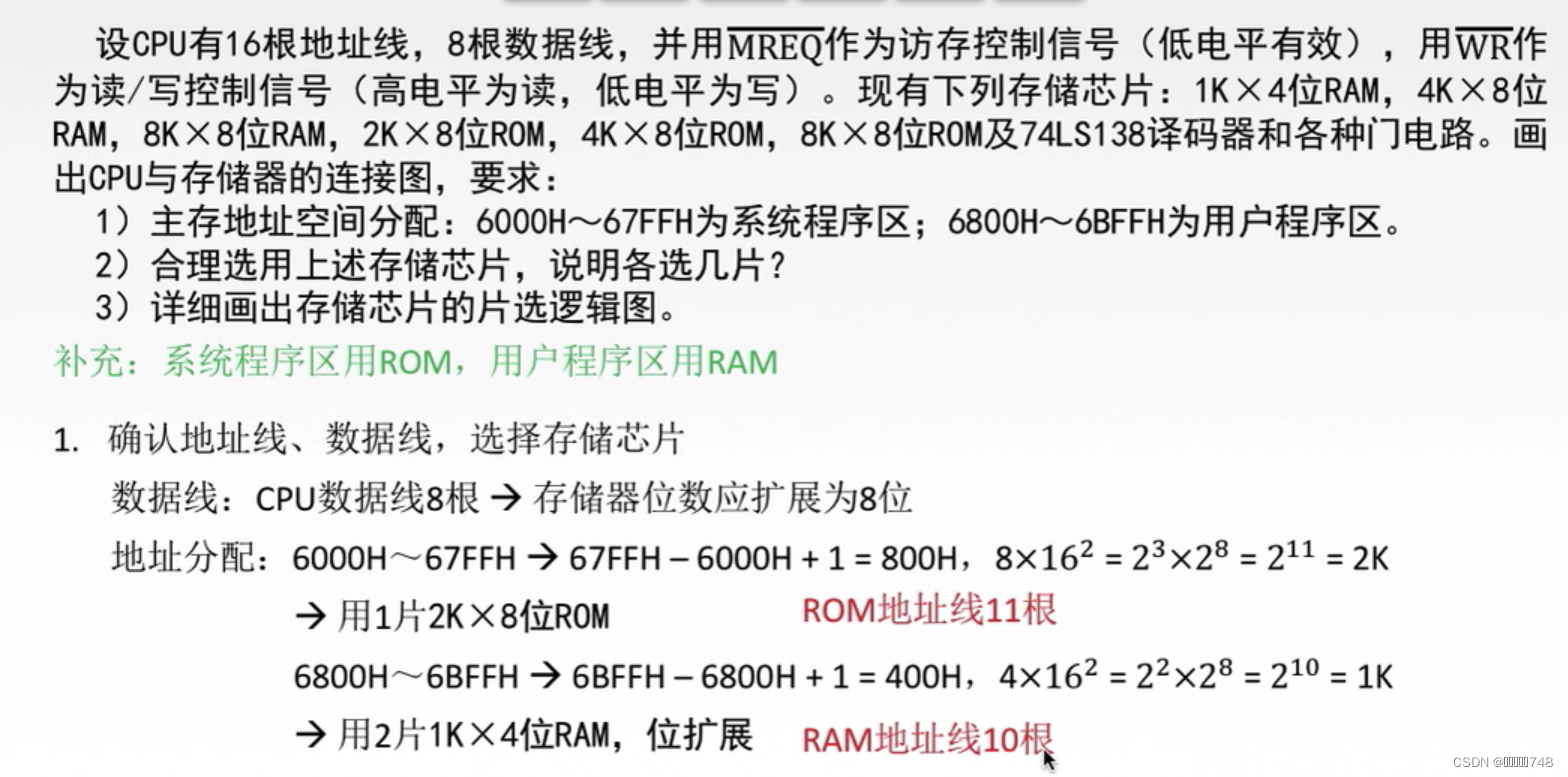

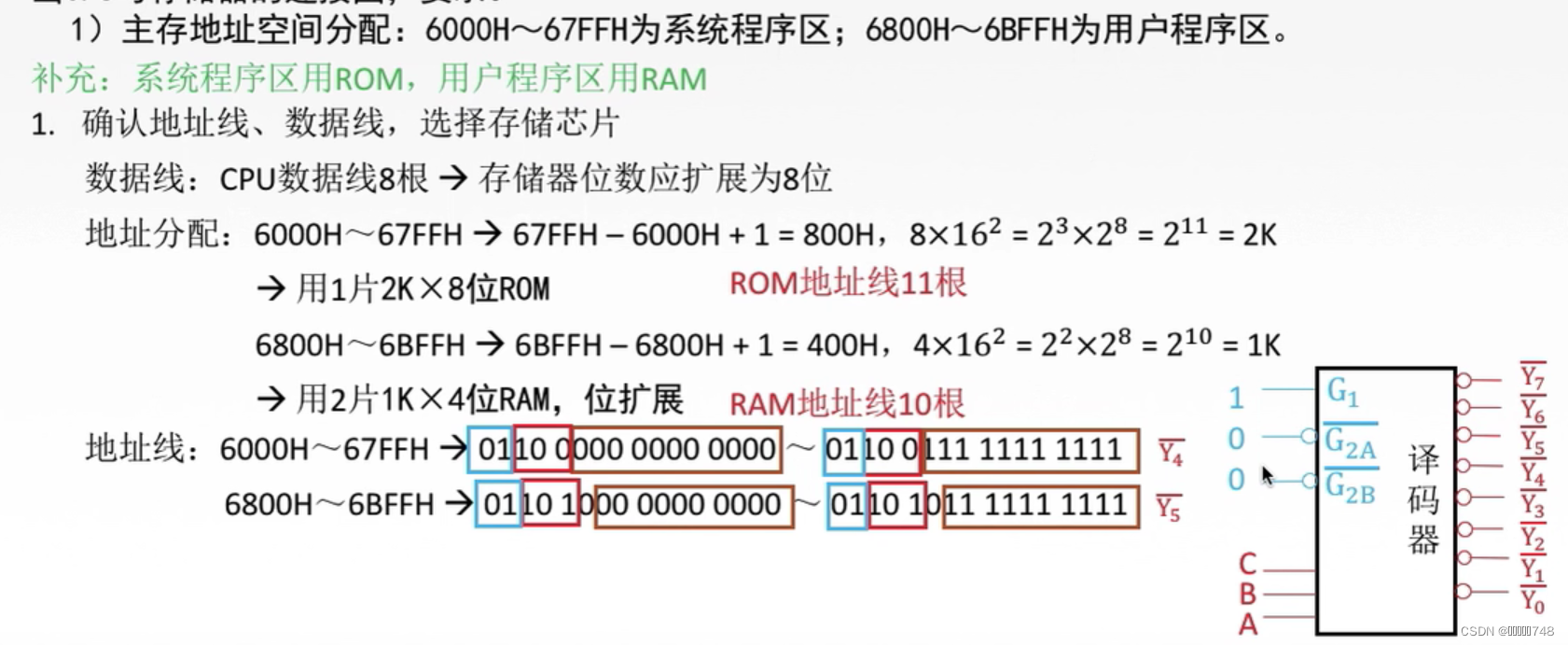

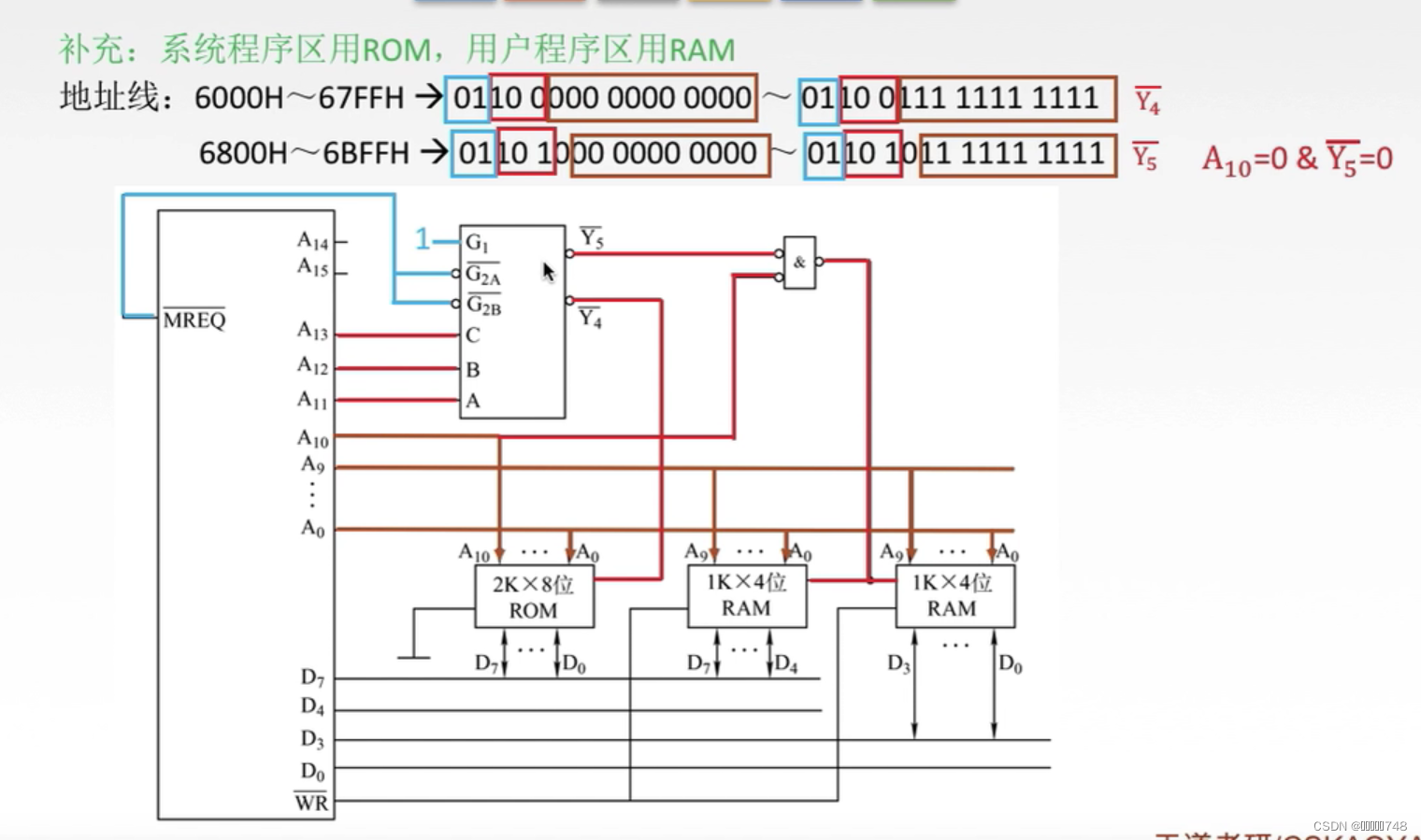

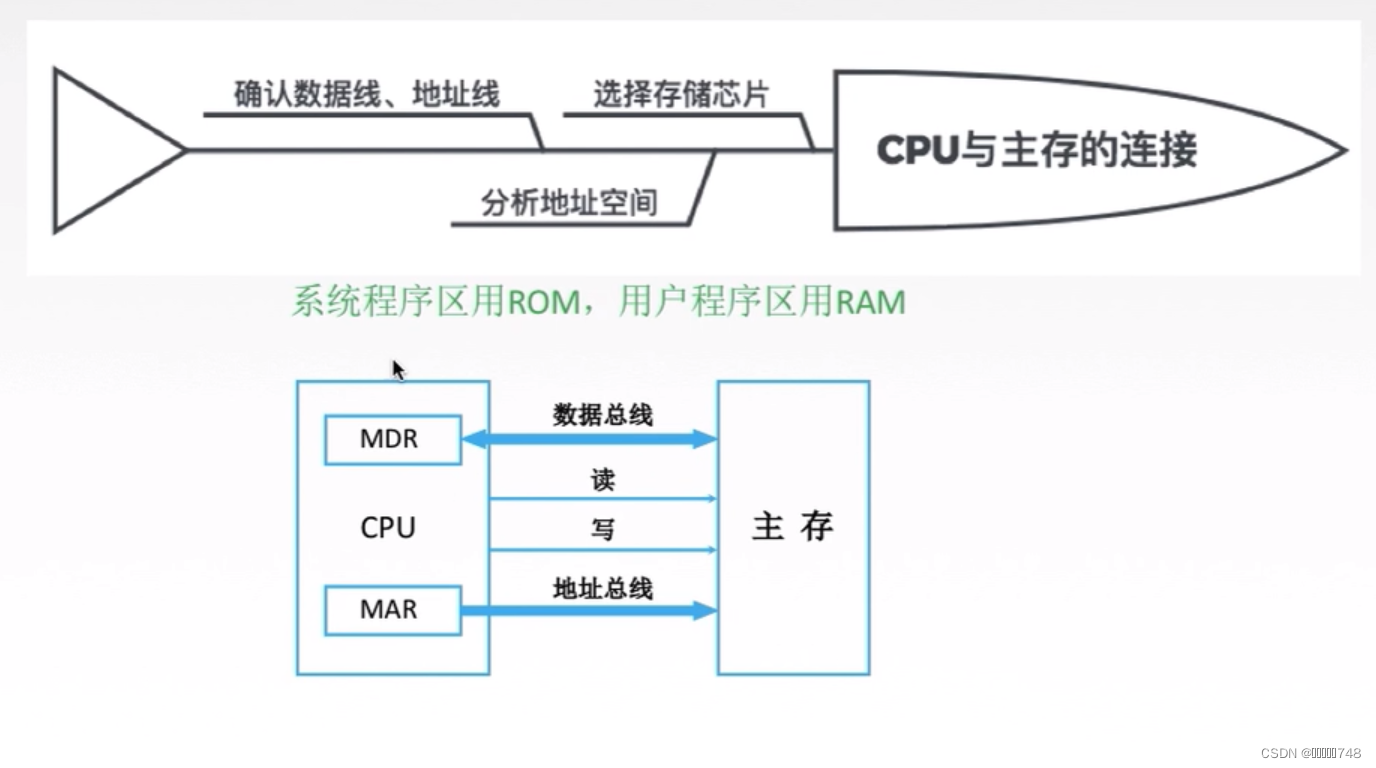

主存与CPU的连接

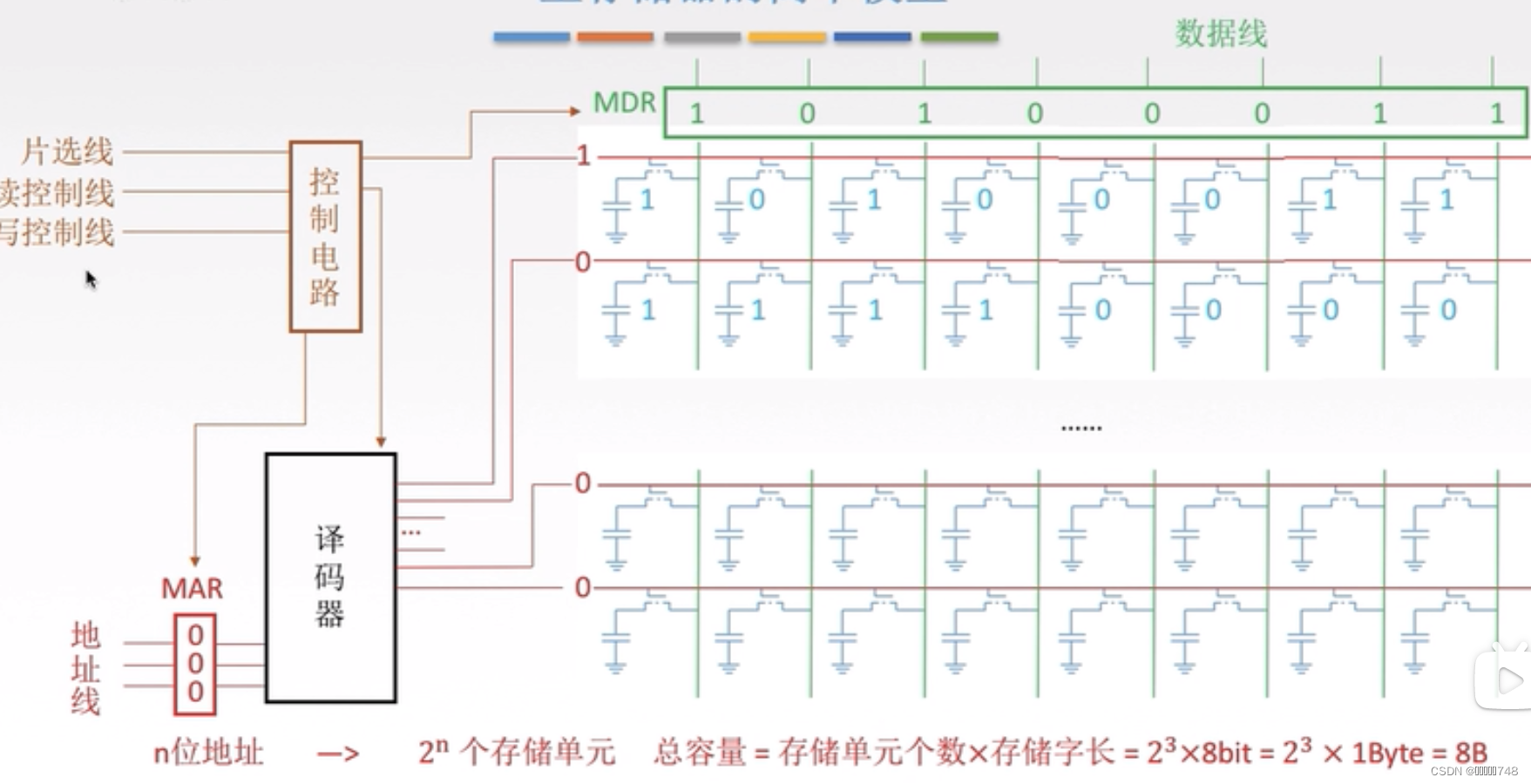

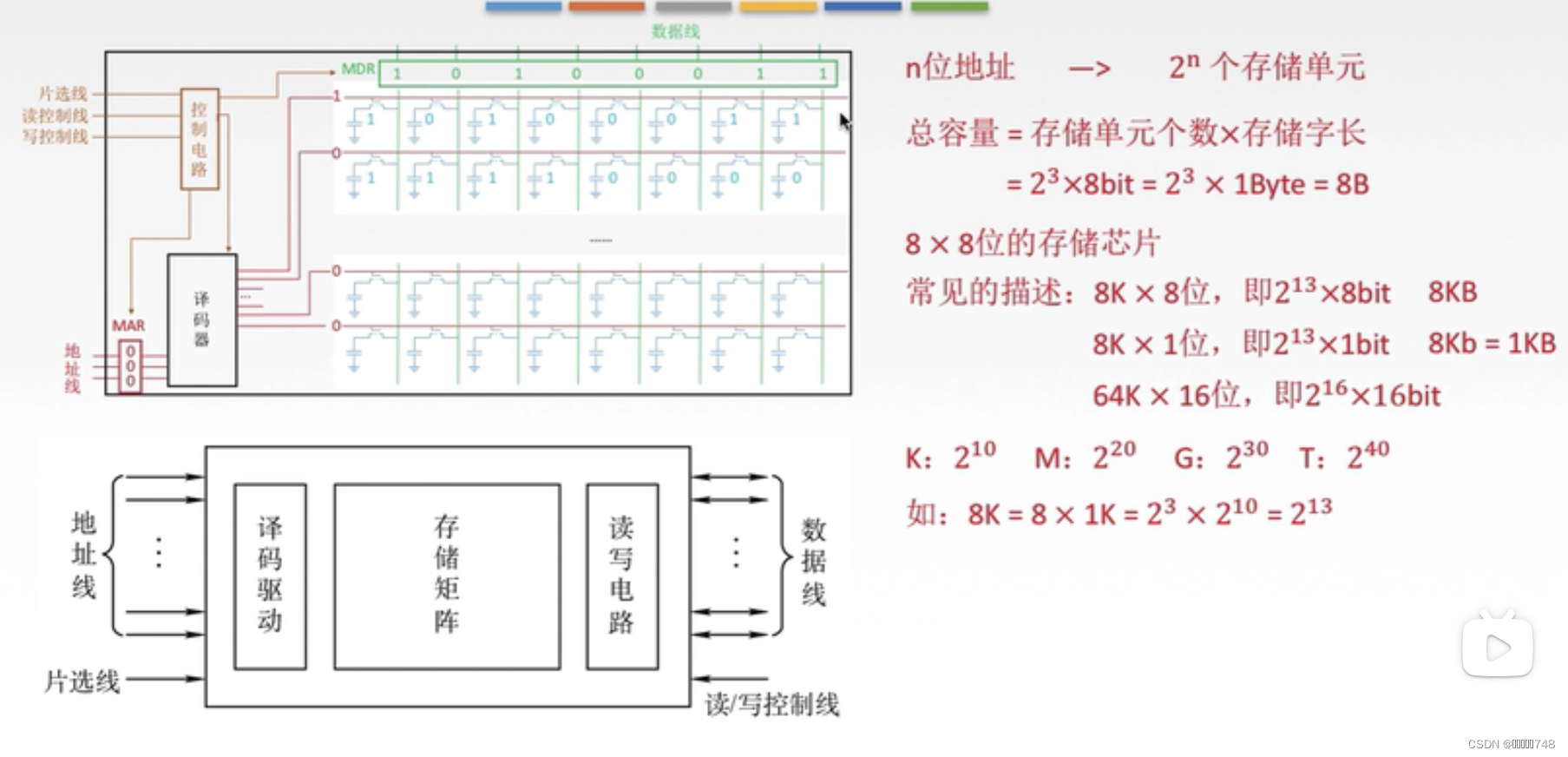

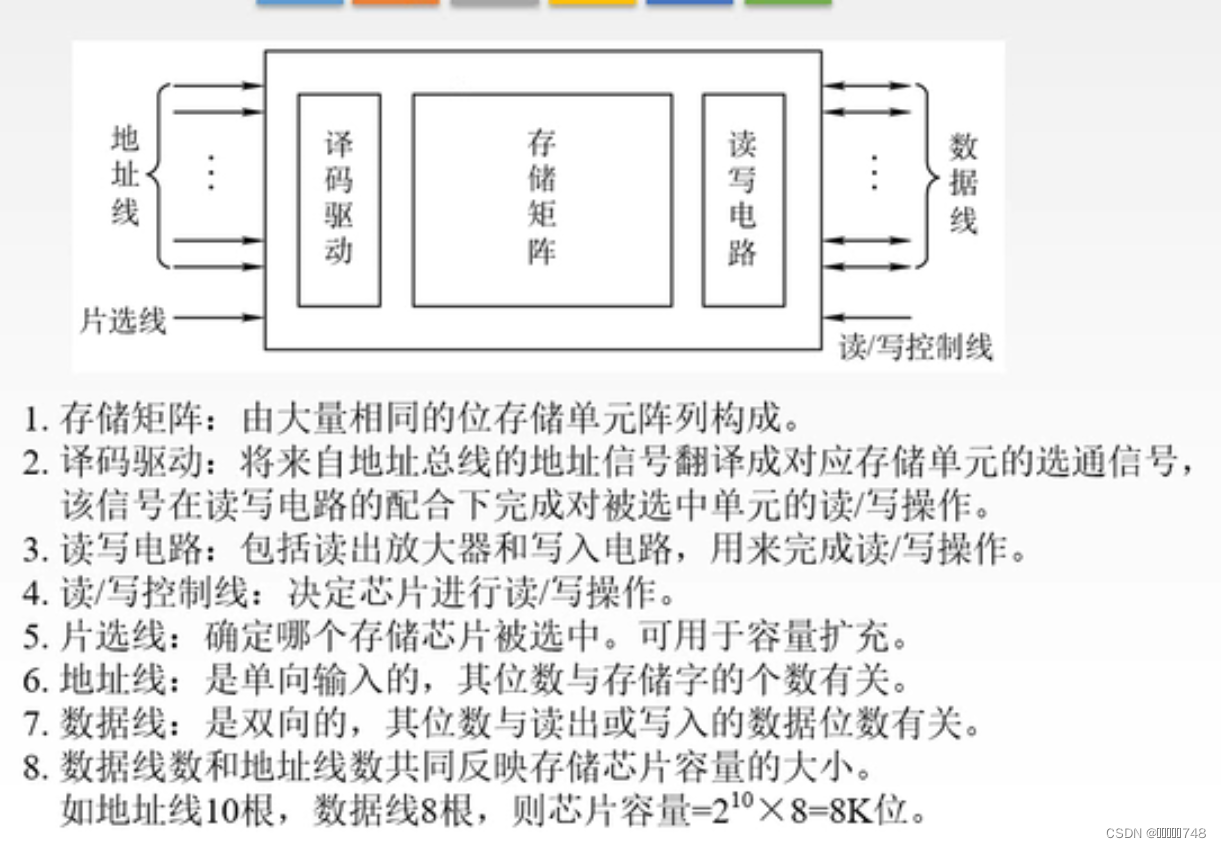

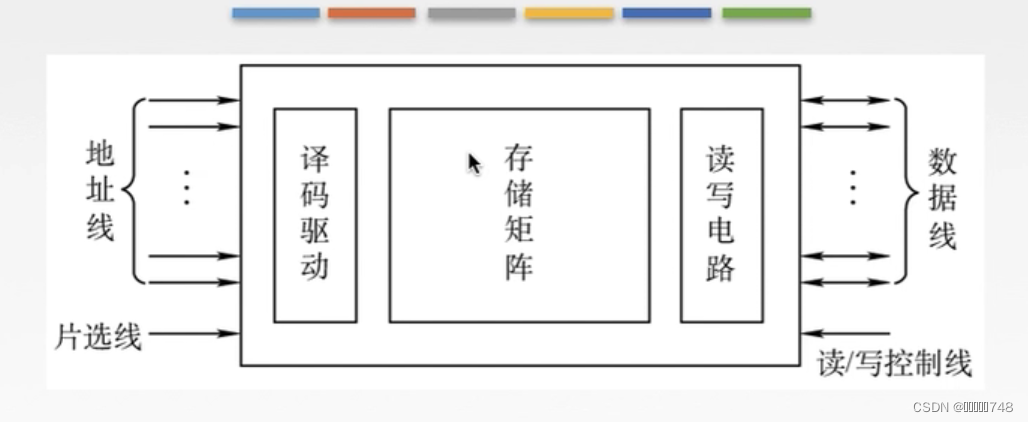

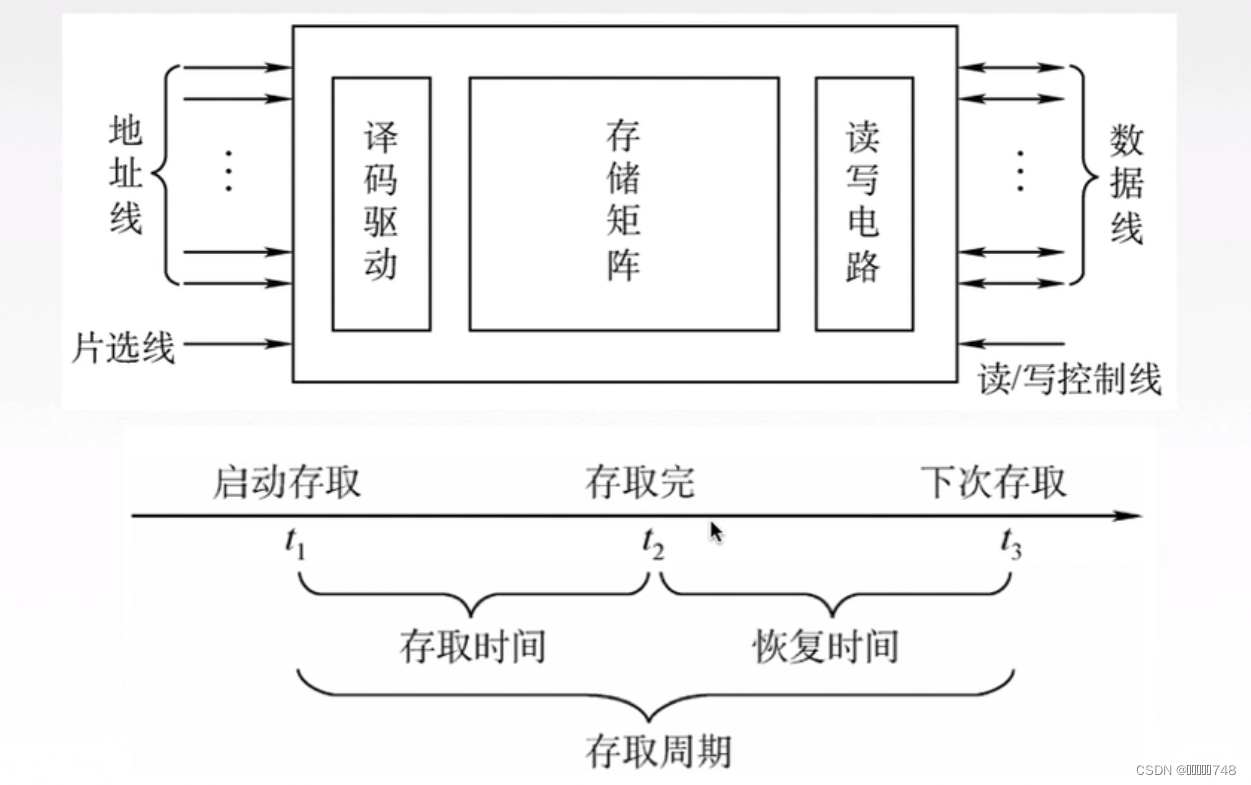

存储器芯片的基本结构

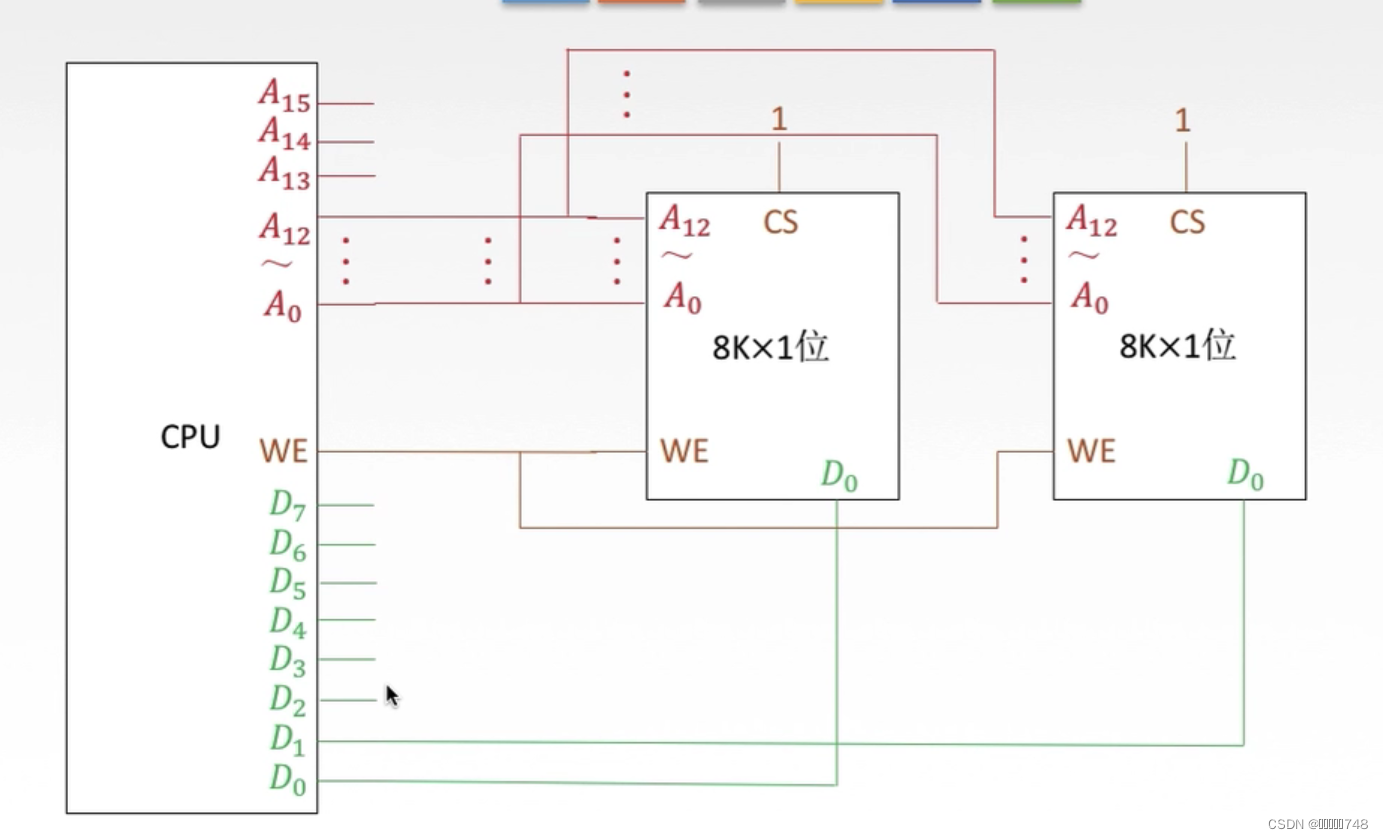

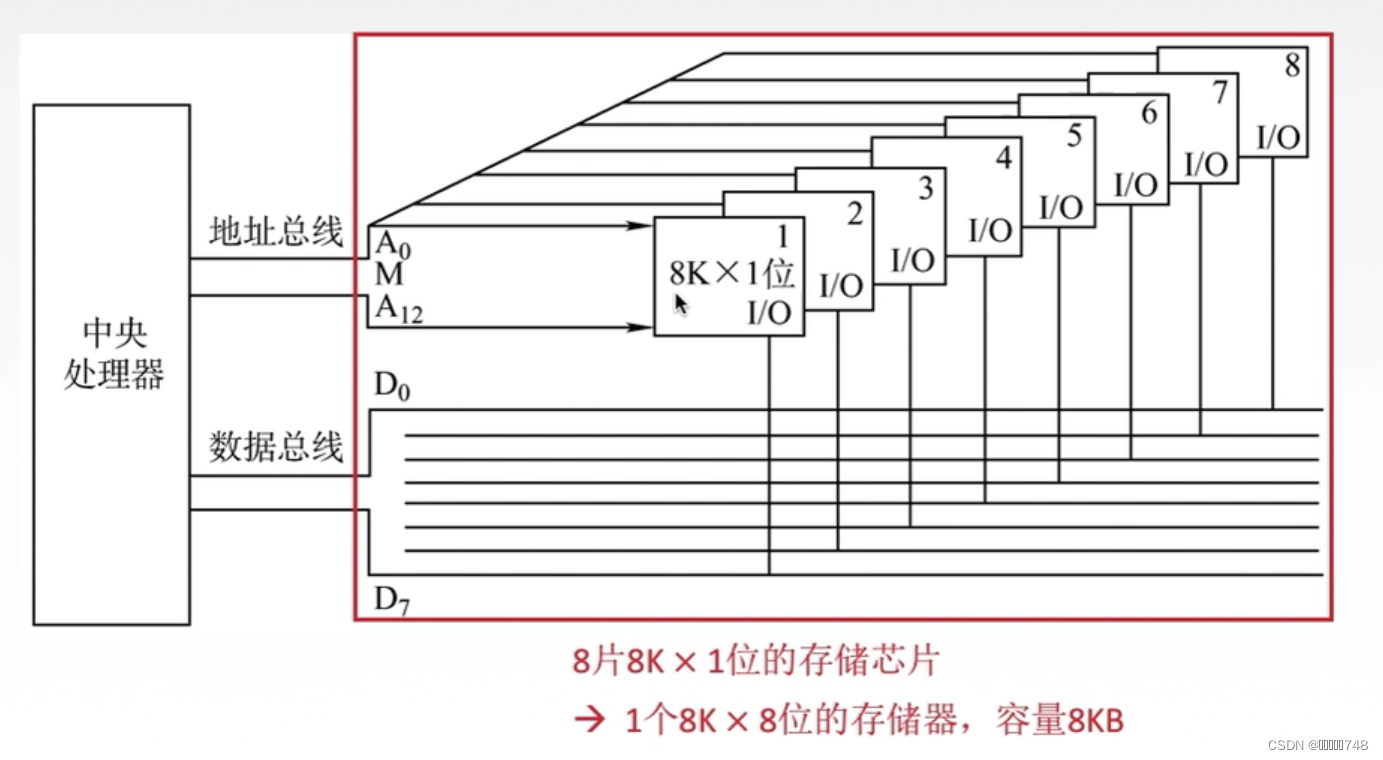

主存容量扩展-位扩展

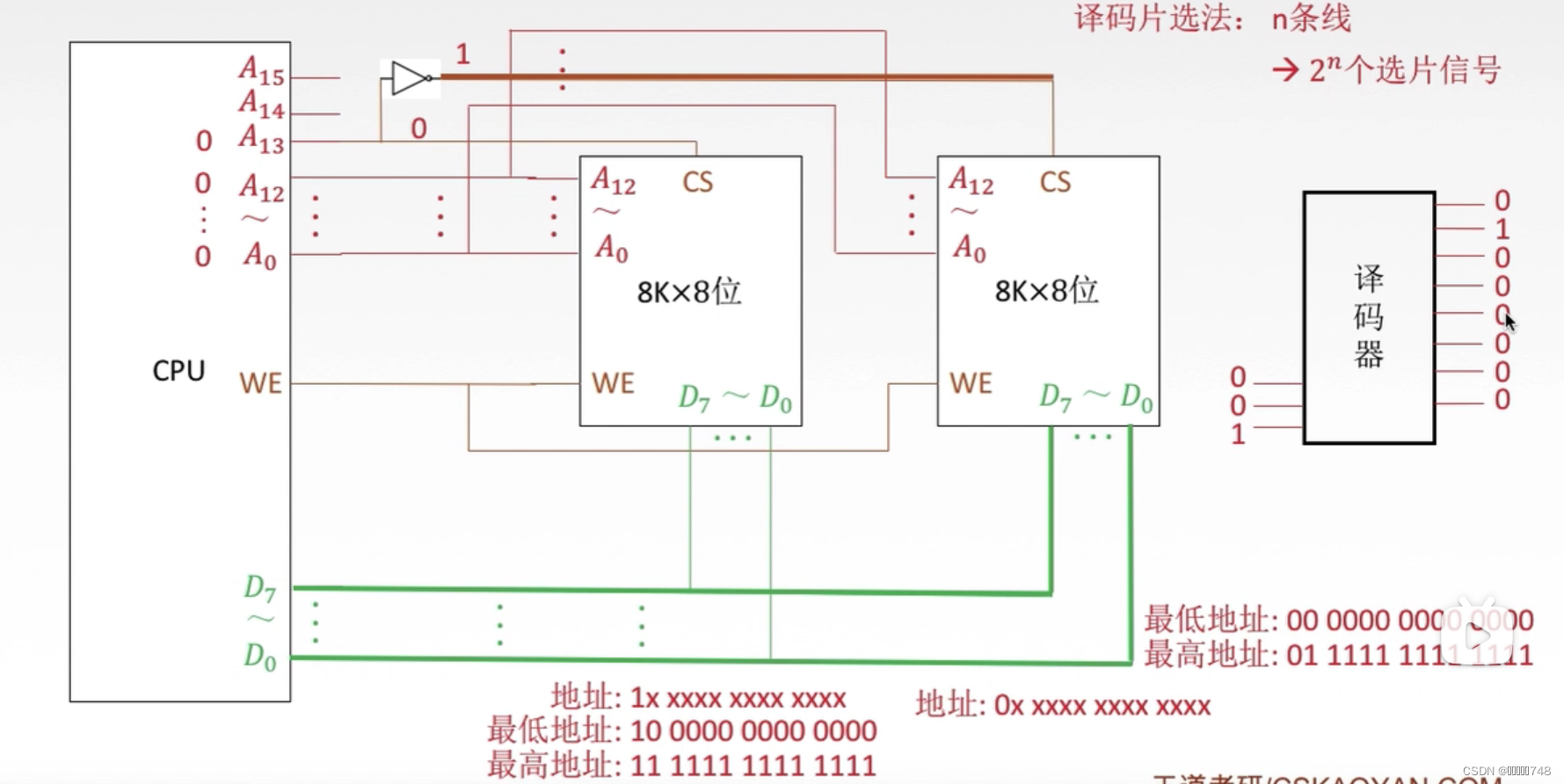

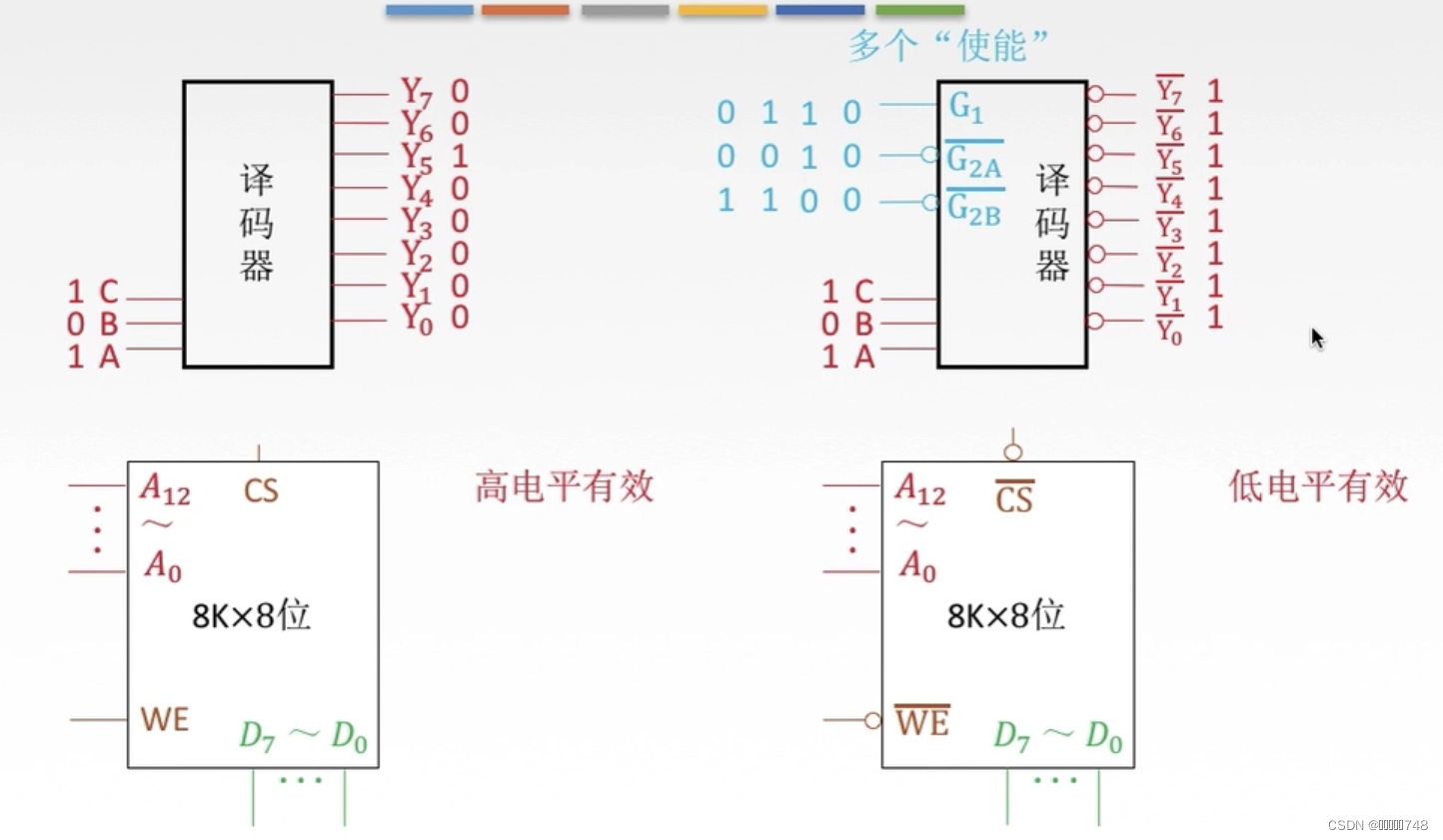

译码器

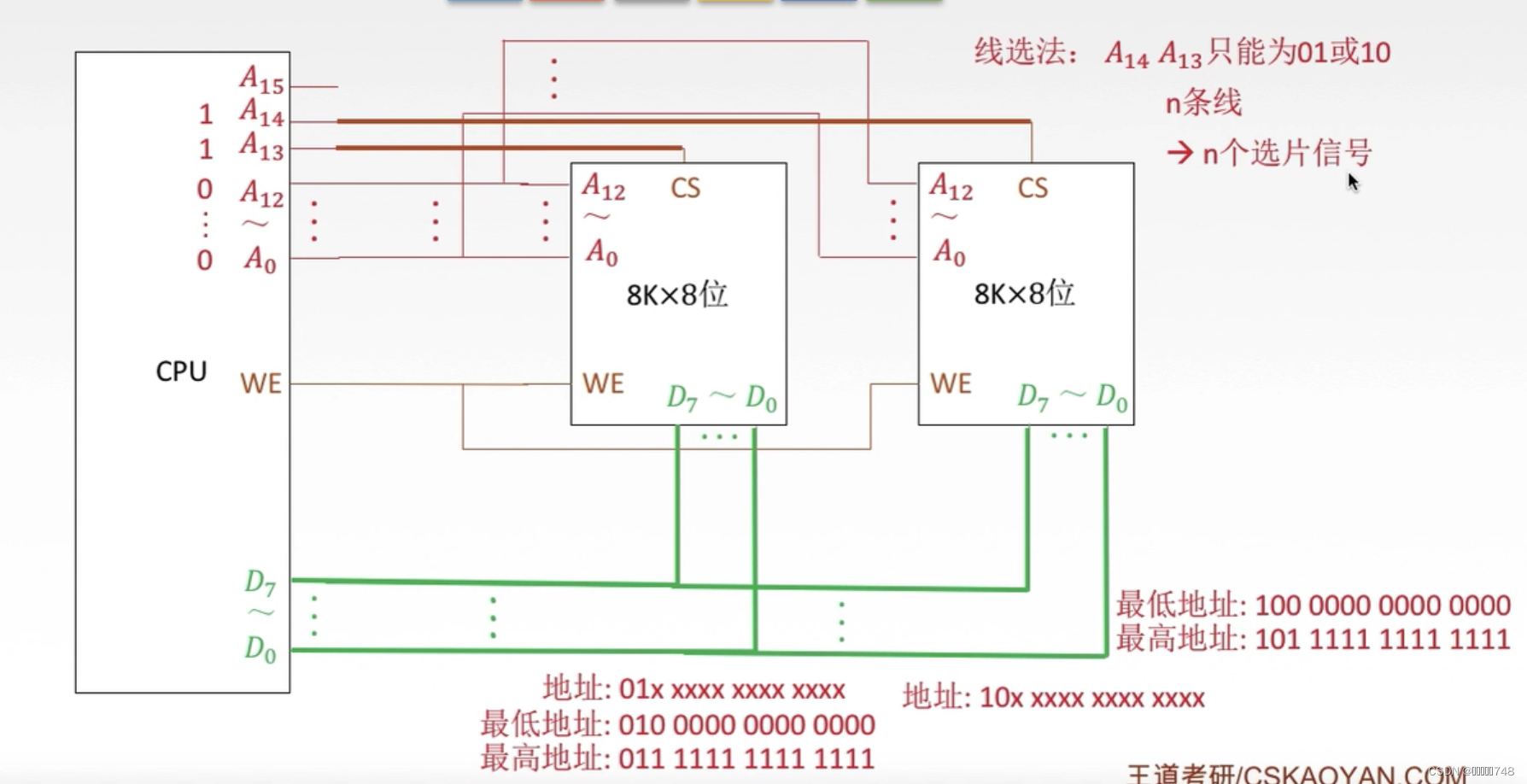

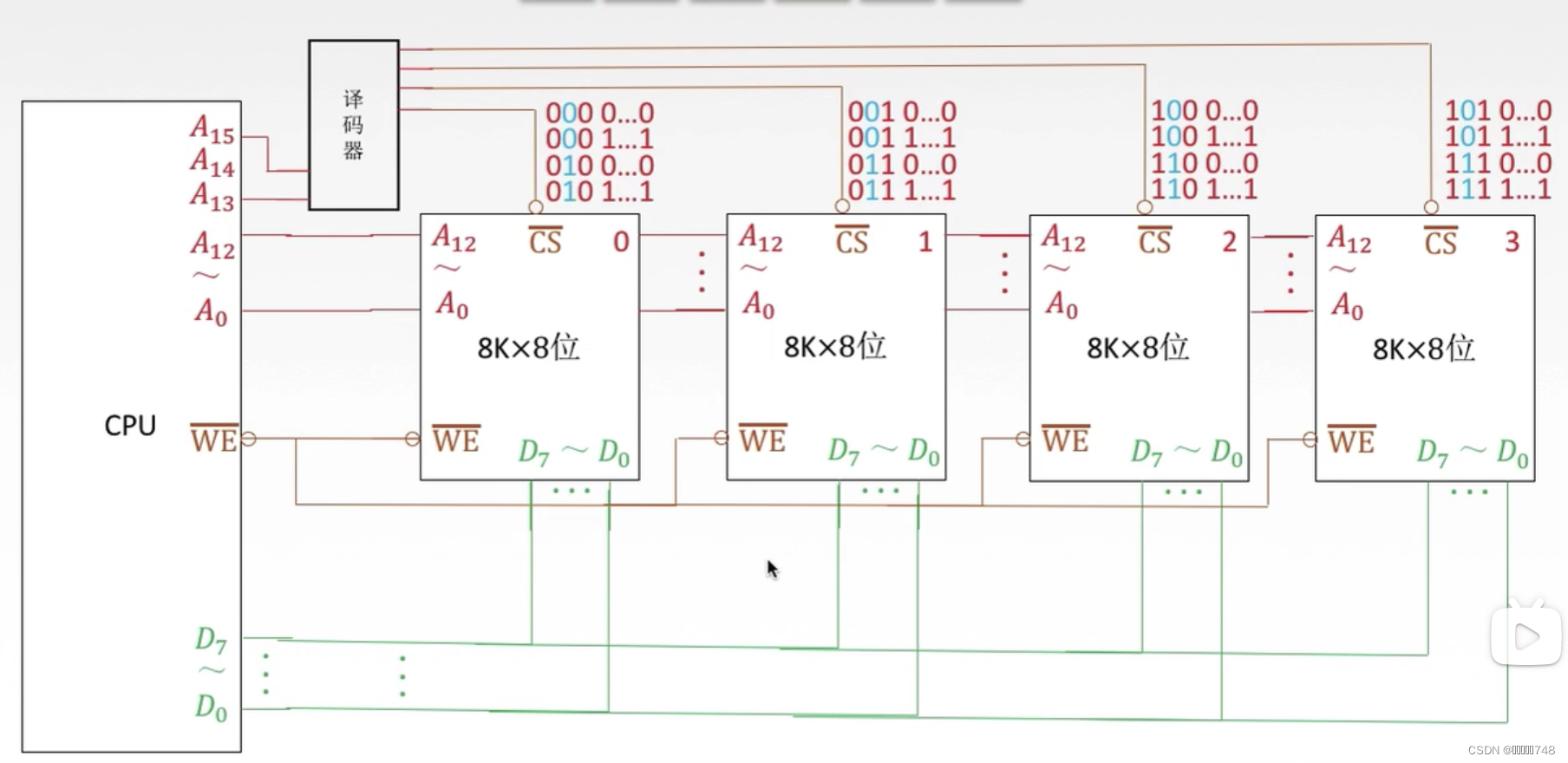

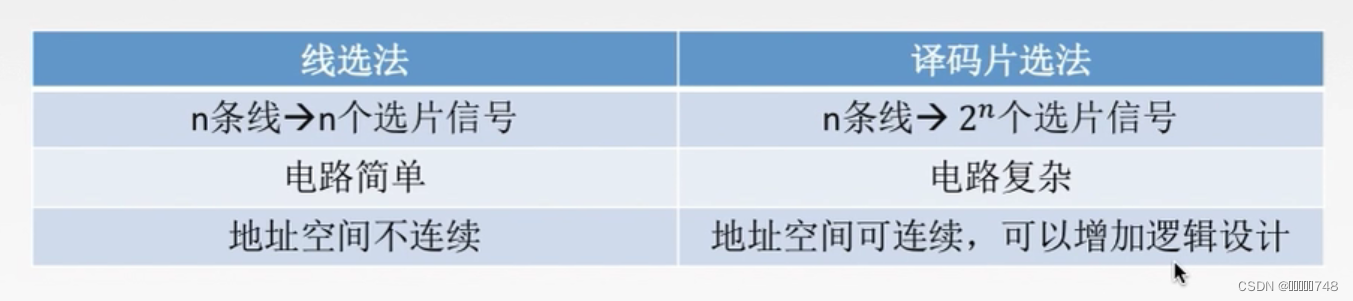

主存容量扩展-字扩展

总结

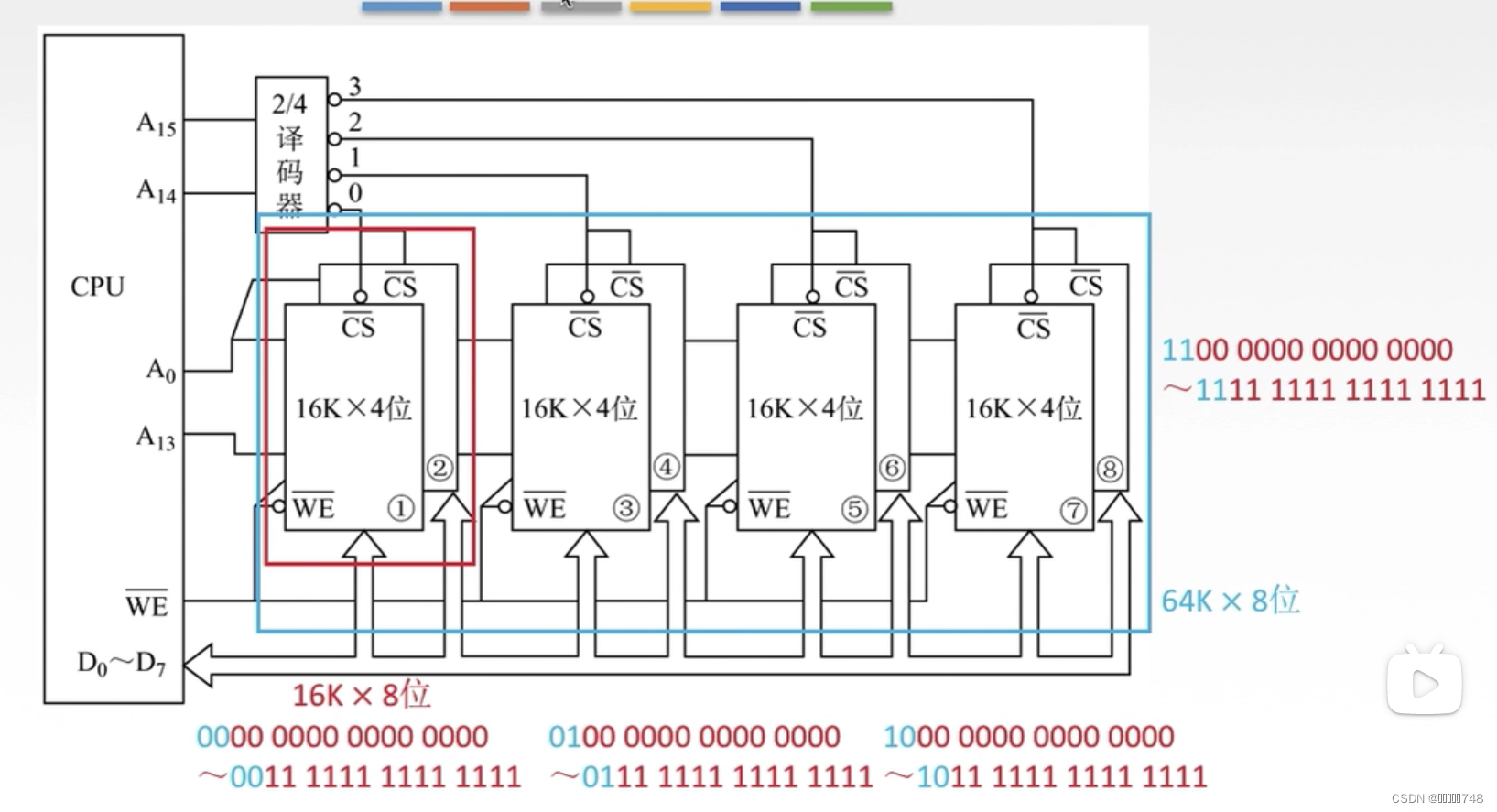

字、位同时扩展

总结

习题

总结

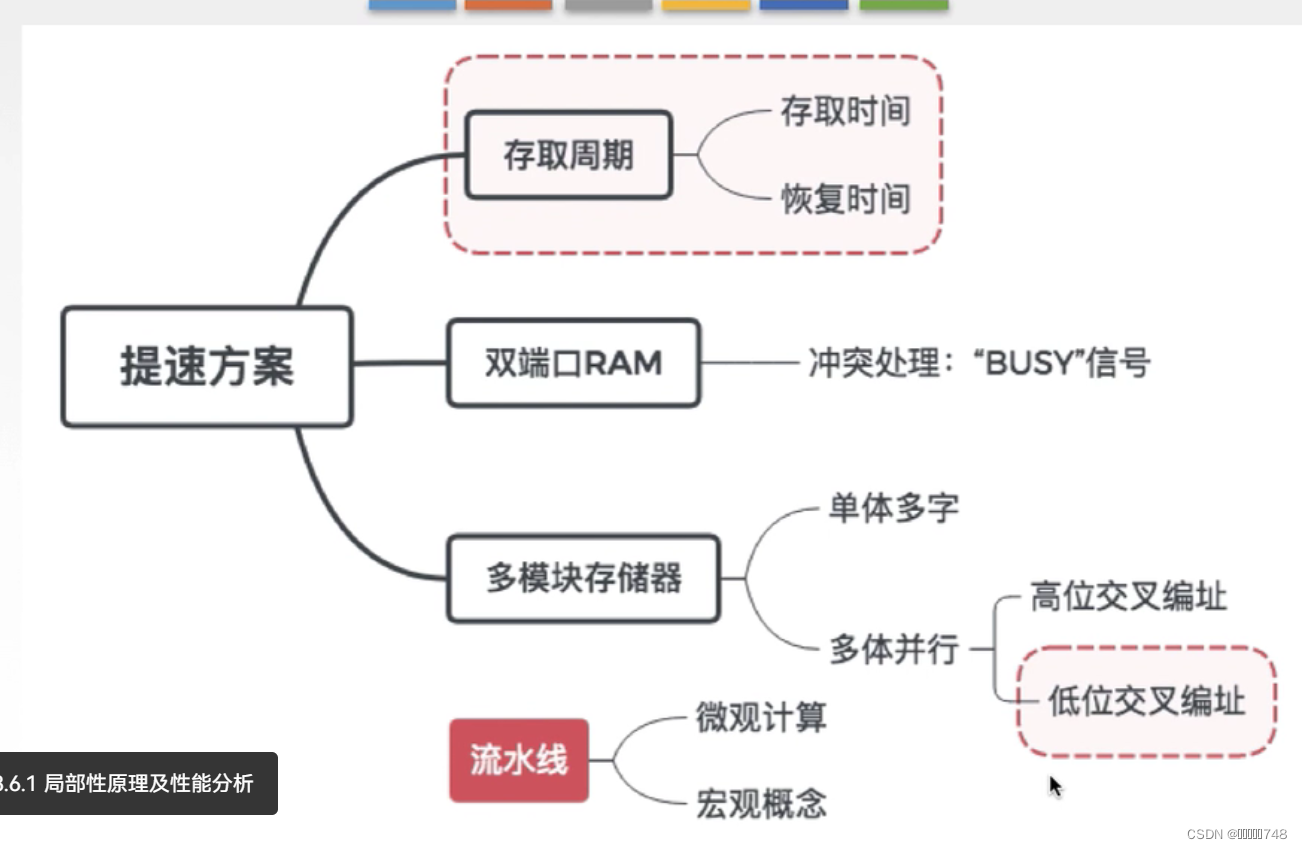

双口RAM和多模块存储器

存储器

存储器的存储周期

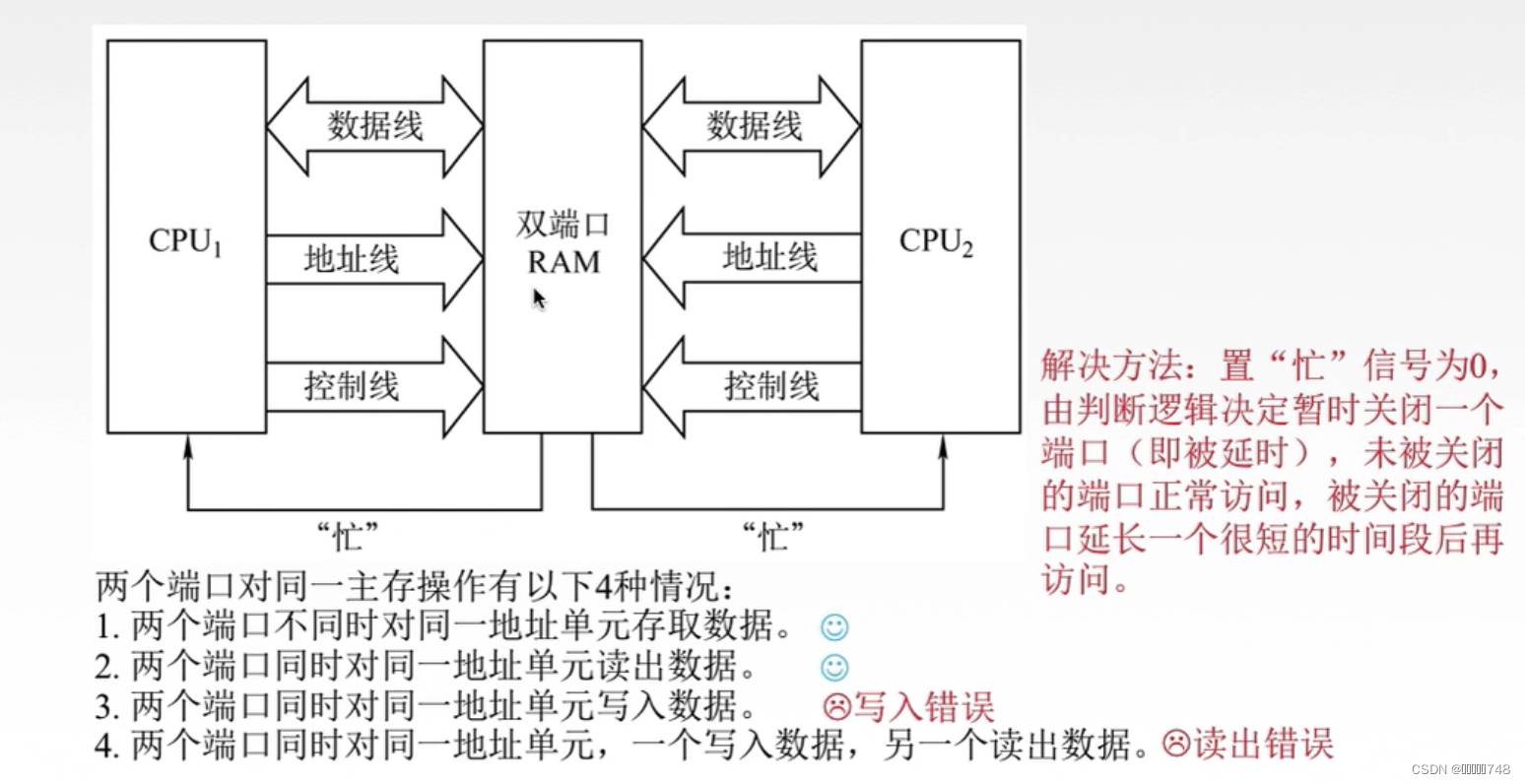

双端口RAM

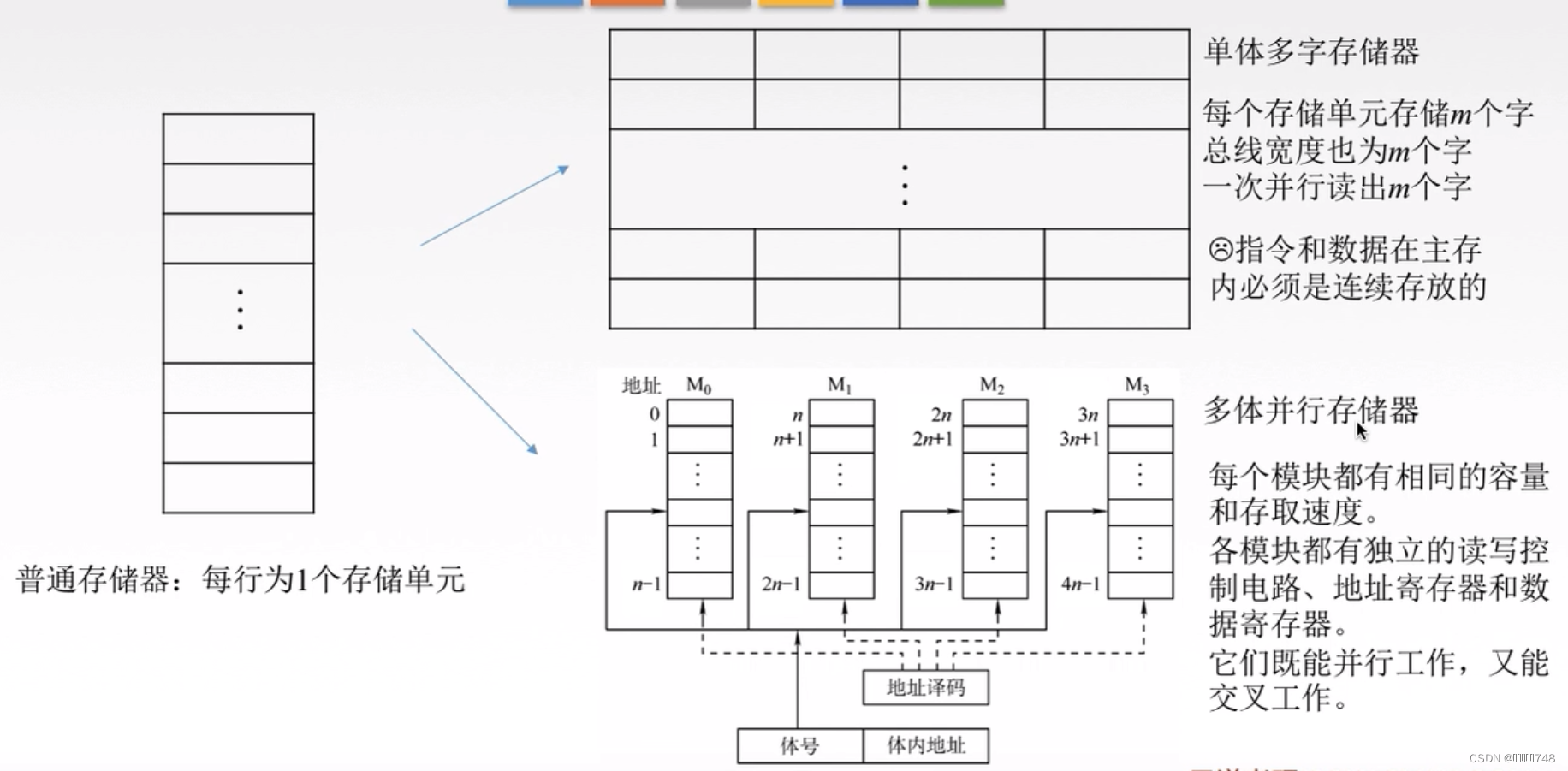

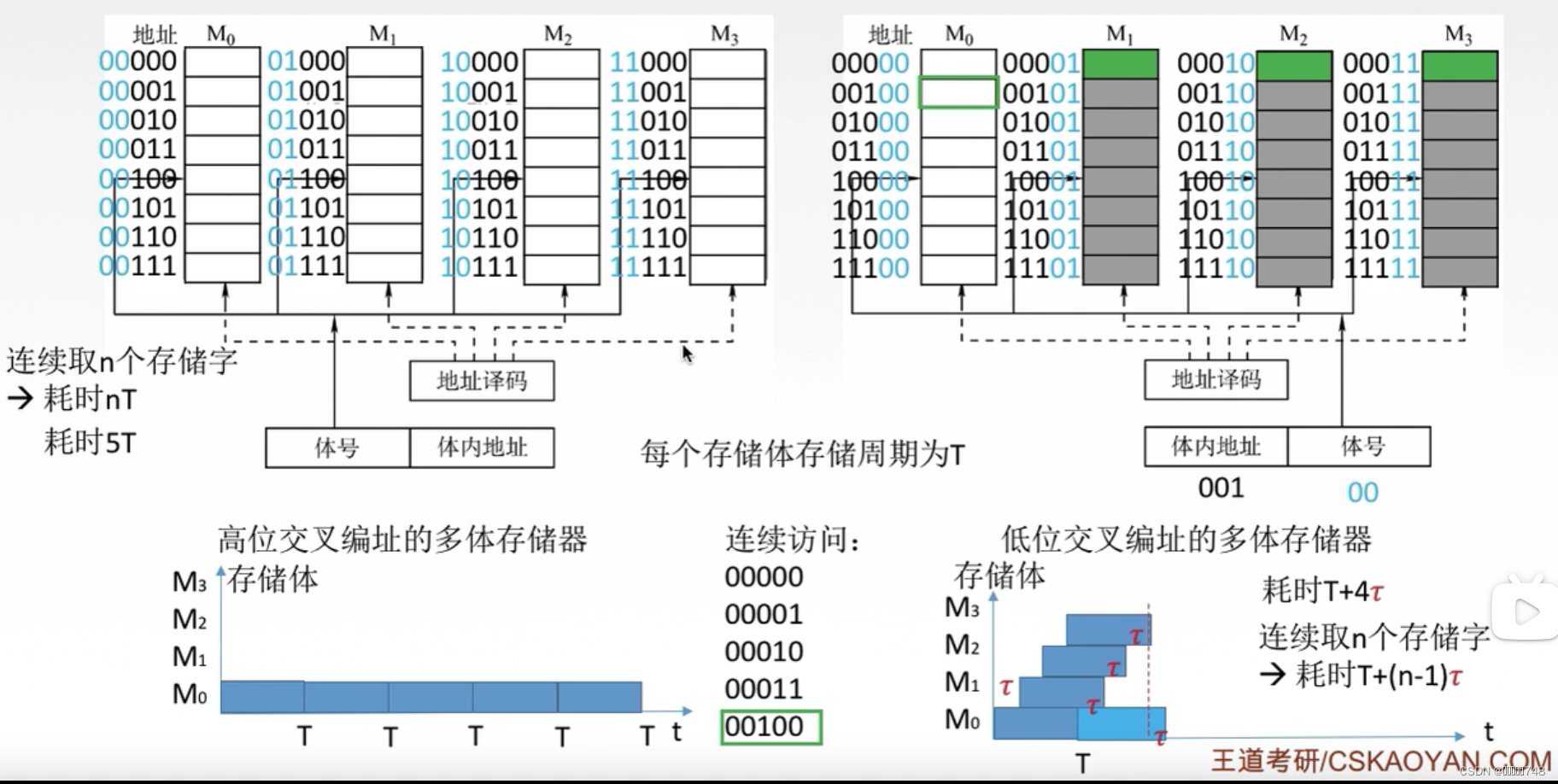

多模块存储器

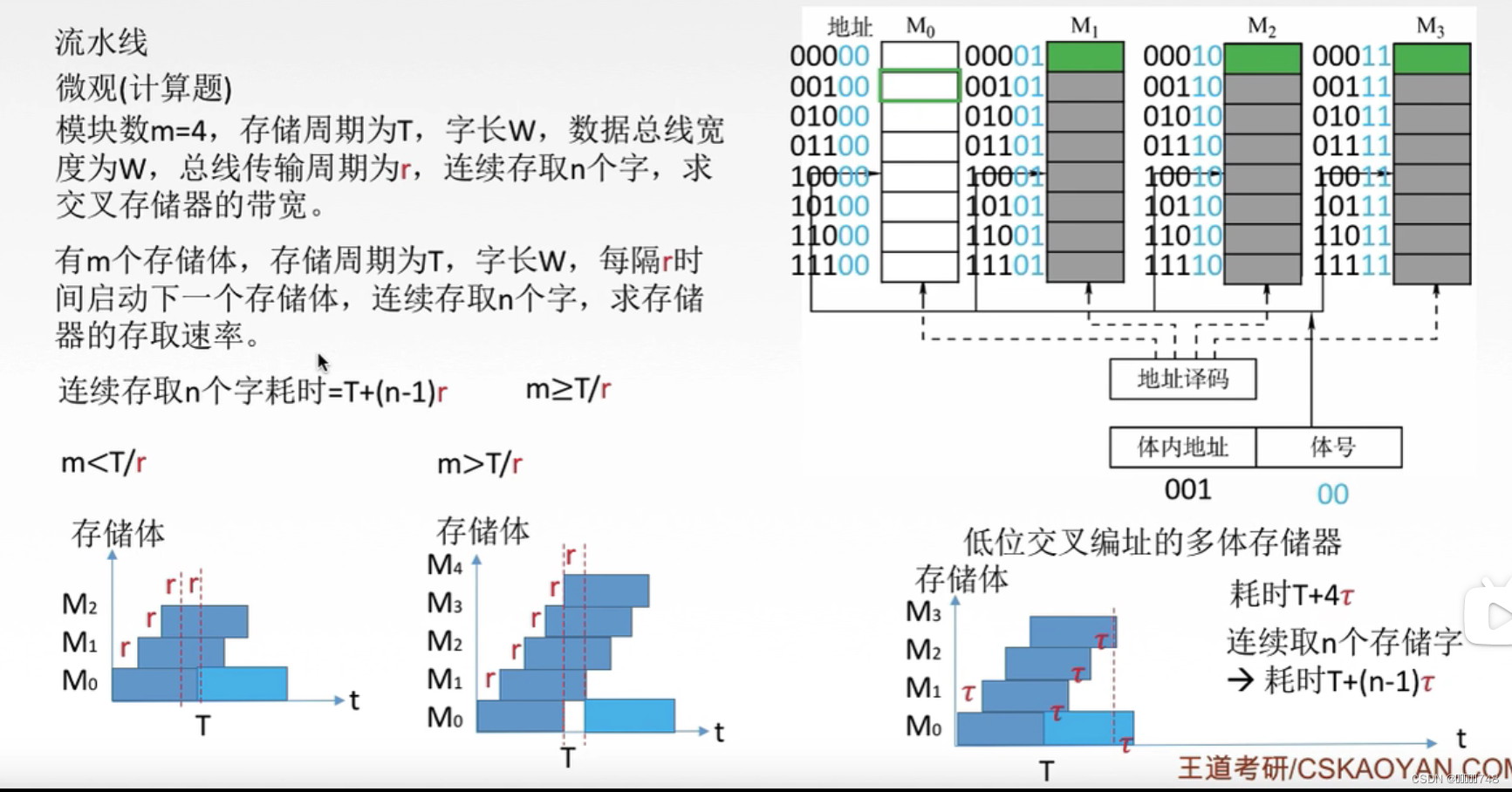

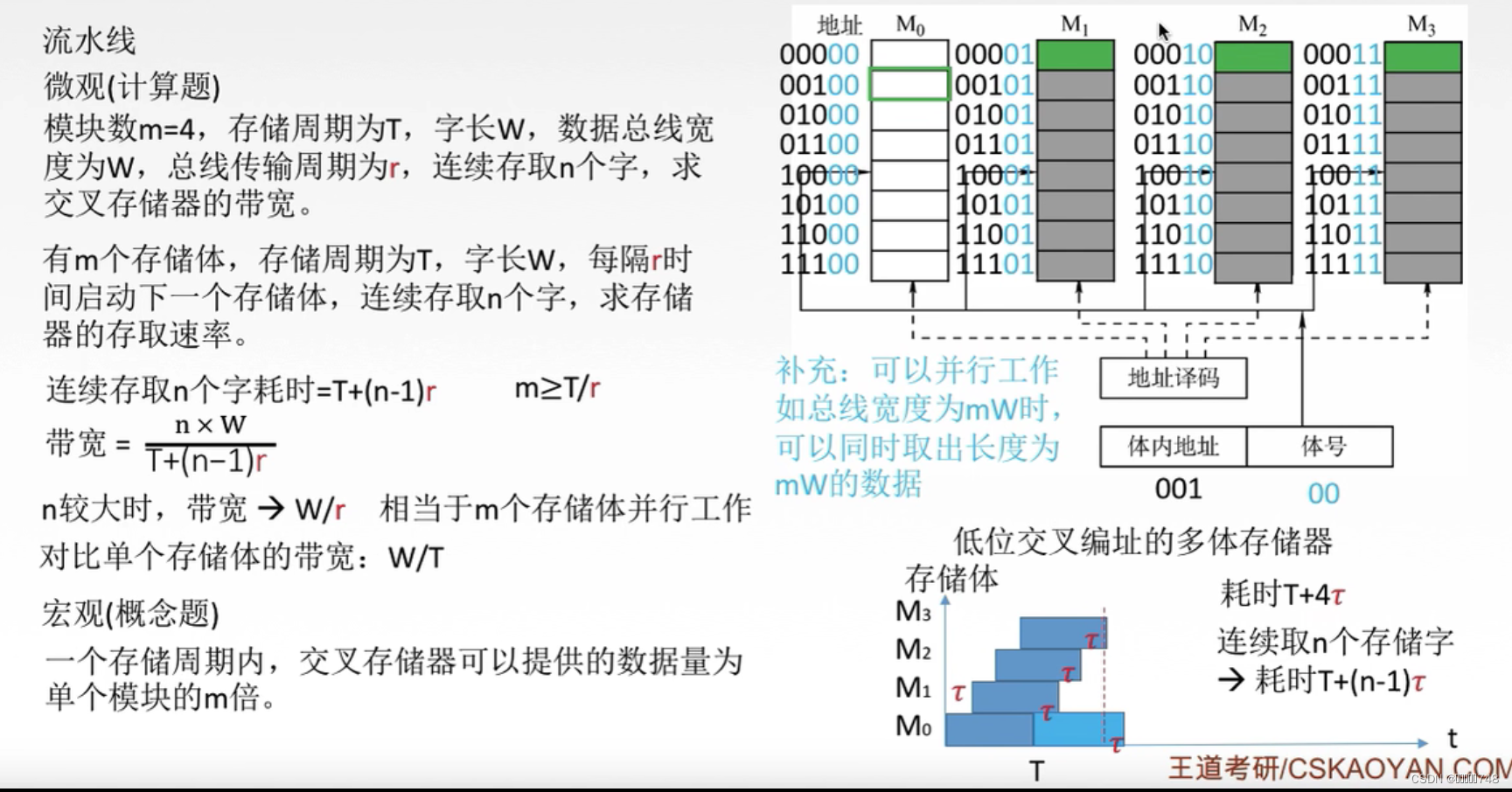

多体并行存储器

带宽:每秒内大概能传多少位的数据

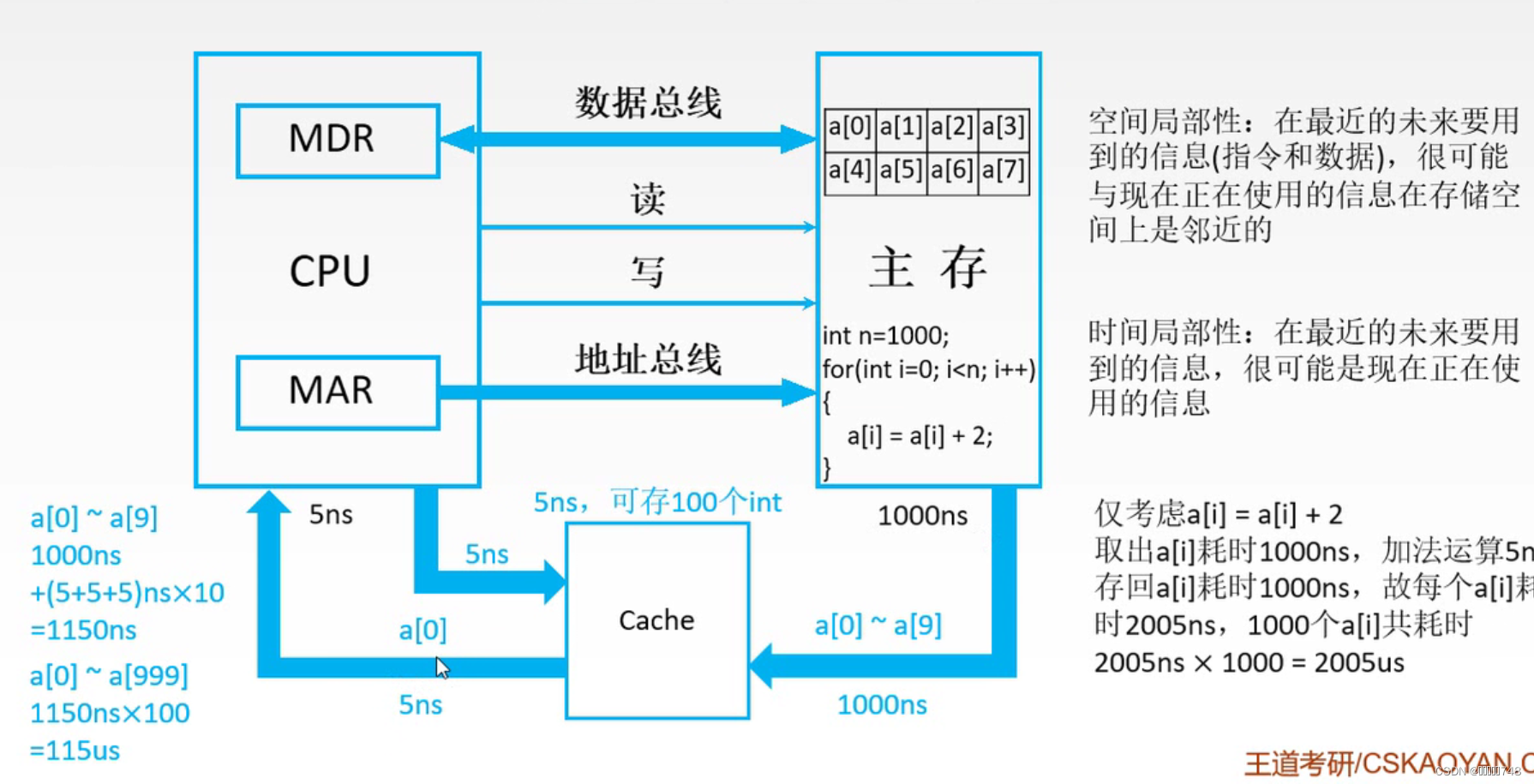

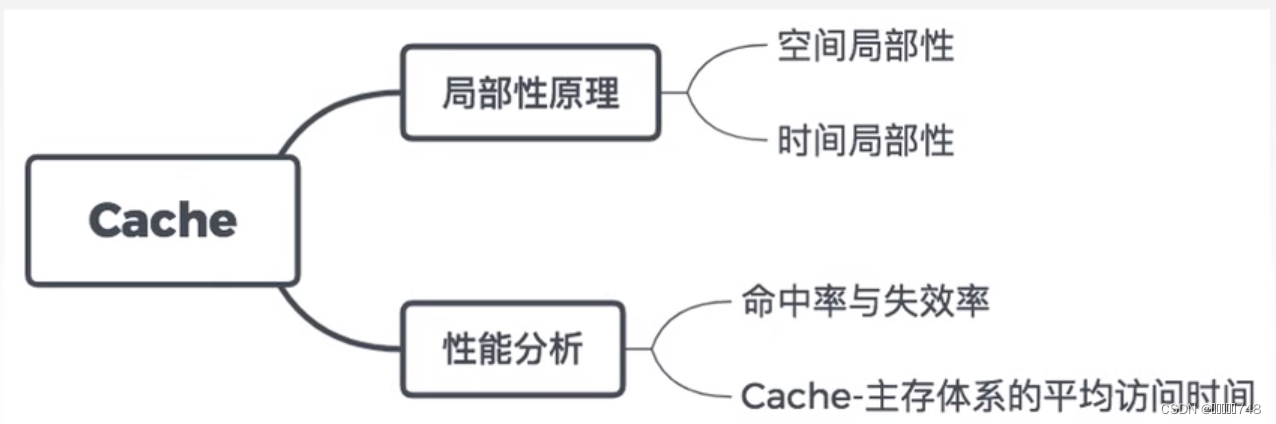

高速缓冲存储器——局部性原理及性能分析

局部性原理

CPU和主存之间数据的传输是通过寄存器来操作的,但是寄存器的位数有限,所以CPU一次只能取出主存里面的一个数据。而主存和Cache之间没有这种限制,他们之间的传输可以以块为单位,块里面数据的个数通常是2^n个。

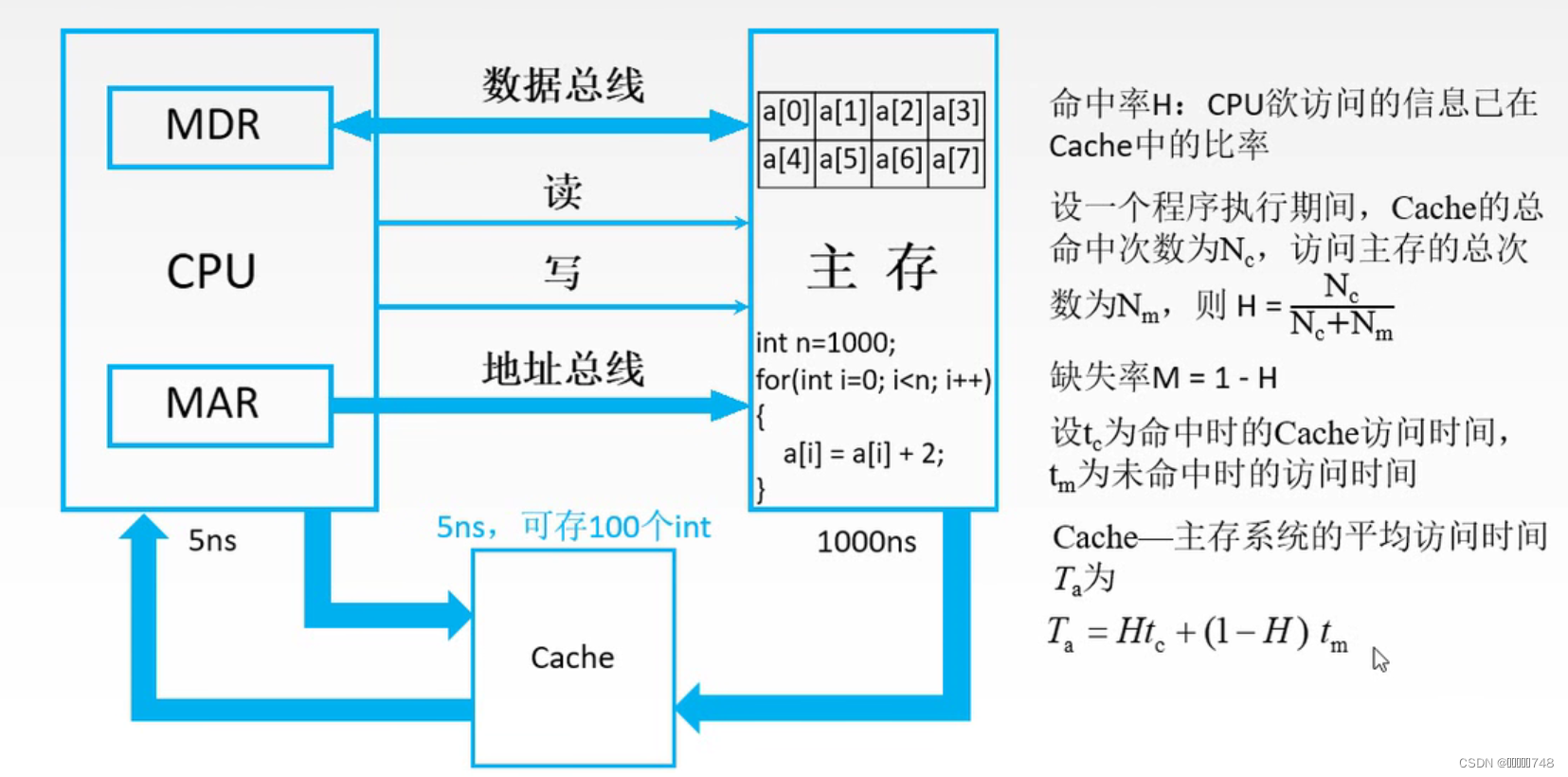

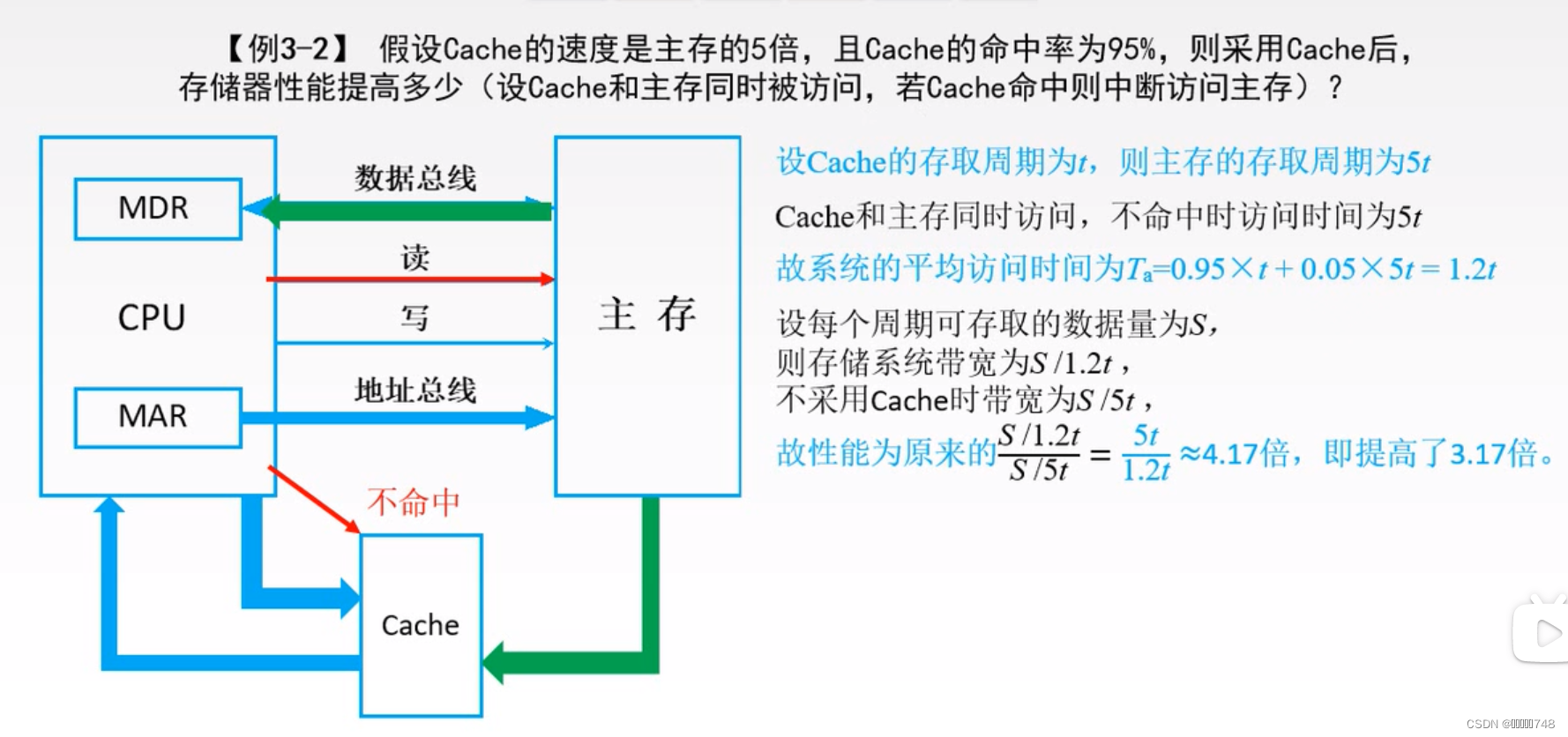

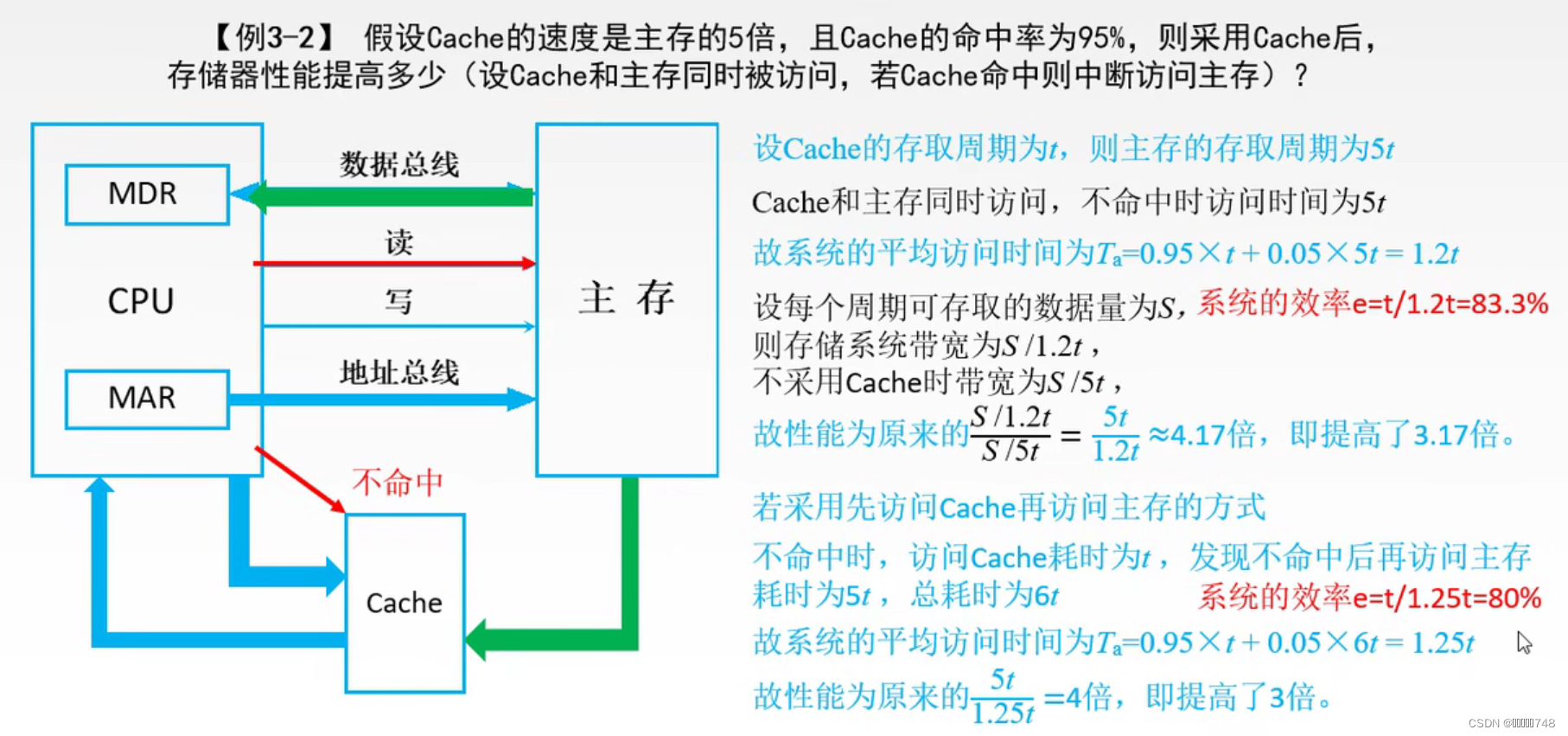

性能分析

未命中的时间包括两种:1.数据从主存先传到Cache,再传到CPU。2.数据从主存同时传到Cache和CPU。

习题

系统的效率:Cache的时间/系统的平均访问时间

总结

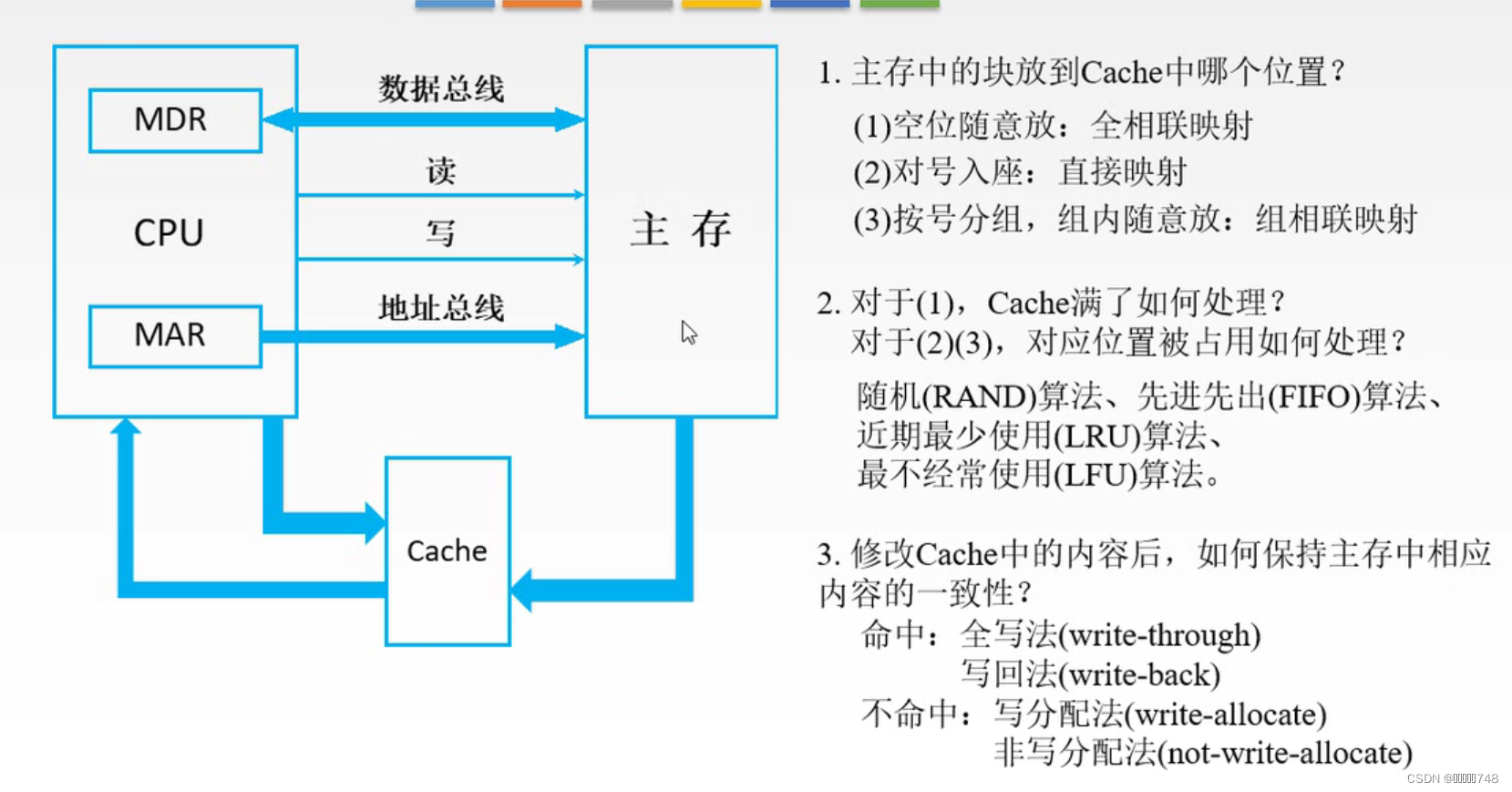

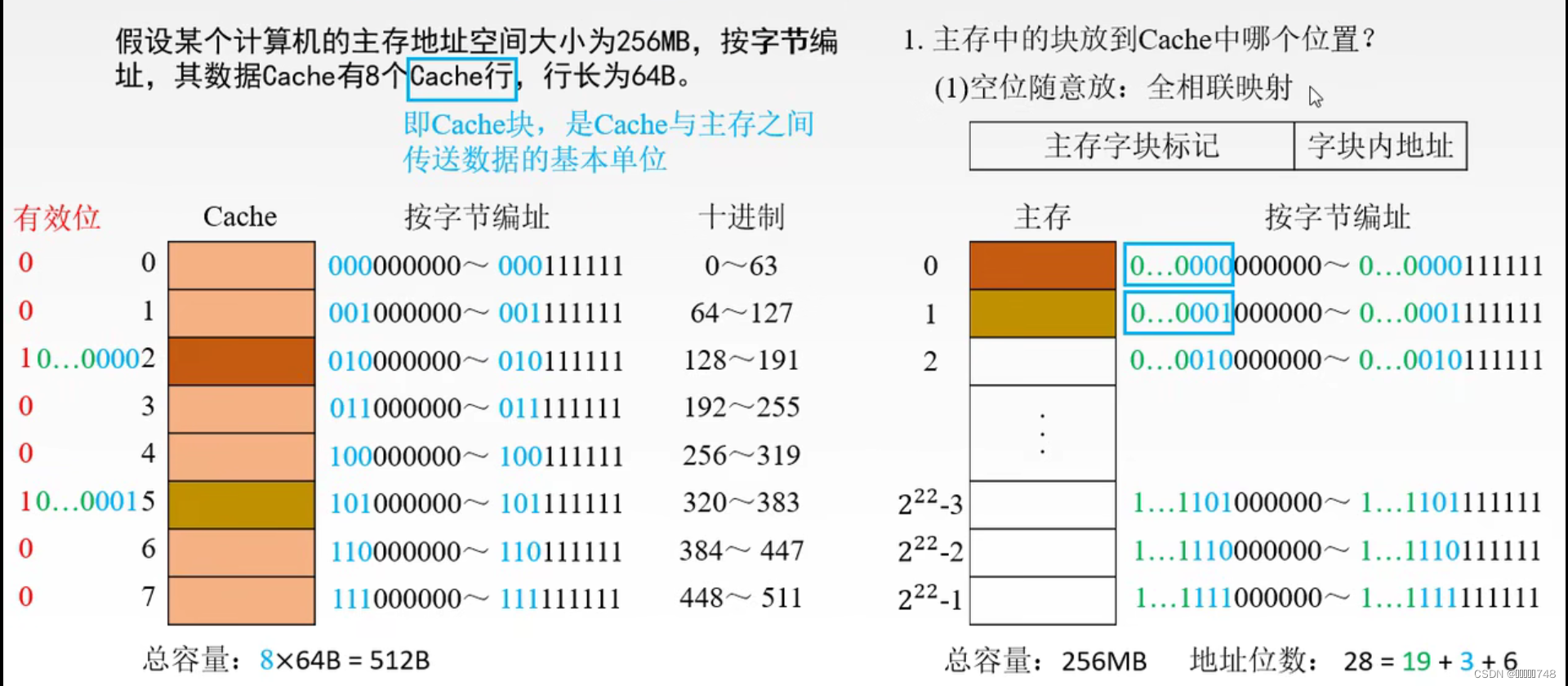

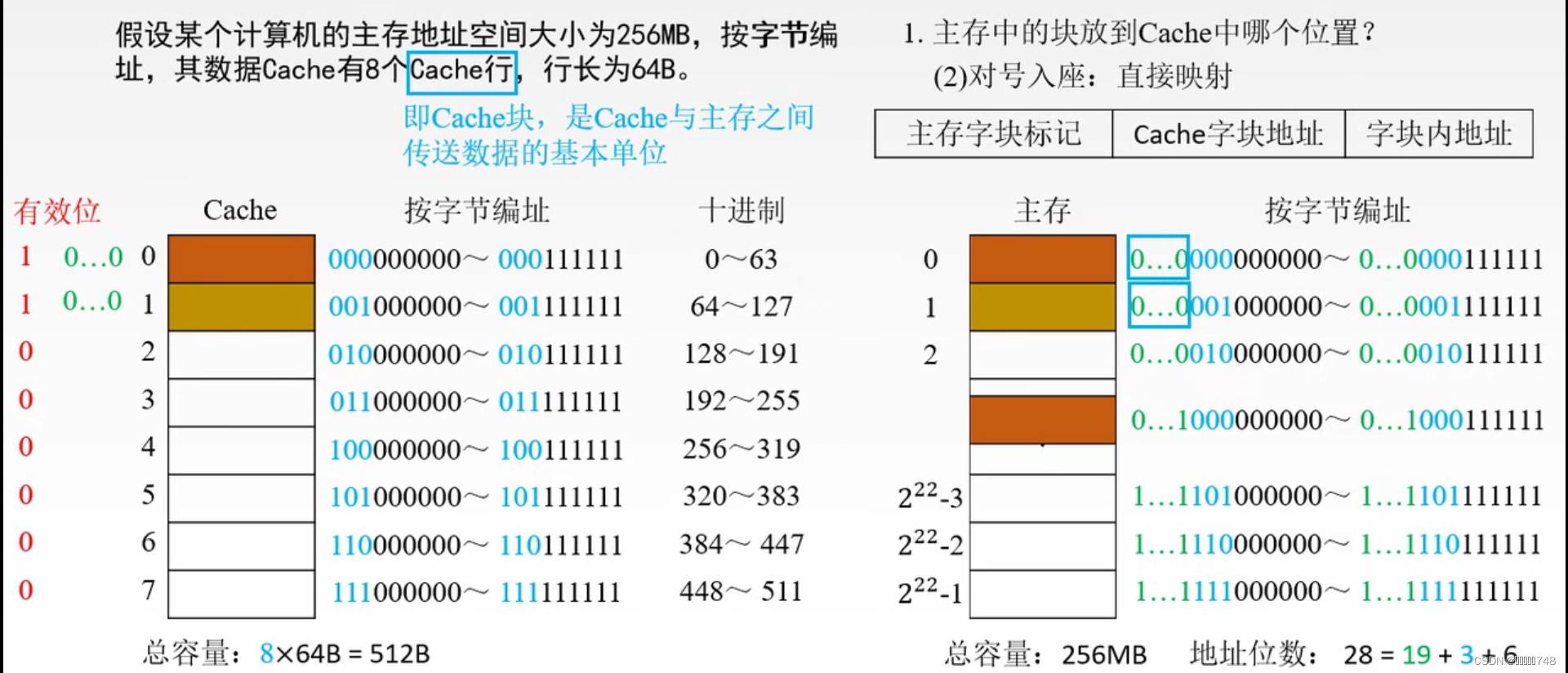

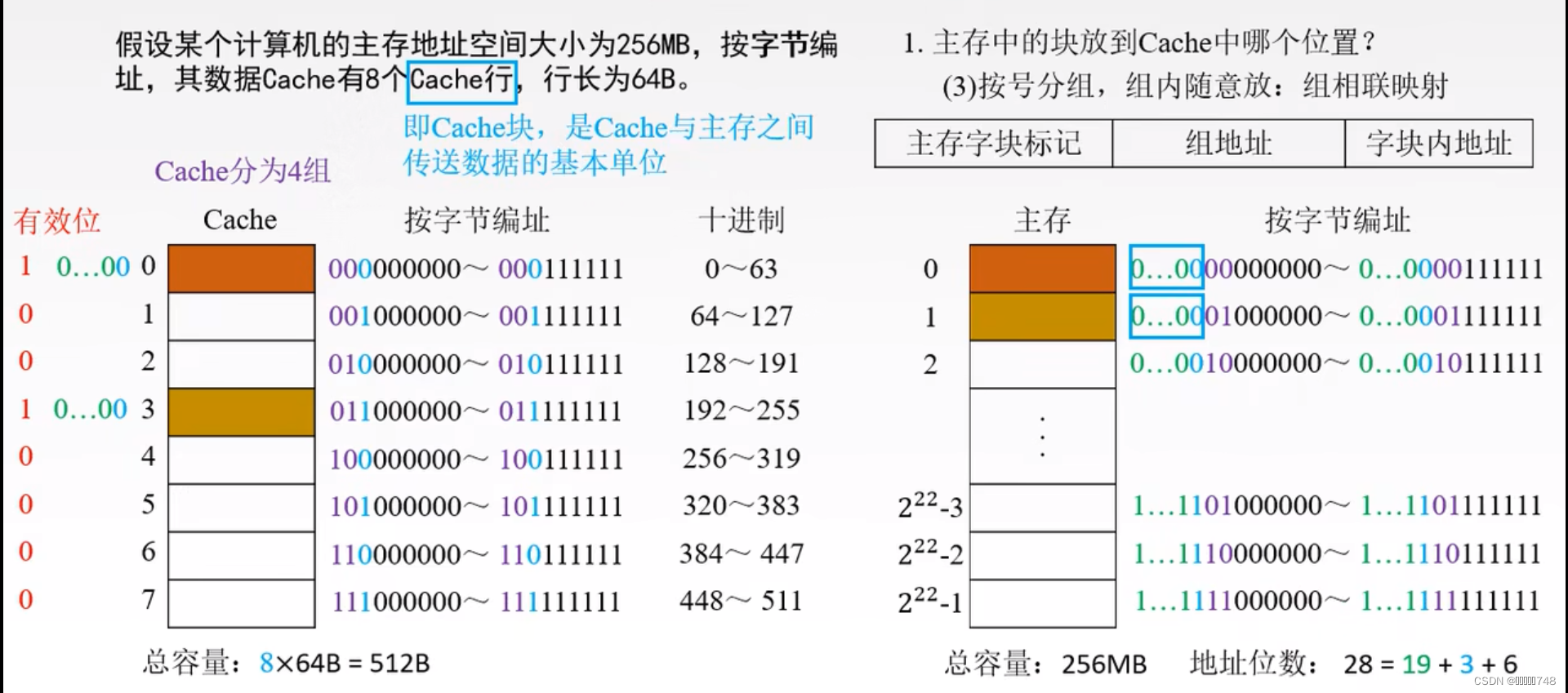

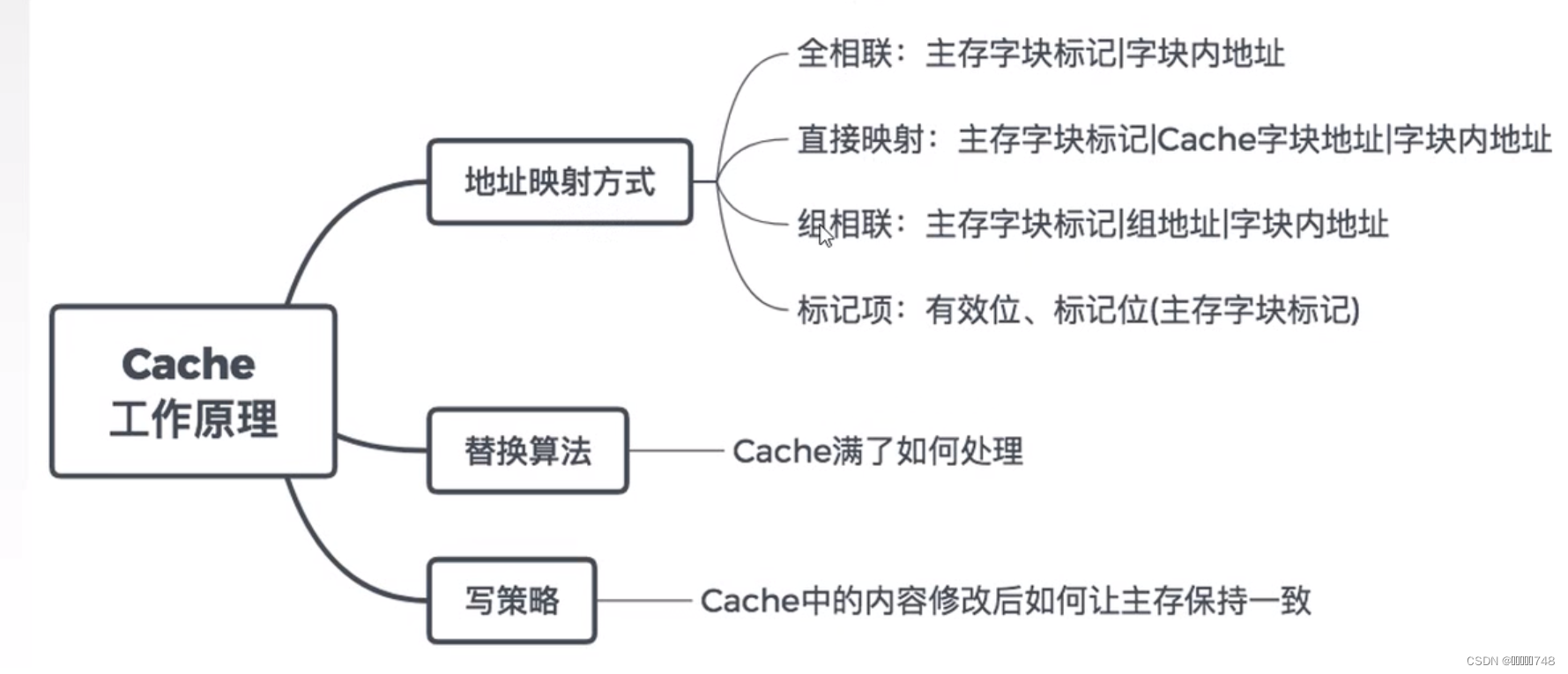

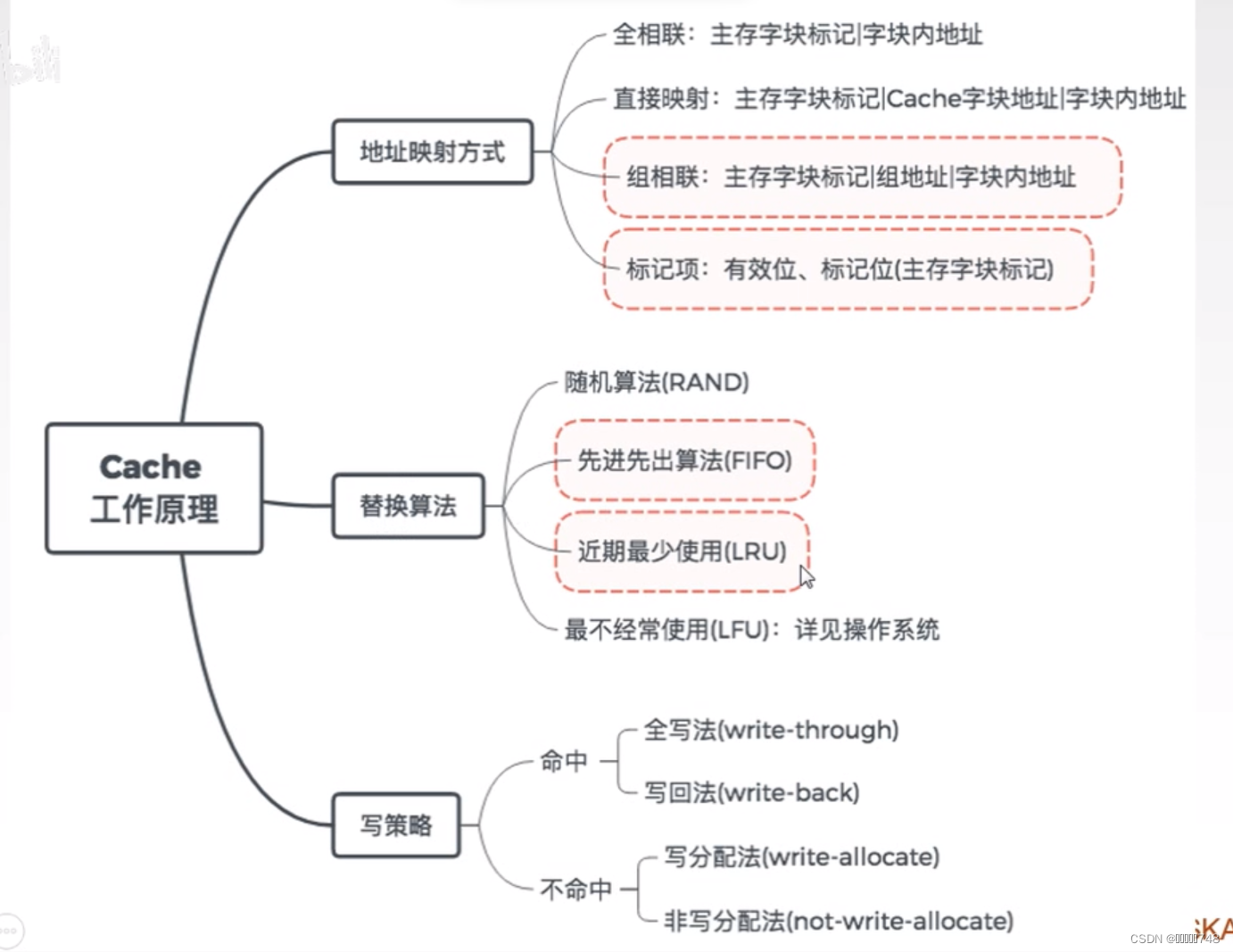

Cache-地址映射

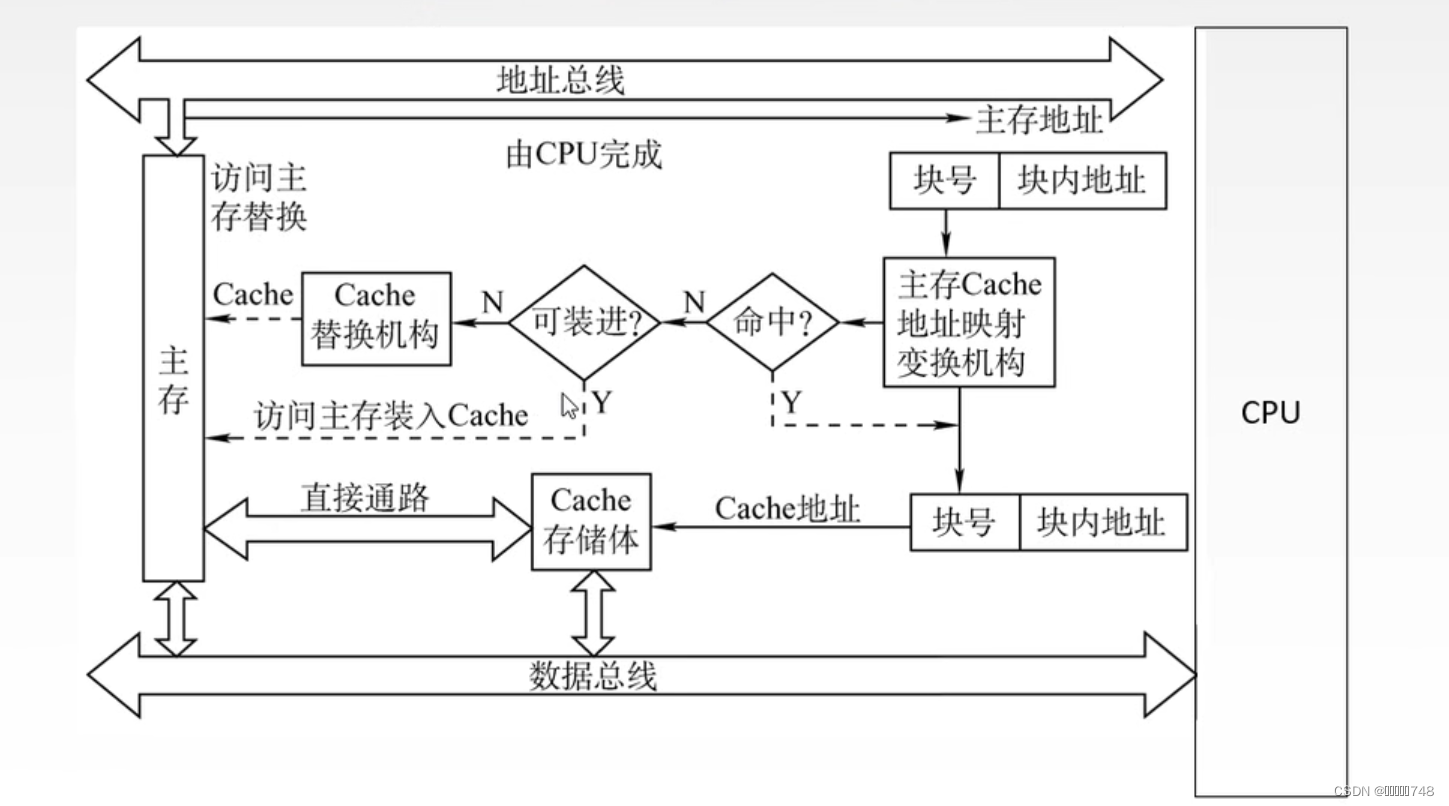

Cache的基本工作原理

地址映射

全相联映射

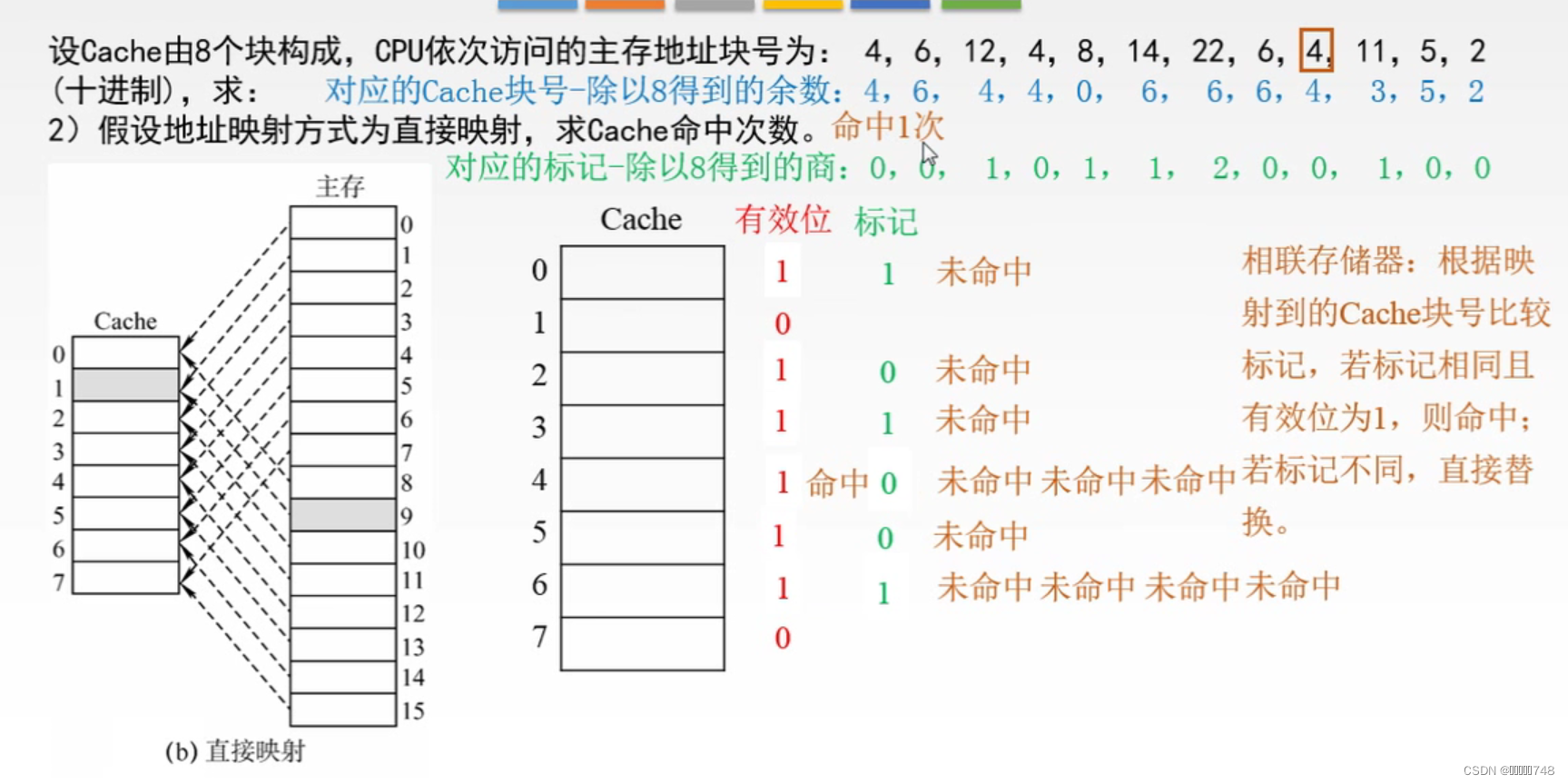

直接映射法

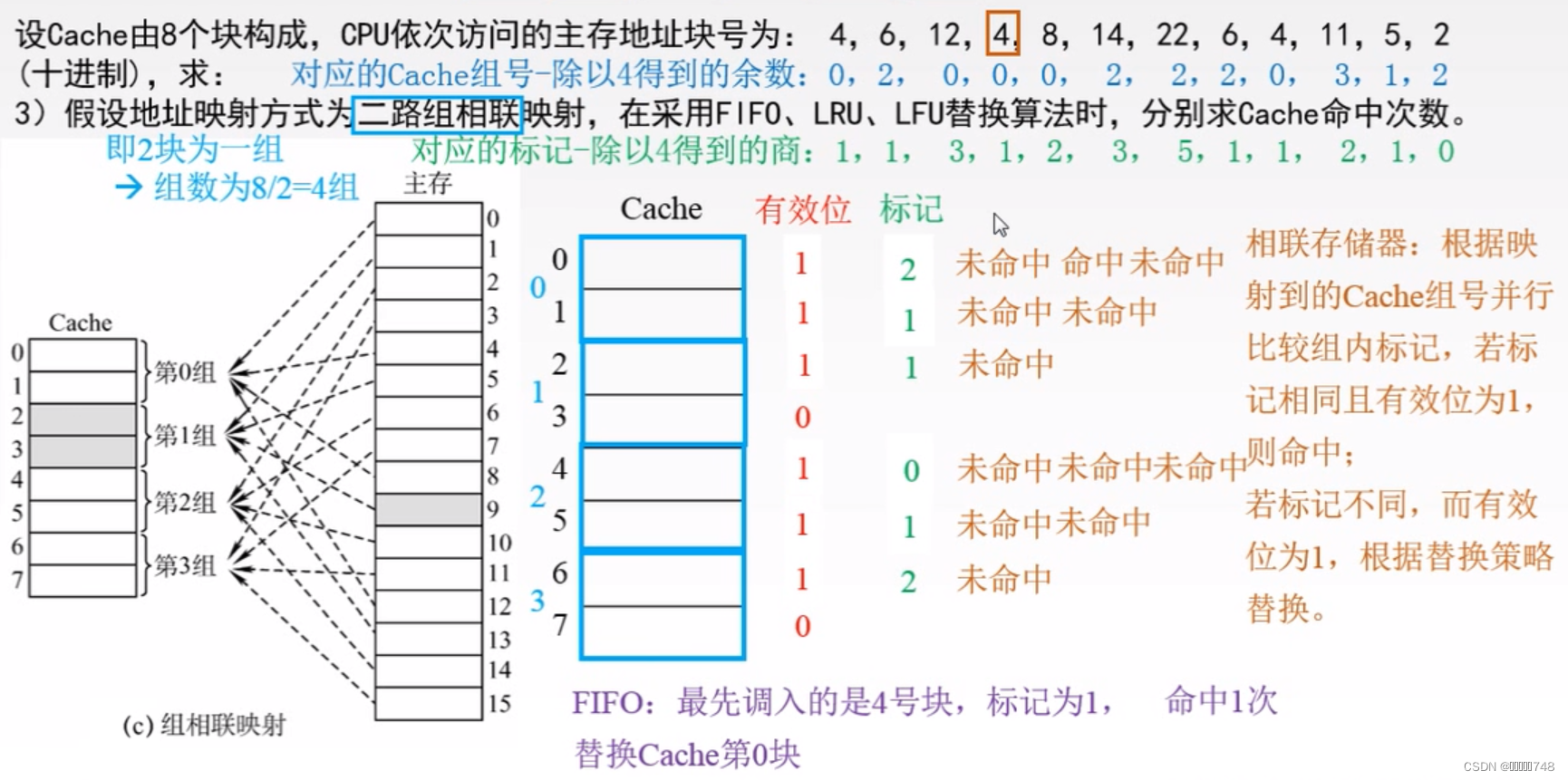

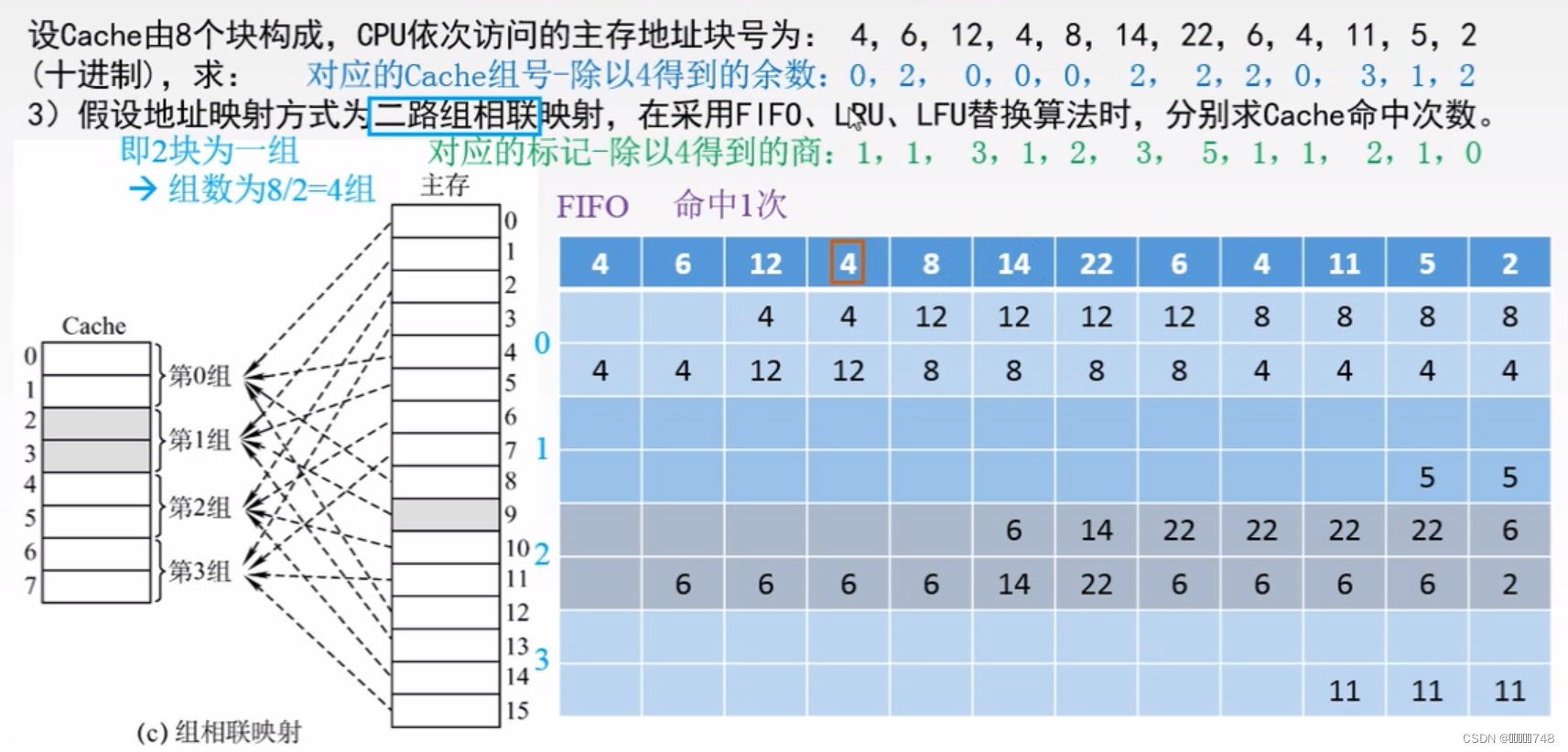

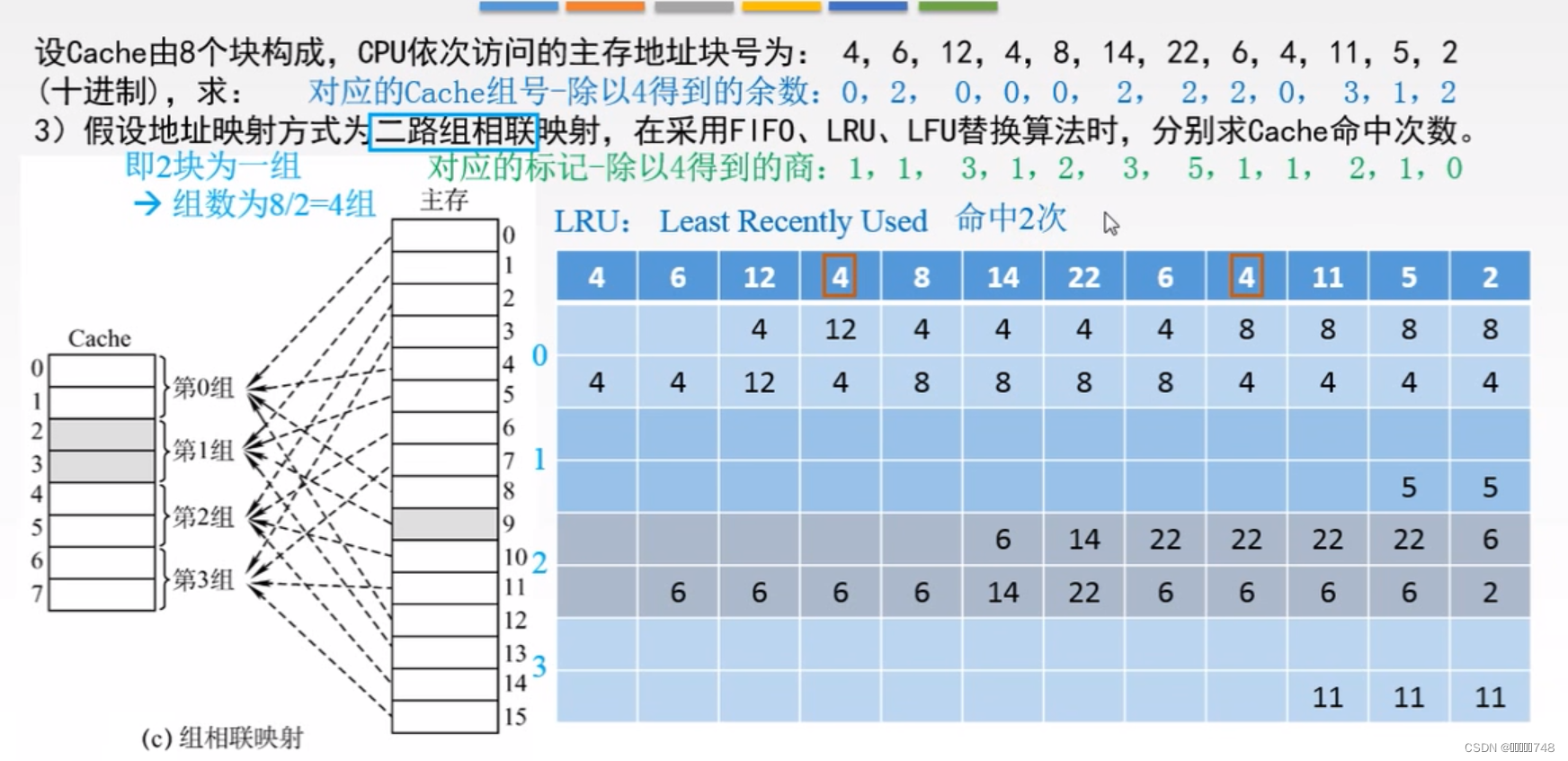

组相联映射法

对比

总结

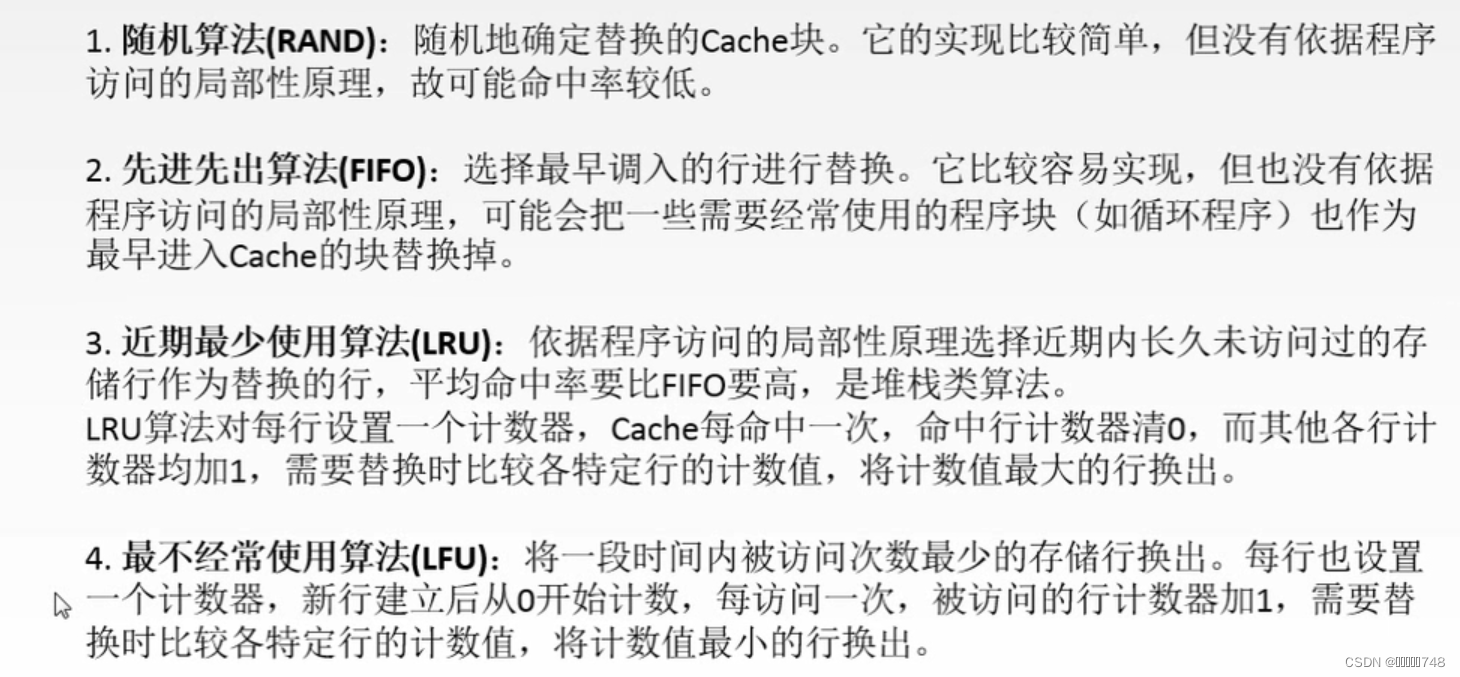

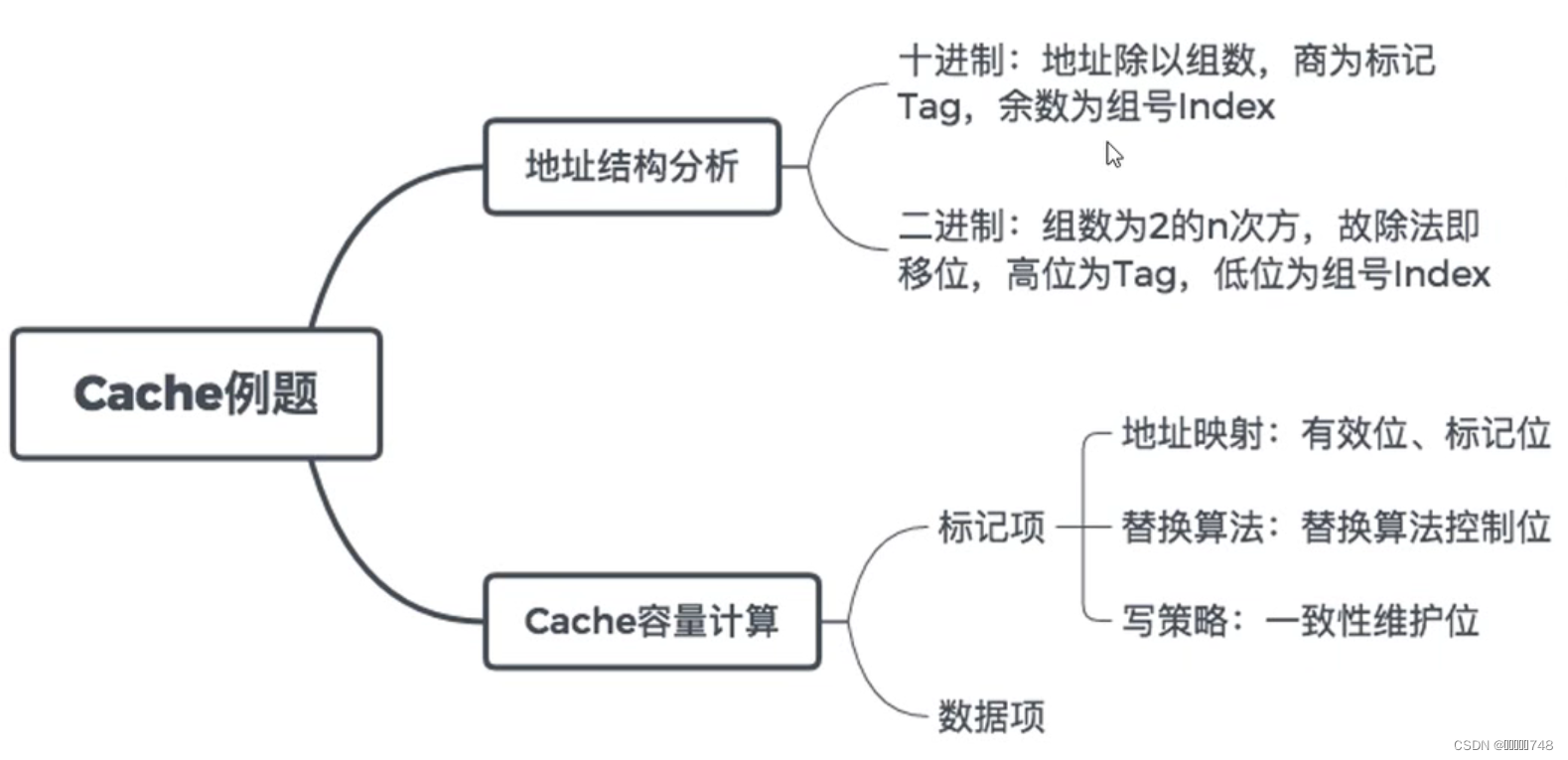

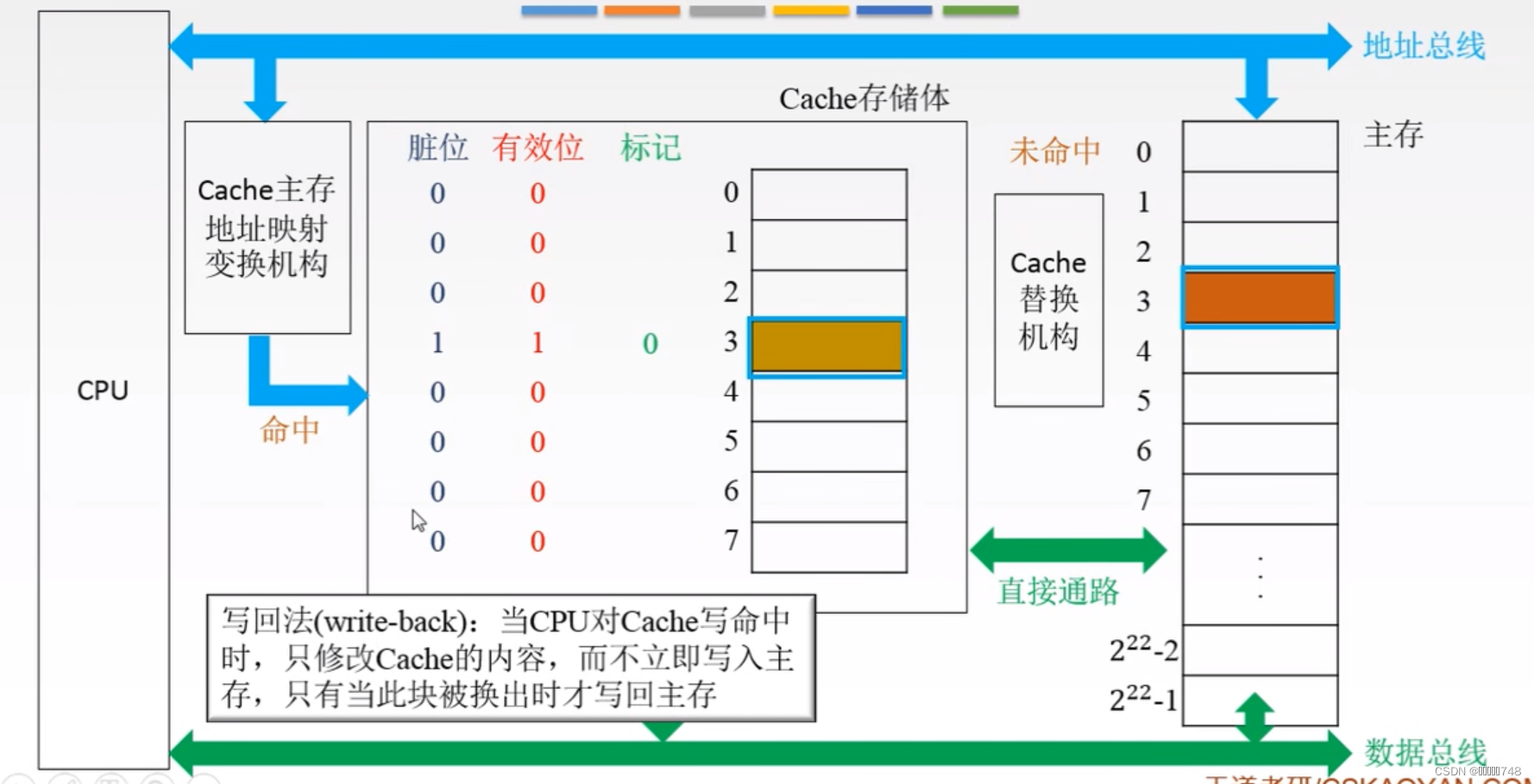

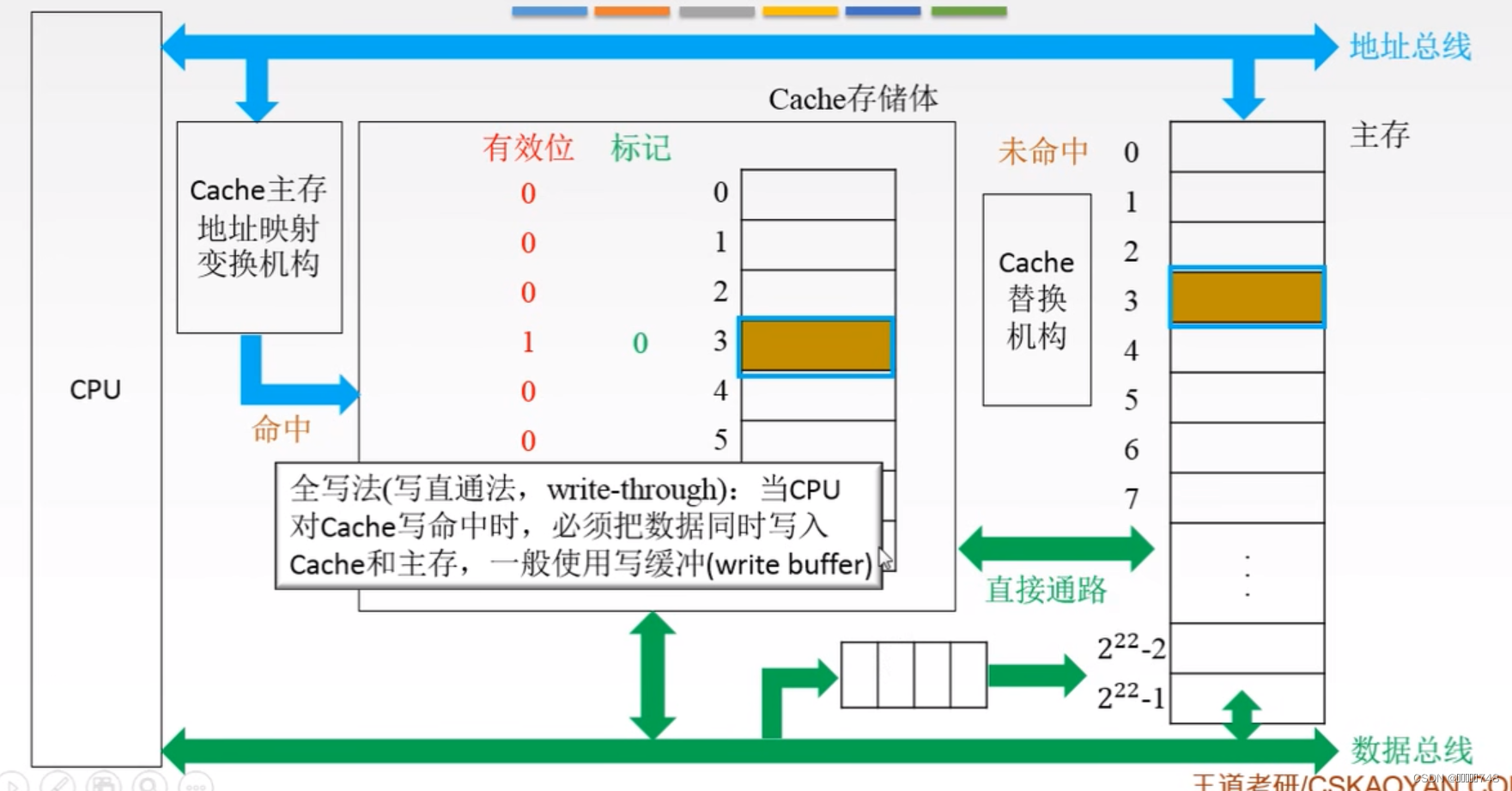

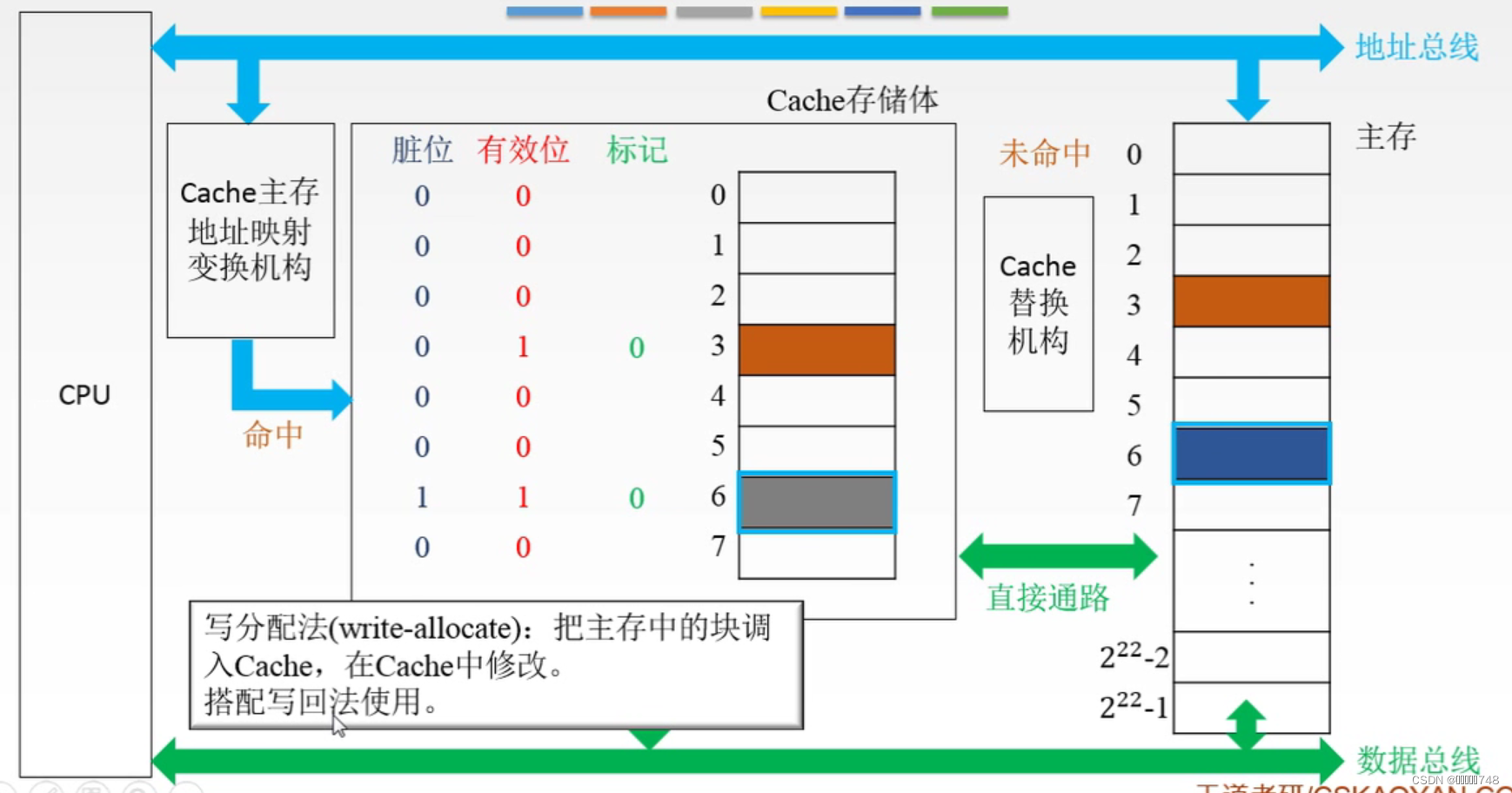

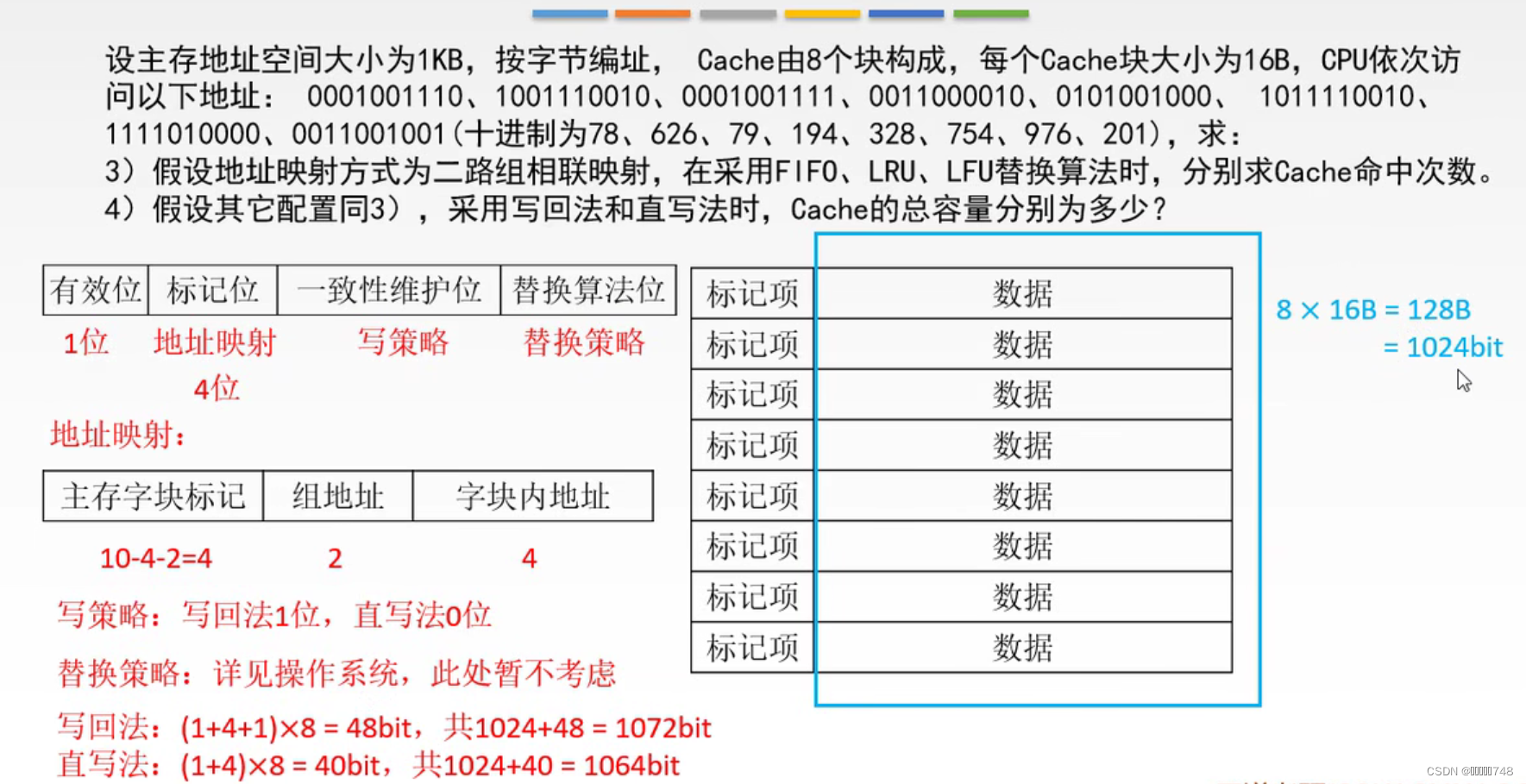

Cache-替换算法及写策略

替换算法

习题

命中三次

先进先出替换法

LRU

习题总结

总结

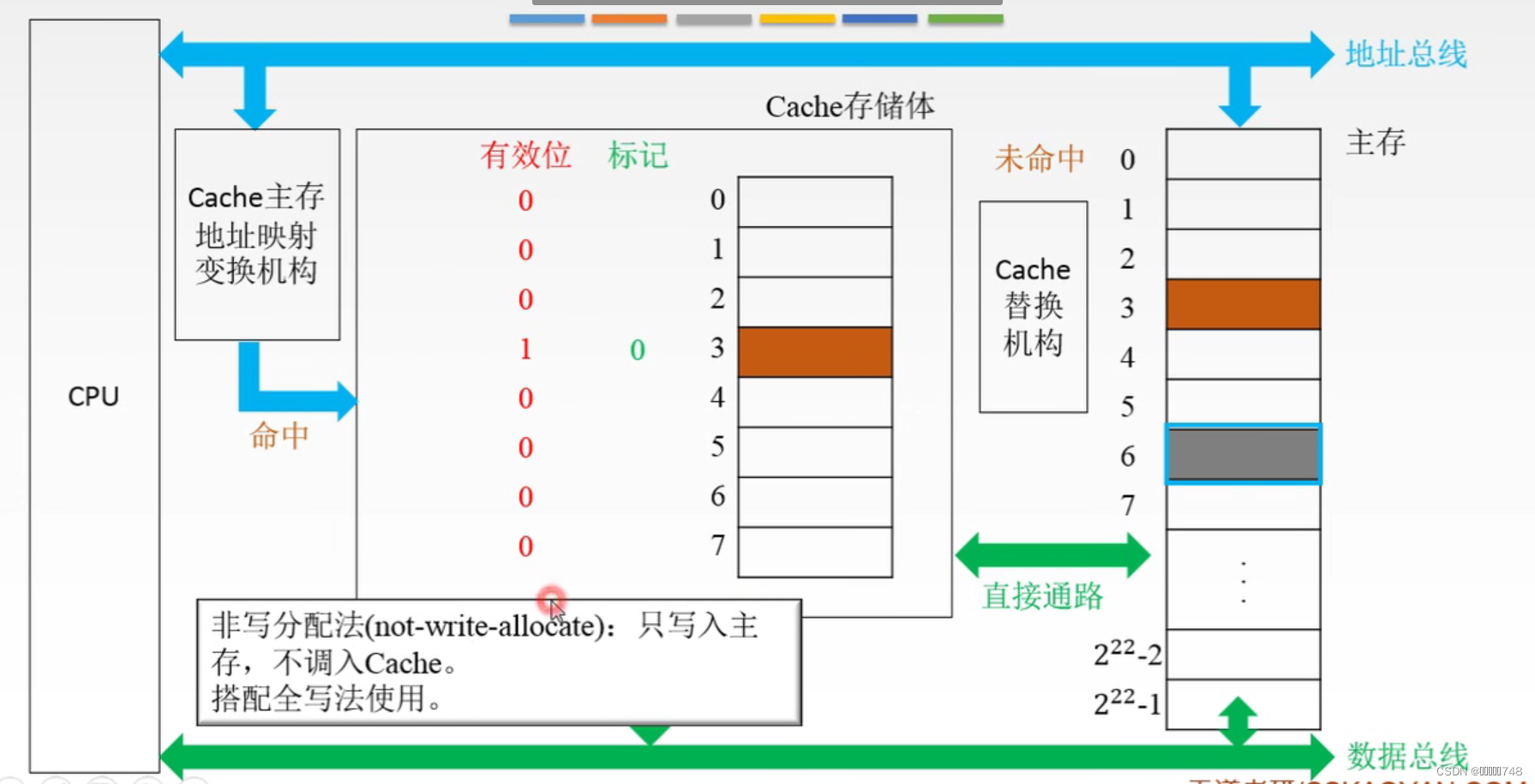

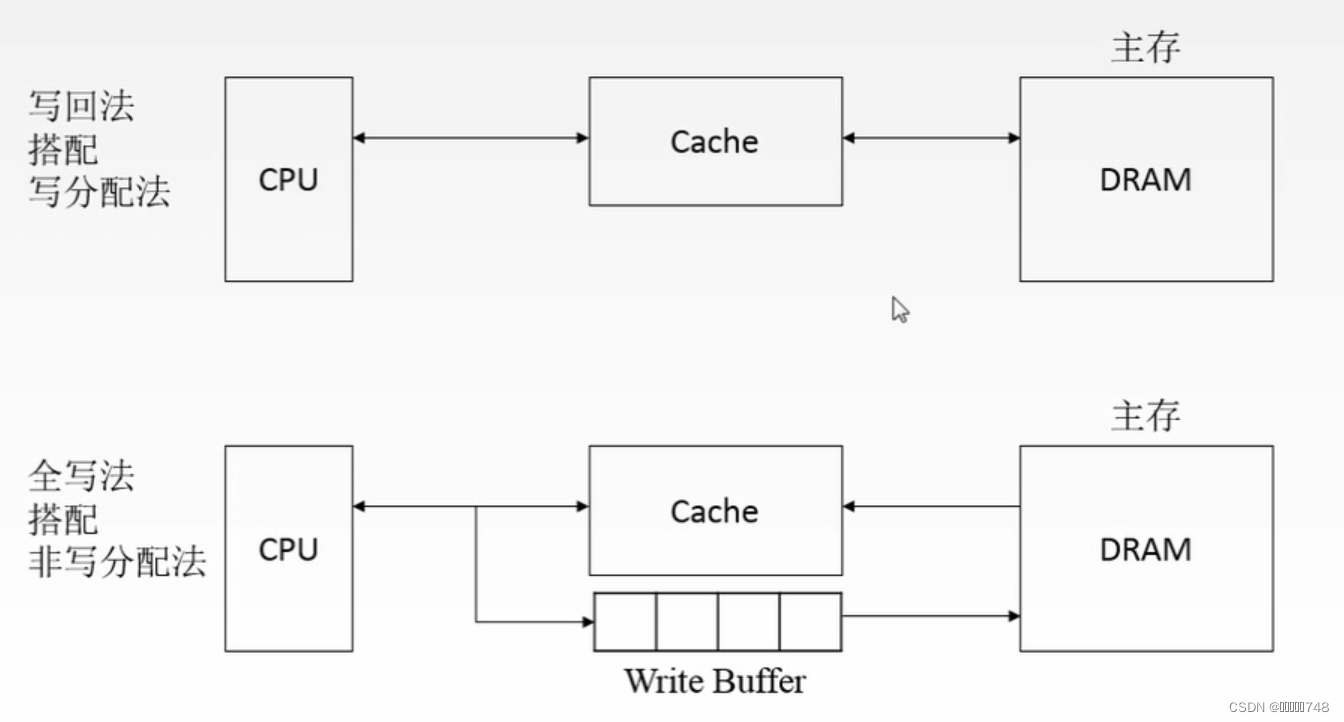

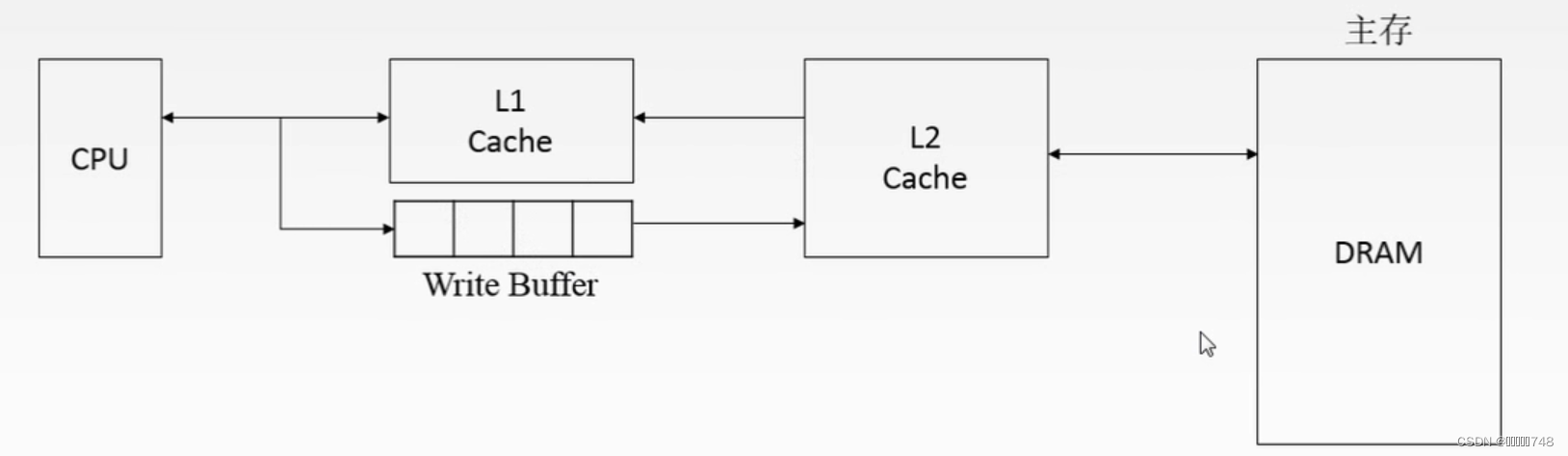

写缓冲

比较:

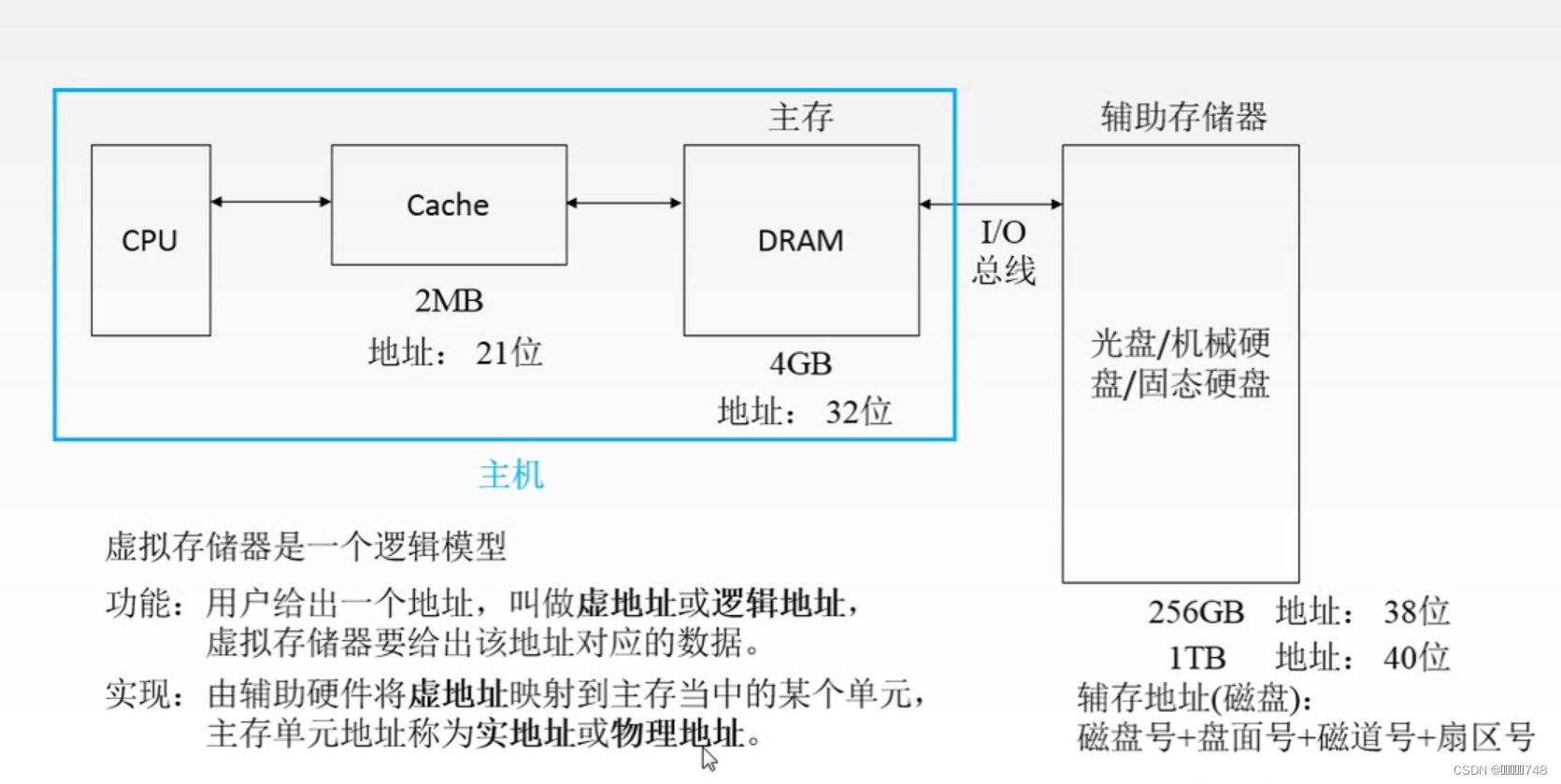

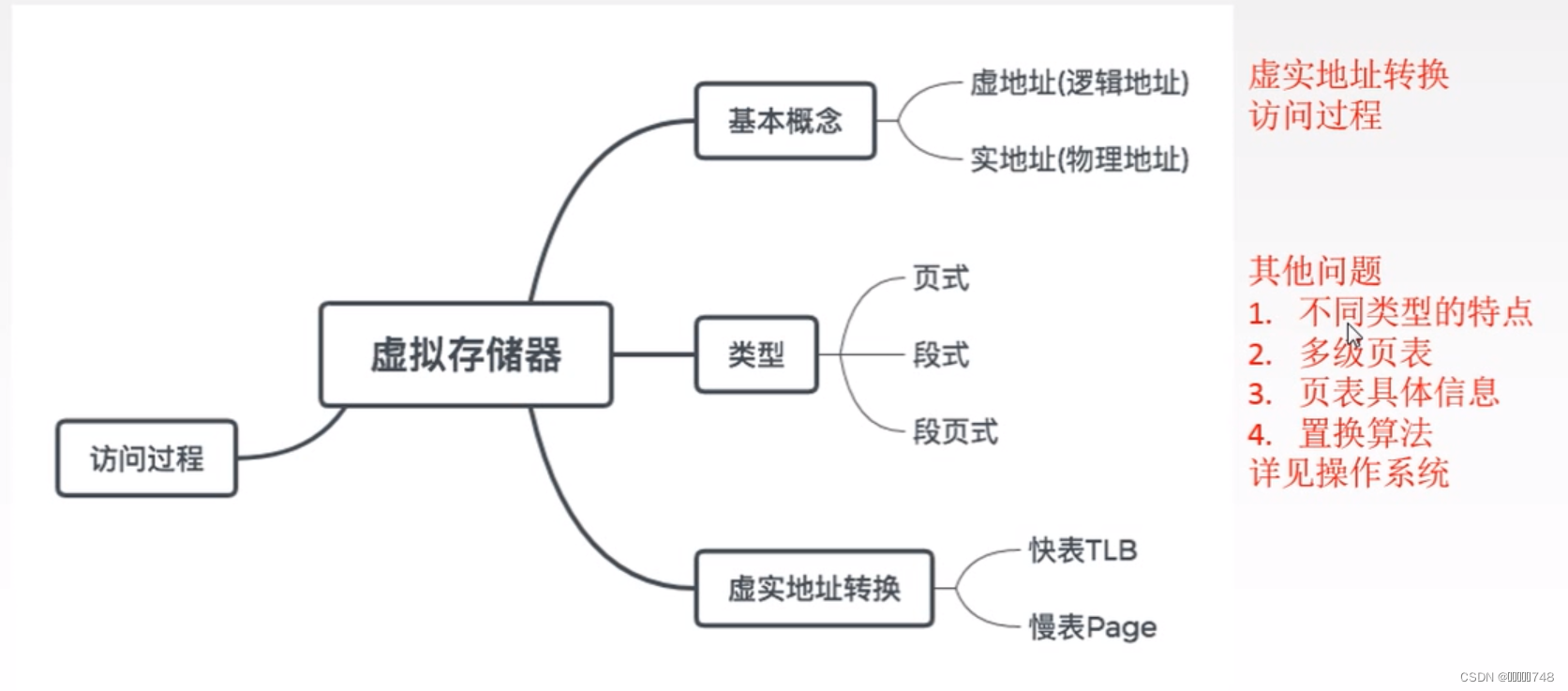

虚拟存储器

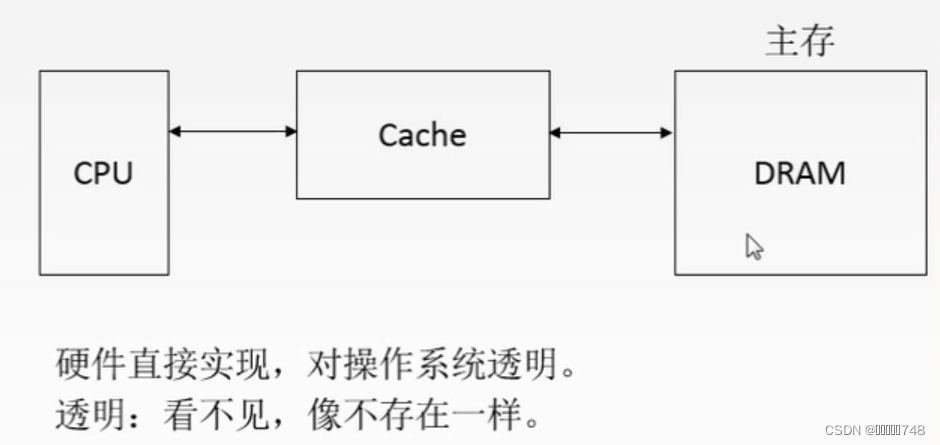

Cache——主存层次

概念

分类

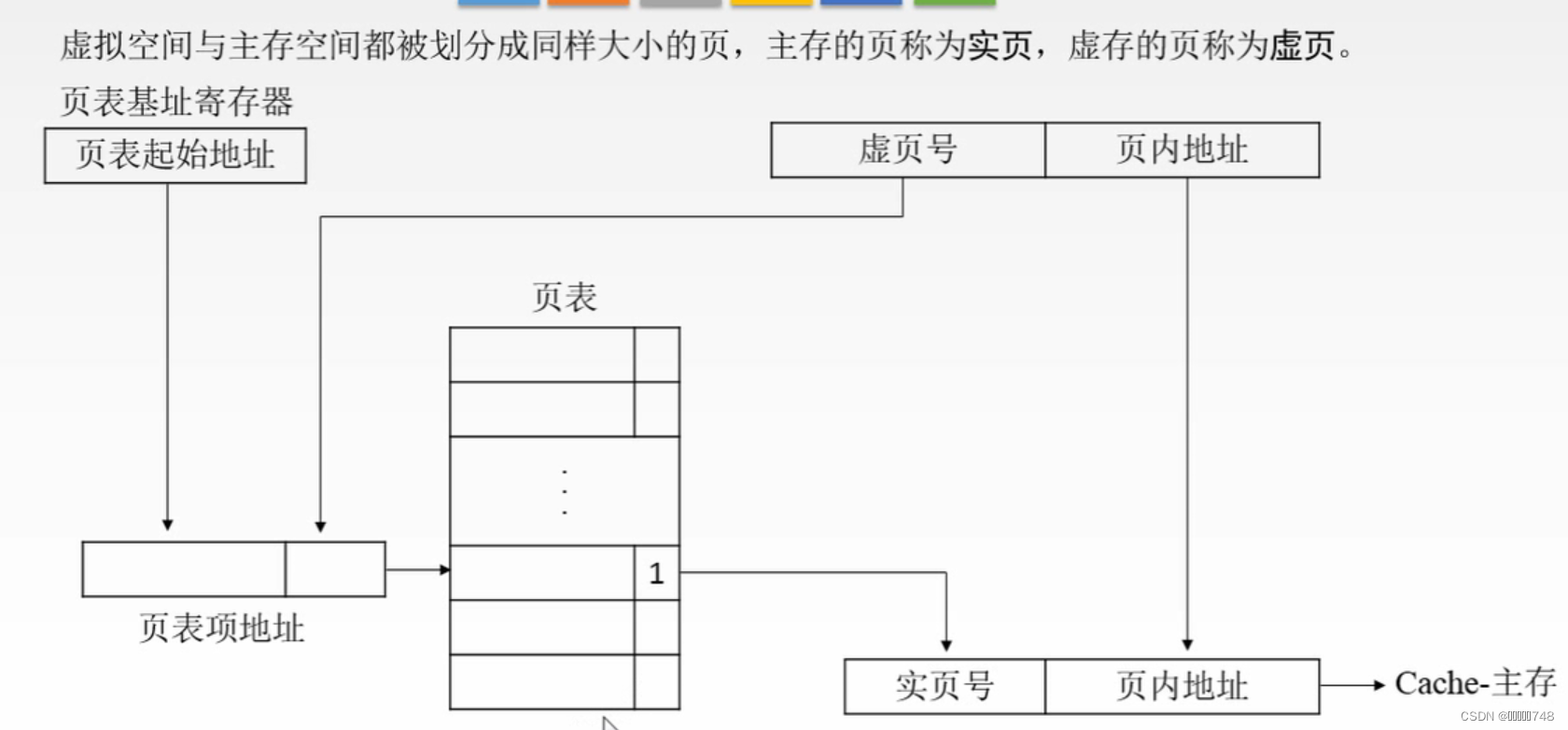

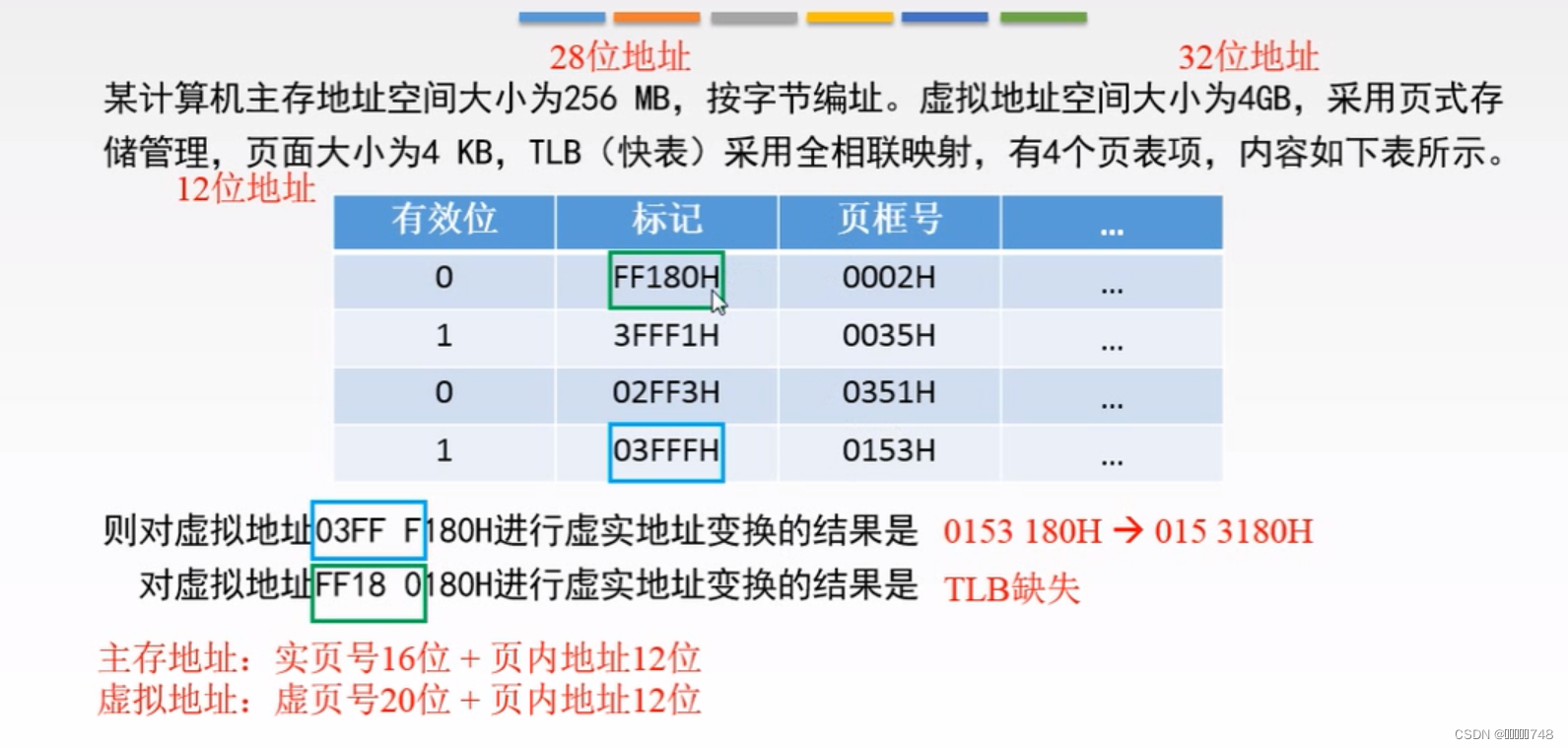

页式虚拟存储器

页表实际上存放在主存当中,页表项地址是一个主存地址,实业号和页内地址拼接成的也是一个主存地址,虚拟地址再主存中是不存在的

页的大小是固定的,主存和虚存都分成大小相同的页

习题

标记指的是虚页号,页框号指的是实页号

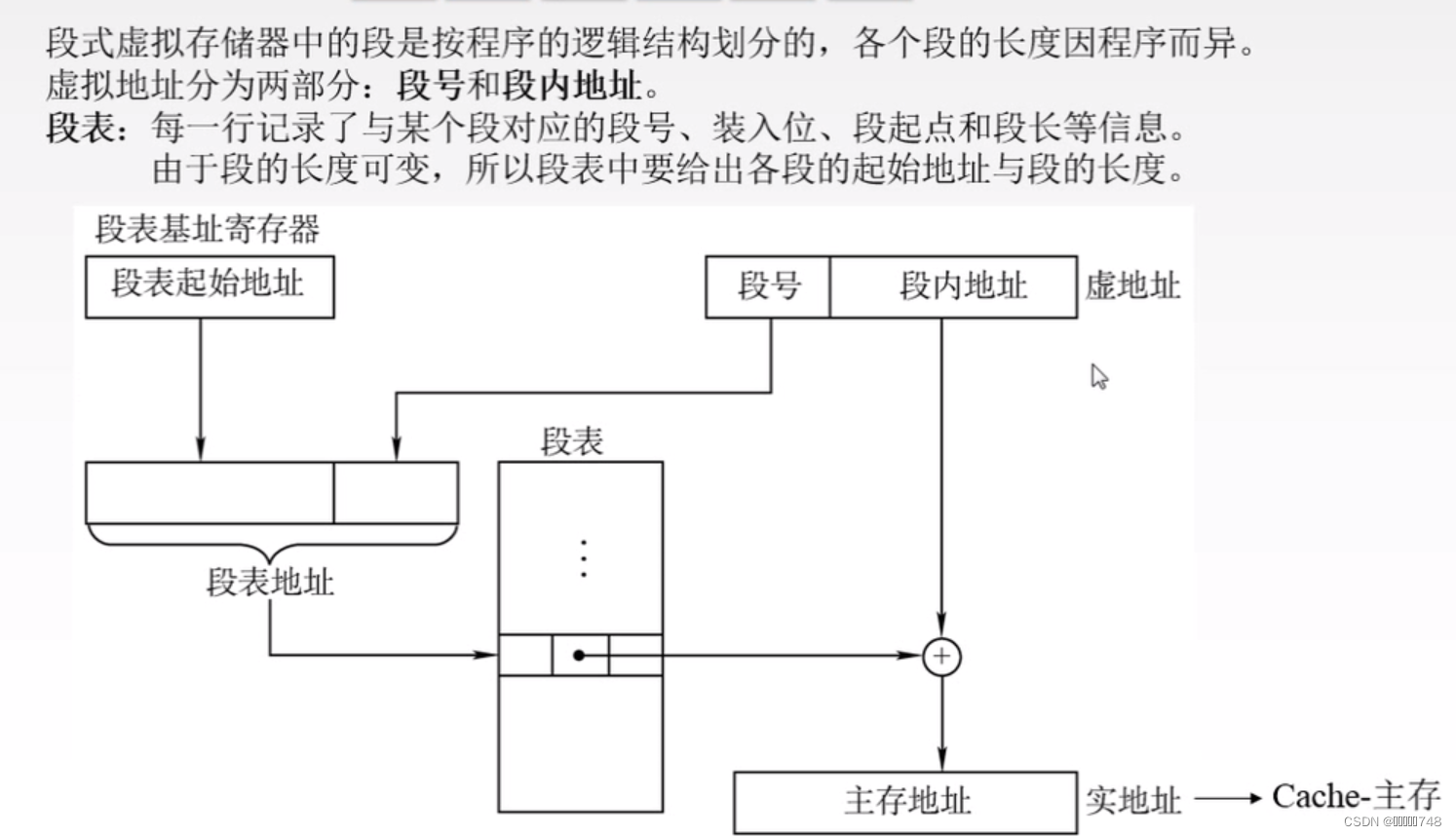

段式虚拟存储器

段大小不固定,主存和虚存不需要提前拆分成大小相等的单位

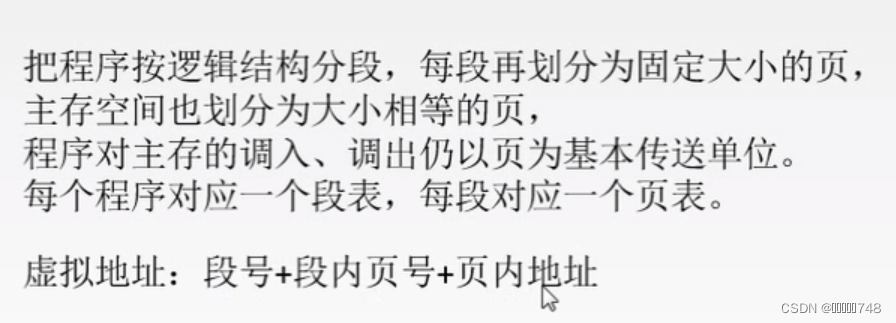

段页式虚拟存储器

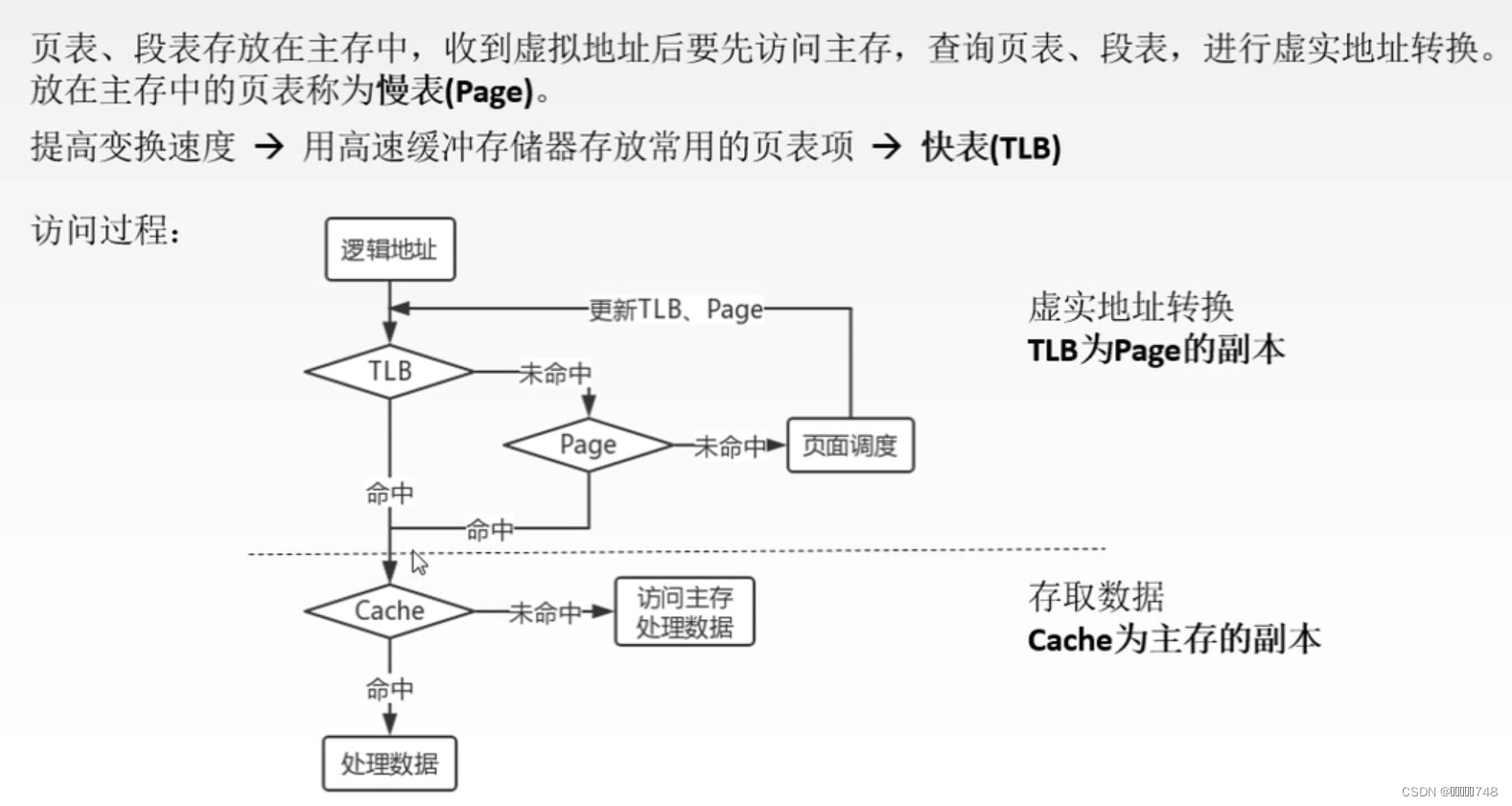

快表TLB

快表是慢表的一个副本,Cache是主存的一个副本

总结

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?