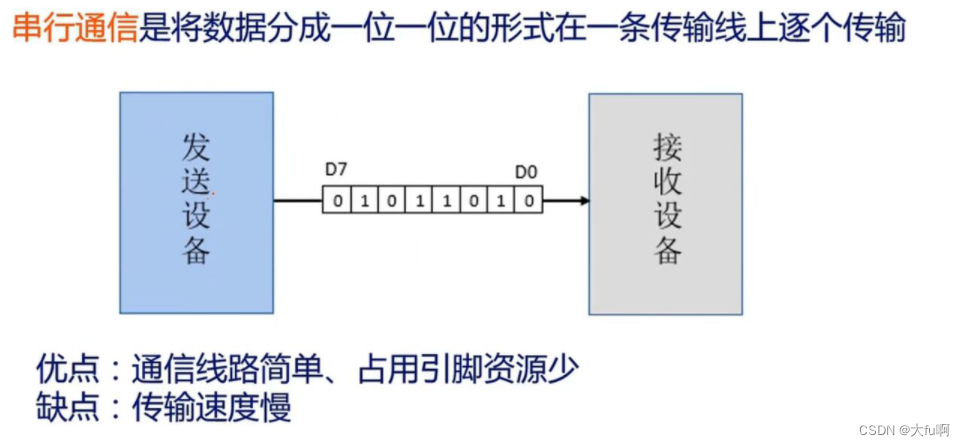

一、串口通信基础知识

1、什么是串口?

串行接口简称串口,也称串行通信接口或串行通讯接口(通常指COM接口),是采用串行通信方式的扩展接口。串行接口 (Serial Interface)是指数据一位一位地顺序传送。其特点是通信线路简单,只要一对传输线就可以实现双向通信(可以直接利用电话线作为传输线),从而大大降低了成本,特别适用于远距离通信,但传送速度较慢。

2、同步通信和异步通信

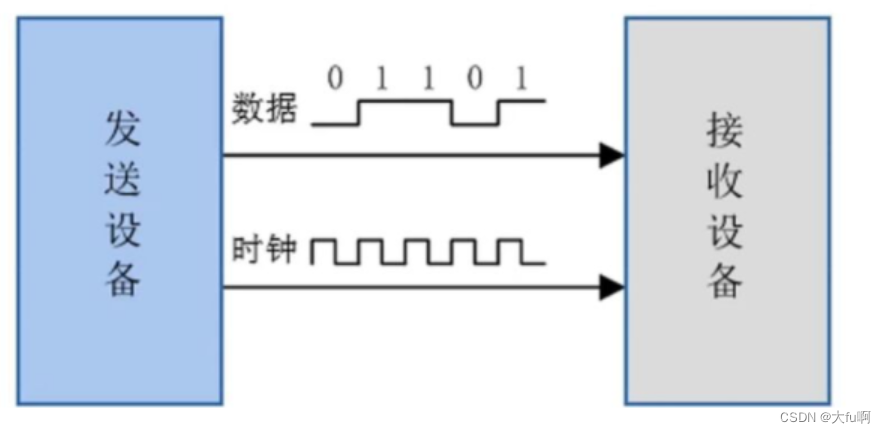

串行通信分为两种方式:同步串行通信和异步串行通信。

同步串行通信需要通信双方在同一时钟的控制下,同步传输数据,比如:SPI,IIC通信接口。图1所示;

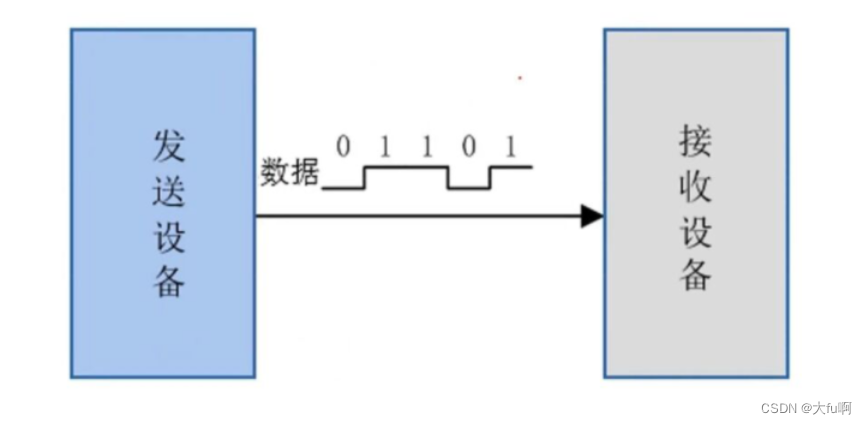

异步串行通信是指通信双方使用各自的时钟控制数据的发送和接收过程,比如:UART(通用异步收发器),图2所示。

图1同步串行通信

图2异步串行通信

3、串行通信的传输方向

根据串行数据的传输方向,我们可以将通信分为单工,半双工,双工。

单工:是指数据传输仅能沿一个方向,不能实现反向传输。

半双工:是指数据传输可以沿两个方向,但需要分时进行传输。

全双工:是指数据可以同时进行双向传输。

下图是单工、半双工以及全双工的示意图

4、常见的串口通信接口

二、UART串口通信

UART基础知识

UART 是一种采用异步串行通信方式的通用异步收发传输器(universal asynchronous receiver-transmitter),它在发送数据时将并行数据转换成串行数据来传输,在接收数据时将接收到的串行数据转换成并行数据。

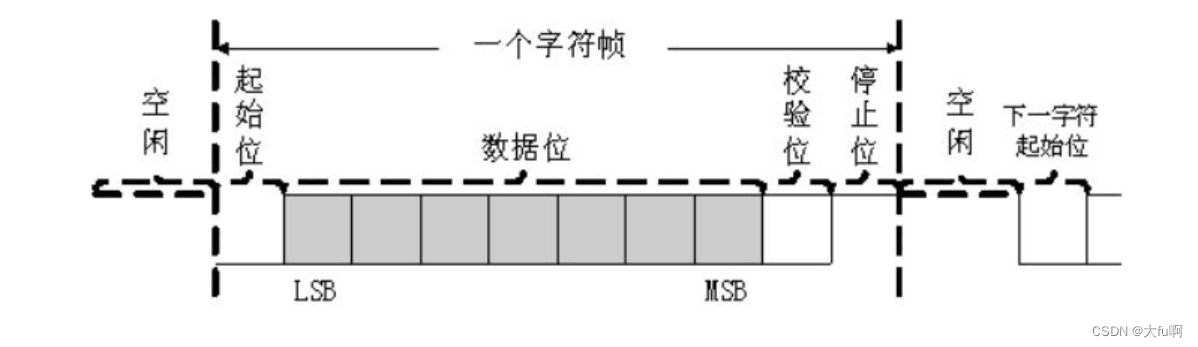

1、协议层:通信协议(包括数据格式,传输速率等)

(1)数据格式

UART 串口通信需要两根信号线来实现,一根用于串口发送,另外一根负责串口接收。UART 在发送或接收过程中的一帧数据由 4 部分组成,起始位、数据位、奇偶校验位和停止位,如图所示。其中,起始位标志着一帧数据的开始,停止位标志着一帧数据的结束,数据位是一帧数据中的有效数据。校验位分为奇校验和偶校验,用于检验数据在传输过程中是否出错。奇校验时,发送方应使数据位中 1 的个数与校验位中 1 的个数之和为奇数;接收方在接收数据时,对 1 的个数进行检查,若不为奇数,则说明数据在传输过程中出了差错。同样,偶校验则检查 1 的个数是否为偶数。

(2)传输速率

波特率:串行通信的数据是按位进行传送的,一般将机器每秒钟传送的二进制数码的位数称为波特率,单位为bps,即位/秒,比如1秒钟传送1位,就是1波特。用于说明数据传送的快慢。UART 通信过程中的数据格式及传输速率是可设置的,为了正确的通信,收发双方应约定并遵循同样的设置。数据位可选择为 5、6、7、8 位,其中 8 位数据位是最常用的,在实际应用中一般都选择 8 位数据位;校验位可选择奇校验、偶校验或者无校验位;停止位可选择 1 位(默认),1.5 或 2 位。串口通信的速率用波特率表示,它表示每秒传输二进制数据的位数,单位是 bps(位/秒),常用的波特率有 9600、19200、38400、57600 以及 115200 等。

2、物理层:接口类型,电平标准等

针对异步串行通信的接口标准有RS232、RS422、RS485等

在设置好数据格式及传输速率之后,UART 负责完成数据的串并转换,而信号的传输则由外部驱动电路实现。电信号的传输过程有着不同的电平标准和接口规范,针对异步串行通信的接口标准有 RS232、RS422、RS485 等,它们定义了接口不同的电气特性,如 RS-232 是单端输入输出,而 RS-422/485 为差分输入输出等。

RS232 接口标准出现较早,可实现全双工工作方式,即数据发送和接收可以同时进行。在传输距离较短时(不超过 15m),RS232 是串行通信最常用的接口标准,RS-232 标准的串口最常见的接口类型为 DB9。

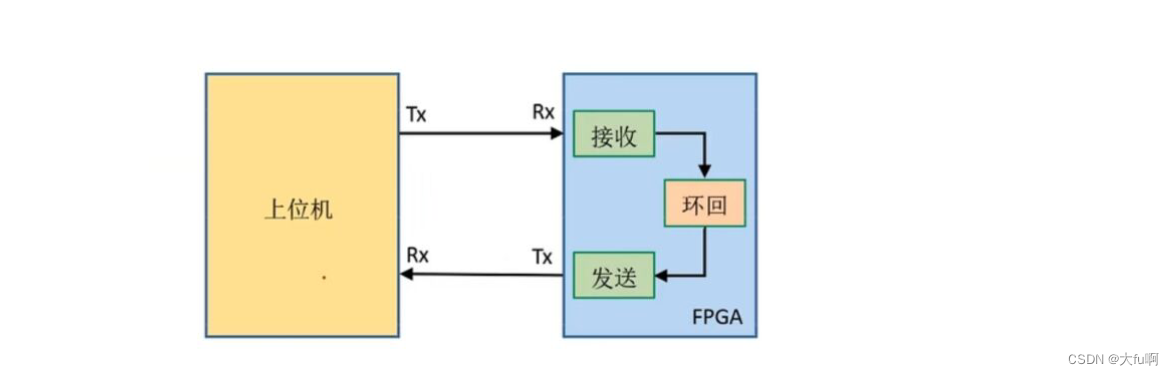

UART串口通信实验

1、程序设计

(1)程序框图

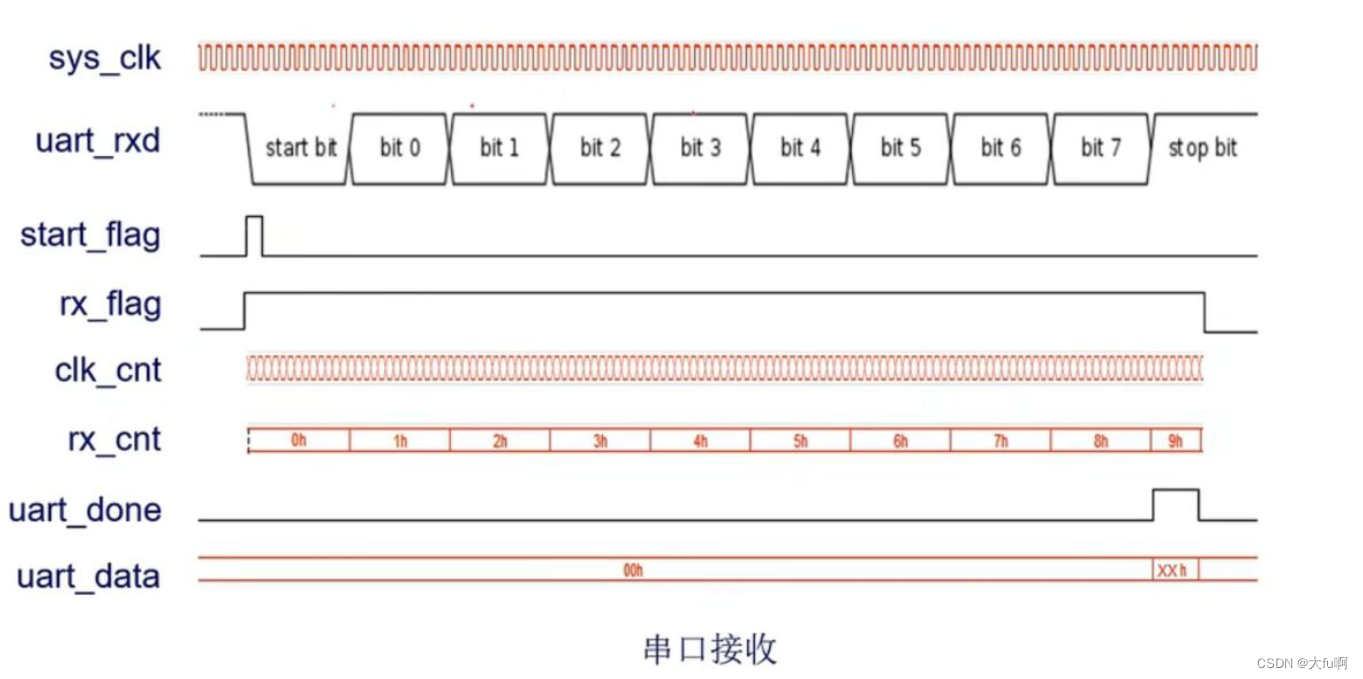

(2)时序框图

(3)接收模块

module uart_recv(

input sys_clk, //系统时钟

input sys_rst_n, //系统复位,低电平有效

input uart_rxd, //UART接收端口

output reg uart_done, //接收一帧数据完成标志

output reg rx_flag, //接收过程标志信号

output reg [3:0] rx_cnt, //接收数据计数器

output reg [7:0] rxdata,

output reg [7:0] uart_data //接收的数据

);

//parameter define

parameter CLK_FREQ = 50000000; //系统时钟频率

parameter UART_BPS = 115200; //串口波特率

localparam BPS_CNT = CLK_FREQ/UART_BPS; //为得到指定波特率,

//需要对系统时钟计数BPS_CNT次

//reg define

reg uart_rxd_d0;

reg uart_rxd_d1;

reg [15:0] clk_cnt; //系统时钟计数器

//wire define

wire start_flag;

//*****************************************************

//** main code

//*****************************************************

//捕获接收端口下降沿(起始位),得到一个时钟周期的脉冲信号

assign start_flag = uart_rxd_d1 & (~uart_rxd_d0);

//对UART接收端口的数据延迟两个时钟周期

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n) begin

uart_rxd_d0 <= 1'b0;

uart_rxd_d1 <= 1'b0;

end

else begin

uart_rxd_d0 <= uart_rxd;

uart_rxd_d1 <= uart_rxd_d0;

end

end

//当脉冲信号start_flag到达时,进入接收过程

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

rx_flag <= 1'b0;

else begin

if(start_flag) //检测到起始位

rx_flag <= 1'b1; //进入接收过程,标志位rx_flag拉高

//计数到停止位中间时,停止接收过程

else if((rx_cnt == 4'd9) && (clk_cnt == BPS_CNT/2))

rx_flag <= 1'b0; //接收过程结束,标志位rx_flag拉低

else

rx_flag <= rx_flag;

end

end

//进入接收过程后,启动系统时钟计数器

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

clk_cnt <= 16'd0;

else if ( rx_flag ) begin //处于接收过程

if (clk_cnt < BPS_CNT - 1)

clk_cnt <= clk_cnt + 1'b1;

else

clk_cnt <= 16'd0; //对系统时钟计数达一个波特率周期后清零

end

else

clk_cnt <= 16'd0; //接收过程结束,计数器清零

end

//进入接收过程后,启动接收数据计数器

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

rx_cnt <= 4'd0;

else if ( rx_flag ) begin //处于接收过程

if (clk_cnt == BPS_CNT - 1) //对系统时钟计数达一个波特率周期

rx_cnt <= rx_cnt + 1'b1; //此时接收数据计数器加1

else

rx_cnt <= rx_cnt;

end

else

rx_cnt <= 4'd0; //接收过程结束,计数器清零

end

//根据接收数据计数器来寄存uart接收端口数据

always @(posedge sys_clk or negedge sys_rst_n) begin

if ( !sys_rst_n)

rxdata <= 8'd0;

else if(rx_flag) //系统处

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1999

1999

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?