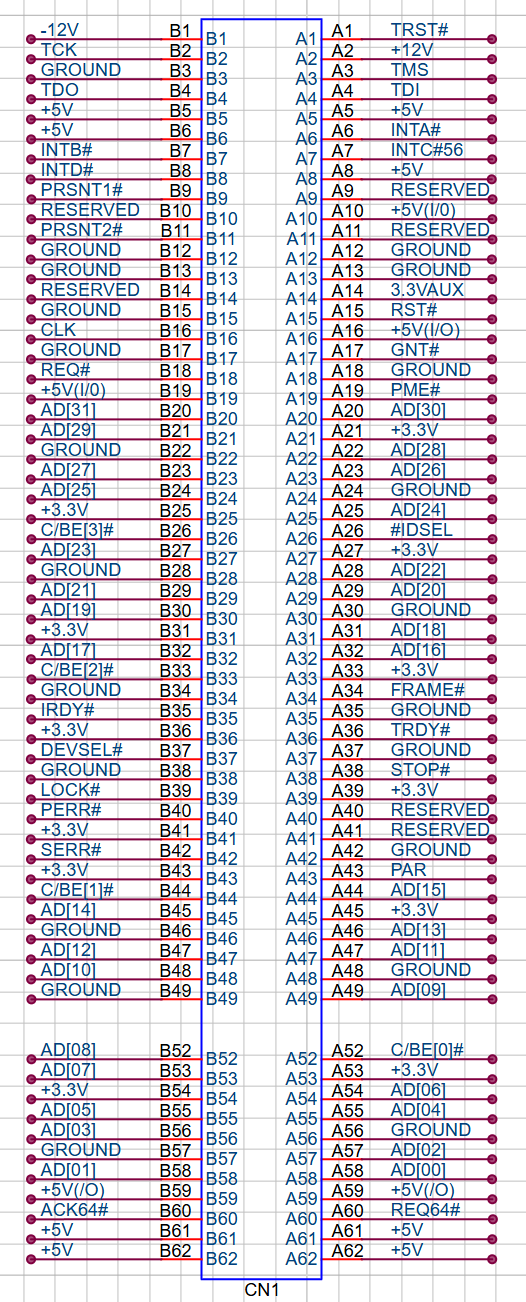

PCI 总线是一条共享总线, 在一条 PCI 总线上可以挂接多个 PCI 设备。 这些 PCI 设备通 过一系列信号与 PCI 总线相连, 这些信号由地址/ 数据信号、 控制信号、 仲裁信号、 中断信号等多种信号组成。

PCI 总线可以使用33 MHz 或者66 MHz 的时钟频率, 而 PCI⁃X 总线可以使用 133 MHz、 266 MHz 或者 533 MHz 的时钟频率。

除了 RST#、 INTA ~ D#、 PME#和 CLKRUN#等信号之外, PCI 设备使用的绝大多数信号 都使用这个 CLK 信号进行同步。 其中 RST#是复位信号, 而 PCI 设备使用 INTA ~ D#信号进 行中断请求。

地址和数据信号

在 PCI 总线中,与地址和数据相关的信号如下

(1)AD[31:0](Address and Data)信号

PCI 总线复用地址与数据信号。PCI 总线事务在启动后的第一个时钟周期传送地址,这个地址是 PCI 总线域的存储器地址或者 I/O 地址;而在下一个时钟周期传送数据。传送地址的时钟周期也被称为地址周期,传送数据的时钟周期也被称为数据周期。PCI 总线支持突发传送,即在一个地址周期之后,可以紧跟多个数据周期(类似于 I2C 的连续读和连续写)。

(2)PAR(Parity)信号

PCI 总线使用奇偶校验机制,保证地址和数据信号在进行数据传递时的正确性。PAR 信号是 AD[31:0] 和 C/BE[3:0] 的奇偶校验信号。在传输地址的时候PAR要在地址传输完毕后一个时钟周期保持稳定。对于数据段,PAR要在IRDY#或者TRDY#有效以后一个时钟周期保持稳定。一旦PAR数据有效,将保持有效到当前数据或地址段传输结束。

(3)C/BE[3:0]#(Bus Commandand Byte Enables)总线信号

PCI 总线复用命令与字节选通引脚。在地址周期中(AD为地址线的时候),C/BE[3:0]# 信号表示 PCI 总线的命令。而在数据周期中(AD为数据线的时候),C/BE[3:0]# 引脚输出字节选通信号,其中 C/BE3、C/BE2、C/BE1、C/BE0 与数据的字节 3、2、1、0 对应,使用这组信号可以对 PCI 设备进行单个字节、字和双字访问。

以下给出常用的总线事务类型

接口控制信号

在 PCI 总线中,接口控制信号的主要作用是保证数据的正常传递,并根据 PCI 主从设备的状态,暂停、终止或者正常完成当前总线事务。其主要信号如下

(1)FRAME# (Cyclone Frame)信号

该信号指示一个 PCI 总线事务的开始与结束。当 PCI 设备获得总线的使用权后,将置该信号有效,即置为低,启动 PCI 总线事务,当结束总线事务时,将置该信号无效,即置为高。PCI 设备(和 HOST 主桥)只有通过仲裁获得当前 PCI 总线的使用权后,才能驱动该信号。

(2)IRDY# (Initiator Ready)信号

该信号由 PCI 主设备(和 HOST 主桥)驱动,该信号有效时表示 PCI 主设备的数据已经准备完毕。如果当前 PCI 总线事务为写事务,表示数据已经在 AD[31:0] 上有效;如果为读事务,表示 PCI 目标(接收)设备已经准备好接收缓冲,目标(发送)设备可以将数据发送到 AD[31:0] 上。

(3)TRDY# (Target Ready)信号

该信号由目标设备驱动,该信号有效时表示目标设备已经将数据准备完毕。如果当前 PCI 总线事务为写事务,表示目标设备已经准备好接收缓冲,可以将 AD[31:0] 上的数据写入目标设备;如果为读事务,表示 PCI 设备需要的数据已经在 AD[31:0] 上有效。

(4)STOP# 信号

该信号有效时表示目标设备请求主设备停止当前 PCI 总线事务。一个 PCI 总线事务除了可以正常结束外,目标设备还可以使用该信号终止当前 PCI 总线事务。

(5)IDSEL(Initialization Device Select) 信号

PCI 总线在进行配置读写总线事务时,使用该信号选择 PCI 目标设备。

IDSEL 信号与 PCI 设备的设备号相关,相当于 PCI 设备配置空间的片选信号。

(6)DEVSEL# (Device Select)信号

该信号有效时表示 PCI 总线的目标设备准备好,该信号与 TRDY# 信号的不同之处在于该信号有效仅表示目标设备已经完成了地址译码。目标设备使用该信号通知 PCI 主设备,其访问对象在当前 PCI 总线上,但是并不表示目标设备可以与主设备进行数据交换。

注意:根据设备的译码速度,PCI设备分为快速、中速和慢速三种,还有一种特殊设备负向译码设备。当三种设备均不能响应PCI总线事务的地址时,负向译码设备将被动接收这个PCI总线事务。若在PCI主设备访问的PCI总线上,没有任何设备可以置DEVSEL#信号有效,主设备将使用Master Abort周期结束当前总线事务。

(7)LOCK#信号

PCI主设备使用该信号,将目标设备的某个存储器或者I/O资源锁定,以禁止其他PCI主设备访问此资源,直到锁定这个资源的主设备将其释放。PCI总线使用LOCK#信号实现LOCK总线事务,只有HOST主桥、PCI桥或其他桥片可以使用LOCK#信号。目前PCI总线使用LOCK#信号仅仅为了防止死锁和向前兼容。

仲裁信号

PCI设备使用该组信号进行总线仲裁,并获得PCI总线的使用权。这组信号由REQ#和GNT#组成。其中PCI主设备的REQ#和GNT#与PCI总线的仲裁器直接相连。在一颗 PCI 总线树中,每一条 PCI 总线上都有一个总线仲裁器。一个处理器体系可以使用 PCI 桥扩展出一条新的 PCI 总线,这条新的 PCI 总线也需要一个总线仲裁器,通常在 PCI 桥中集成了这个总线仲裁器。多数 HOST 主桥也集成了一个 PCI 总线仲裁器。

PCI 主设备使用 PCI 总线进行数据传递时,需要首先置 REQ# 信号有效,向 PCI 总线仲裁器发出总线申请,当 PCI 总线仲裁器允许 PCI 主设备获得 PCI 总线的使用权后,将置 GNT# 信号为有效,并将其发送给指定的 PCI 主设备。而 PCI 主设备在获得总线使用权后,可以置 FRAME# 信号有效,与 PCI 从设备进行数据通信。

(1)REQ#(Request)请求信号

总线占用请求信号。该信号一旦有效即表示驱动它的设备要求使用总线,它是一个点到点的信号线,任何主设备都有其REQ#信号。

(2)GNT#(Grant)信号

总线占用允许信号,用来向申请占用总线的设备表示,其请求已获得批准。这也是一个点到点的信号线,任何主设备都应由自己的GNT#信号。

中断请求信号

PCI 总线提供了 INTA#、INTB#、INTC#、INTD# 四个中断请求信号,PCI 设备借助这些中断请求信号,使用电平触发方式向处理器提交中断请求。当这些中断请求信号为低时,PCI 设备将向处理器提交中断请求;当处理器执行中断服务程序清除 PCI 设备的中断请求后,PCI 设备将该信号置高,结束当前终端请求。

INTx 这组信号为开漏输出,当所有的驱动源不驱动该信号时,该信号由上拉电阻驱动为高。

PCI 总线规定单功能设备只能使用 INTA# 信号,而多功能设备才能使用 INTB#/C#/D# 信号。PCI 设备的这些中断请求信号可以通过某种规则进行线与,之后与中断控制器的中断请求信号线相连。而处理器系统需要预先知道这个规则,以便正确处理来自不同 PCI 设备的中断请求。这个规则也被称为中断路由表。

系统信号

(1)CLK_IN信号

系统时钟信号,对于所有的PCI设备都是输入信号。其频率最高可达33MHz,最低频率一般为0Hz(DC),这一频率也称为PCI的工作频率。对于PCI的其它信号,除了RST#、IRQB#、IRQC#、IRQD#之外,其余信号都在CLK的上升沿有效(或采样)。

(2)RST#_IN信号

复位信号。用来使PCI专用的特性寄存器和定序器相关的信号恢复规定的初始状态。至于PCI定序器之外的设备复位后如何变化,本次不说明。但必要的PCI配置寄存器,其复位状态是明确规定的。每当复位时,PCI的全部输出信号一般都应驱动到第三态。SERR#信号为高阻状态,SBD#和SDONE可驱动到低电平(如果未能提供三态输出)。REQ#和GNT#必须同时驱动到第三态,不能再复位期间为高或为低。为放置AD、C/BE#及PAR在复位期间浮动,可由中心设备将它们驱动到逻辑低,但不能驱动为高电平。RST#和CLK可以不同步,但要保证其撤销的边沿没有反弹。当设备请求引导系统时,将相应复位,复位后相应系统引导。

错误报告信号

(1)PERR#(Parity Error)信号

数据奇偶检验错误报告信号。但该信号不报告特殊周期中的数据奇偶错。一个设备只有在响应设备选择信号(DEVSEL#)和完成数据期之后,才能报告一个PERR#。对于每个数据接收设备,如果发现数据有错误,就应在数据接收的两个时钟周期内将PERR#激活。该信号的持续时间与数据期的多少有关,如果是一个数据期,则最小持续时间为一个时钟周期;若是一连串的数据期并且每个数据期都有错,那么PERR#的持续时间将多于一个时钟周期。由于该信号是持续的三态信号,因此,该信号在释放前必须先驱动为高电平。另外,对于数据奇偶错的报告既不能丢失也不能推迟。

(2)SERR#(System Error)信号

系统错误报告信号。该信号的作用是报告地址奇偶错、特殊命令序列中的奇偶错,以及其它可能引起灾难性后果的系统错误。如果设备不希望产生非屏蔽中断,就应采用其它机制来实现SERR#的报告。由于SERR#是一个漏极开路信号,因此,报告此类错误的设备只需将该信号驱动一个PCI周期即可。SERR#信号的发出和时钟同步,因而满足总线上所有其它信号的建立时间和保持时间的要求。要使该信号复位,需要一个微弱的上拉作用,但这应由系统设计来提供,而不是靠报错的设备或中央资源。一般这种上拉复位需要2~3个时钟周期才能完成。

PRSNT1#与PRSNT2#信号

与热插拔相关,处理器系统根据插入和拔出时插槽中的该信号高低电平来做相应处理。硬件设计上应该使用长短针才能实现热拔插功能,PRSNT1#和PRSNT2#信号使用的金手指长度是其他信号的一半。

高速缓存支持信号

为了使具有可缓存功能的PCI存储器能够和写穿式(Write-through)或者回写式(Write-back)的Cache相配合工作,可缓存的PCI存储器应该能实现两条高速缓存(Cache)支持信号作为输入。如果可缓存的存储器位于PCI总线上。那么,连接回写式Cache和PCI的桥要能够将这对信号作为输出,而连接写穿式Cache的桥只需要实现一个信号。上述的两个信号的定义如下:

(1)SBO#信号

试探返回信号。当该信号有效时,表示命中了一个修改过的行。当该信号无效时,而SDONE信号有效时,表示有一个“干净”的试探效果。

(2)SDONE信号

监听完成信号。用来表示当前监听的状态,该信号无效时,表明监听仍在进行,否则,表明监听已经完成。

64位总线扩展信号

必须注意的是,如果要进行64位扩展,以下信号都要使用。

(1)AD[63..32]信号

扩展的32位地址和数据复用线。再地址期(如果使用了DAC命令且REQ64#有效时)这32条线上含有64位地址的高32位,否则,它们时保留的;在数据期,当REQ64#和ACK64#同时有效时,这32条线上含有高32位数据。

(2)C/BE[7..4]#信号

总线命令和字节使能多路复用信号线。在数据期,若REQ64#和ACK64#同时有效时,该四条线上传输的是表示数据线上哪些字节是有意义的字节使能信号。在地址期里,如果使用了DAC命令且REQ64#信号有效,则表明C/BE[7..4]上传输的是总线命令,否则这些位是保留的且不确定。

(2)REQ64#信号

64位传输请求。该信号是由当前主设备驱动,并表示本设备要求采用64位通路传输数据。它与FRAME#有相同的时序。

(3)ACK64#信号

64位传输认可。表明从设备将用64位传输。此信号由从设备驱动,并且和DEVSEL#具有相同的时序。

(4)PAR64信号

奇偶双字节校验,是AD[64..32]和C/BE[7..4]的检验位。当REQ64#有效且C/BE[3..0]#上是DAC命令时,PAR64将在初始地址期之后的一个时钟周期内有效,并在DAC命令的第二地址期过后的一个时钟处失效。当REQ64#和ACK64#同时有效时,PAR64在各数据期内稳定有效,并且在IRDY#或TRDY#发出后的一个时钟处失效。PAR64信号一旦有效,将保持到数据期完成之后的一个时钟周期处。该信号与AD[63..32]的时序相同,但拖后一个时钟周期,对于主设备是为了地址和写数据而发PAR64,从设备是为了读数据而发PAR64。

3761

3761

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?