边沿检测指的是检测一个信号的上升沿或者下降沿,即产生一个脉冲信号。边沿检测电路根据检测边沿的类型一般分为上升沿检测电路、下降沿检测电路和双沿检测电路。

1.边沿检测简介

在复杂的逻辑设计中,很多情况我们都需要检测信号的跳变。如果一个信号发生跳变,则逻辑给出一个指示,这个指示用来控制其他信号的动作,这种情况就需要有一个边沿检测电路,所以说边沿检测是一种非常典型的电路,其设计思想也是很重要的。

我们根据检测边沿的类型一般可以将边沿检测分为上升沿检测电路、下降沿检测电路和双沿检测电路。

下面我们来介绍下时序中常用的边沿检测电路,我们先来看下上升沿检测电路。

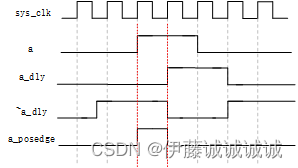

a信号是一个持续2个时钟周期的信号,如果想得到a信号的上升沿也就是a_posedge信号,大家想下,我们应该怎么做呢?a_posedge信号是一个持续1个时钟周期的脉冲信号,那么如果我们把a信号寄存一拍,得到a_dly信号。我们再用a信号和a_dly取反再相与,是不是就可以得到一个持续1个时钟周期的脉冲信号呢,这个a_posedge信号就是a的上升沿指示信号。

module pos_module(

input i_sys_clk ,

input i_a ,

output o_pos

);

(* ASYNC_REG = "TRUE" *)

reg r_dly;

always@(posedge i_sys_clk)

begin

r_dly <= i_signal;

end

assign o_pos = i_a & ~r_dly;

endmoudle看完上升沿检测电路后,接下来我们再来看一下下降沿检测电路。

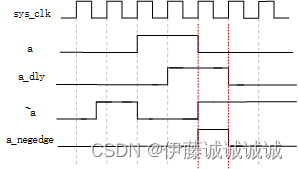

a信号是一个持续2个时钟周期的信号,如果想得到a信号的下降沿也就是a_negedge信号,大家再想下,我们应该怎么做呢?首先a_negedge信号是一个持续1个时钟周期的脉冲信号,那么如果我们把a信号寄存一拍,得到a_dly信号,我们再把a信号取反,用a取反的信号和a_dly相与,是不是就可以得到一个持续1个时钟周期的脉冲信号呢,这个a_negedge信号就是a的下降沿指示信号。

module neg_module(

input i_sys_clk ,

input i_a ,

output o_neg

);

(* ASYNC_REG = "TRUE" *)

reg r_dly;

always@(posedge i_sys_clk)

begin

r_dly <= i_signal;

end

assign o_neg= ~i_a & r_dly;

endmoudle

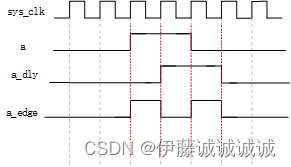

a信号是一个持续2个时钟周期的信号,如果想得到a信号的上升沿和下降沿也就是a_edge信号,大家想下,我们应该怎么做呢?从图上可以看出,取沿的时机正好符合异或门的逻辑。也就是说a_edge信号刚好是a和a_dly信号不同的地方为高电平,那么a和a_dly异或的结果就是a_edge信号,这个信号在a的上升沿持续一个时钟周期,然后在a的下降沿后又持续一个时钟周期。

module edge_module(

input i_sys_clk ,

input i_a ,

output o_edge

);

(* ASYNC_REG = "TRUE" *)

reg r_dly;

always@(posedge i_sys_clk)

begin

r_dly <= i_signal;

end

assign o_edge= i_a ^ r_dly;

endmoudle

文章介绍了边沿检测在逻辑设计中的重要性,详细讲解了如何通过电路设计检测信号的上升沿、下降沿以及双沿。上升沿检测电路通过将原信号延迟一拍并与原信号进行逻辑操作来产生脉冲信号,同样方法适用于下降沿检测。双沿检测则利用异或门来捕捉信号的上升和下降变化。

文章介绍了边沿检测在逻辑设计中的重要性,详细讲解了如何通过电路设计检测信号的上升沿、下降沿以及双沿。上升沿检测电路通过将原信号延迟一拍并与原信号进行逻辑操作来产生脉冲信号,同样方法适用于下降沿检测。双沿检测则利用异或门来捕捉信号的上升和下降变化。

1805

1805

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?