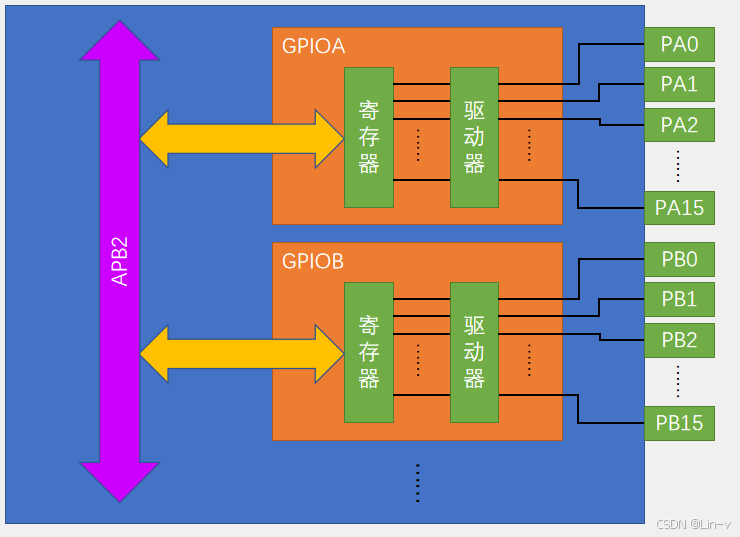

一、GPIO的基本结构

以GPIOA和GPIOB为例,两个GPIO搭载在APB2总线上,内核通过该总线控制GPIO内部对应的寄存器,寄存器可分为输入寄存器和输出寄存器,输入寄存器输入值为1,对应端口输入为高电平,输入为0时为低电平;作为输出寄存器时,输出为1对应端口输出高电平,输出为0对应端口输出低电平,内核通过APB2总线读写寄存器,控制/感知低16位引脚的高低电平。(因为寄存器位为32位,引脚是16位,寄存器的低16位才有对应引脚的端口)

驱动器主要作用为增强信号的驱动能力

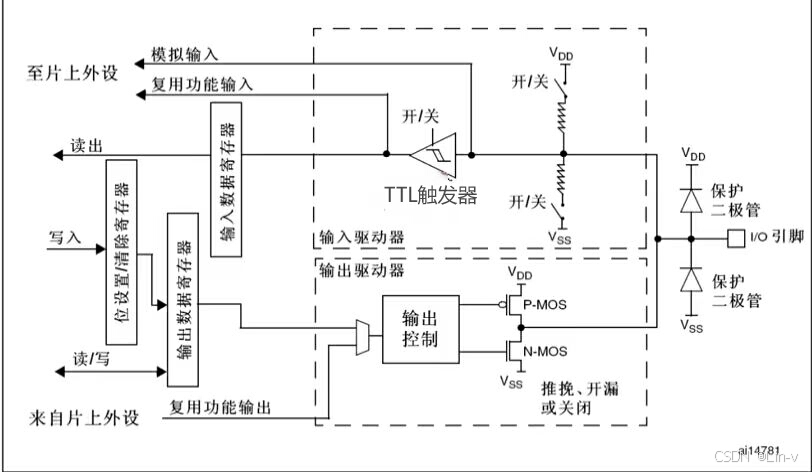

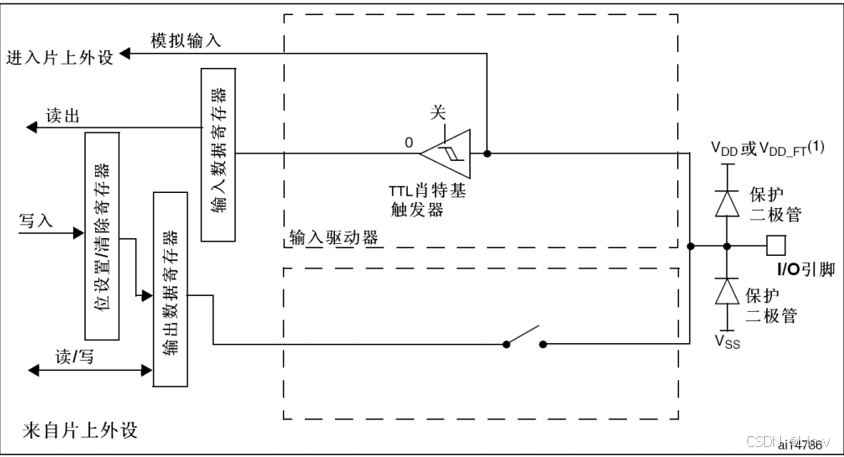

上图为GPIO的基本结构,主要分成输入部分与输出部分,下面对该结构的器件的作用做出说明

输入部分:

保护二极管:I/O的主要承受电压为0-3.3V,当输入电压大于3.3V时VDD处的保护二极管导通,电流从VDD处流出,避免电流进入结构内部;当输入电压为负压小于0V时VSS处保护二极管导通,电流从I/O引脚处流出。

输入驱动部分的两个开关:开关的三种状态对应三种输入模式

VDD的开关闭合——上拉输入模式即高电平输入模式,VSS的开关闭合——下拉输入模式即低电平输入模式,VDD和VSS处的开关都断开——浮空输入模式

TTL触发器,又名施密特触发器,对电压进行整流,保证输出电流为矩形,输入电压大于某一值电压瞬间为高电平,输入电压小于某一值电压瞬间为底电平。

模拟输入需要输入模拟量,所以接施密特触发器后面,复用功能输入需要输入数字量,所以接施密特触发器前面

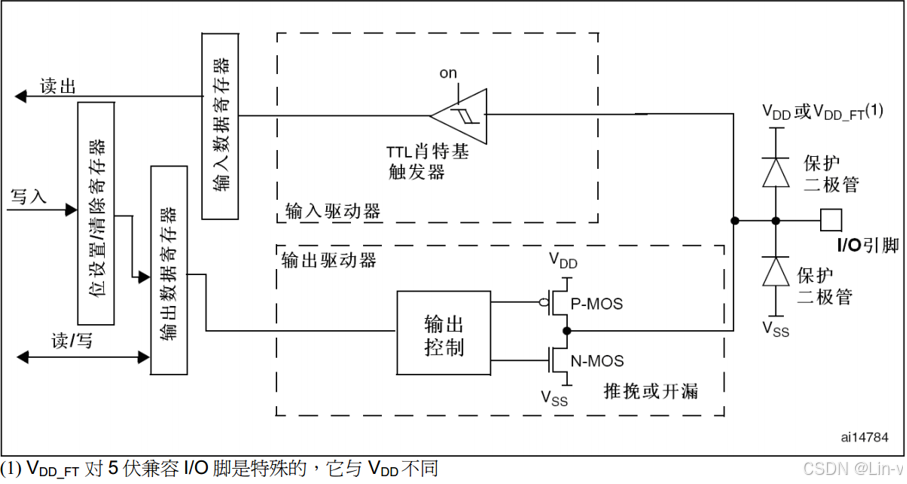

输出部分:

由输出控制寄存器和片上外设两部分组成接到输出控制部分,如果为输出控制寄存器控制则为IO输出由输出控制寄存器的某一位设置对应的端口,对于IO口高低电平的改变分为两种方式,

1、读出输出控制寄存器,该寄存器同时控制16个端口通过按位与或按位或的方式整体改变,再写入输出控制寄存器中,该寄存器通过整体改变位进行端口改变;

2、通过位控制寄存器,该方式对比直接控制输入输出控制寄存器可以只改变单个位而不影响其他位;

输出控制接两个MOS管,分别为P-MOS和N-MOS管两个MOS管不同的状态对于不同的输出模式

1、推挽输出,P-MOS和N-MOS都有效,当设置为高电平时P-MOS闭合接高电平,为低电平时N-MOS闭合接低电平,该模式下无论是高电平还是低电平IO口都有较强的驱动能力

2、开漏输出,P-MOS管无效N-MOS有效,输出控制为1时N-MOS断开,相当于高阻态,输出控制位0时N-MOS连接输出低电平,再此状态下只有低电平有驱动能力而高电平没有驱动能力,该模式可作为通信协议的驱动模式,避免多机串扰。同时可以输出5V信号用于驱动5V设备,外接5V电源,当N-MOS断开时直接输入5V电压,N-MOS连接时直接接VSS

3、关闭,P-MOS和N-MOS均无效,端口电平信号由外部信号控制

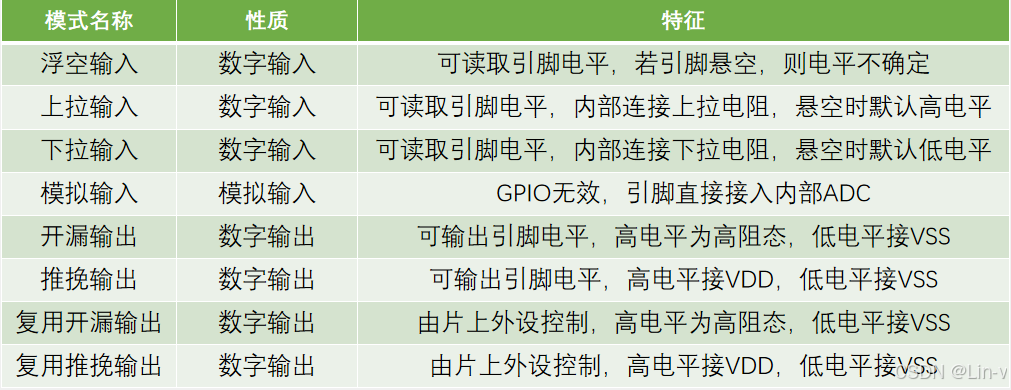

二、GPIO的8种模式以及对应的电路图形

1、浮空/上拉/下拉输入电路

在该模式下输出部分断开,VDD与VSS的开光状态对应三种模式

(1)VDD连接VSS断开:上拉

(2)VDD断开VSS连接:下拉

(3)VDD断开VSS断开:浮空

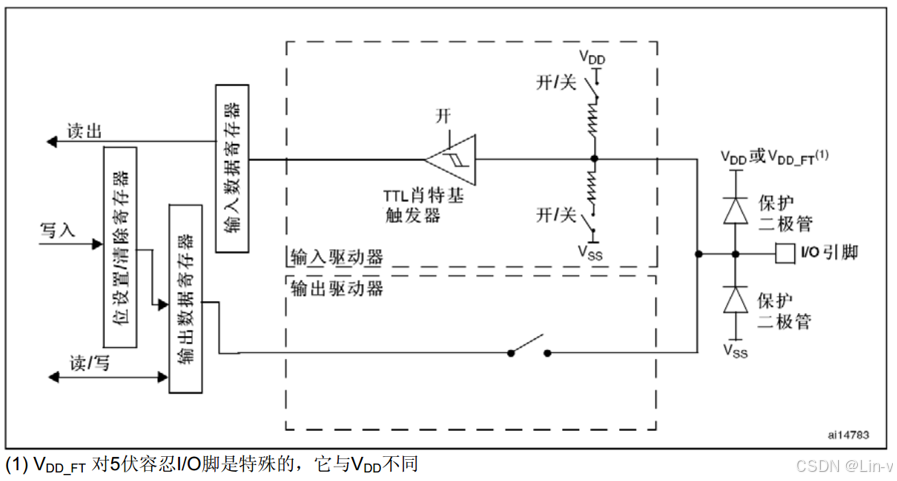

2、模拟输入输入电路

输出部分断开,触发器关闭,模拟输入直接接IO口

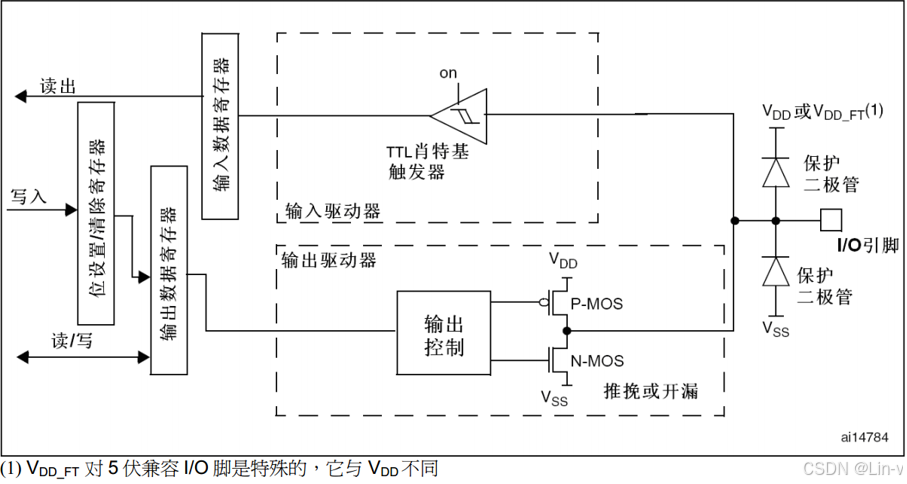

3、开漏/推挽输出电路

由输出控制寄存器控制与VDD和VSS的通断状态有关,前文已经讲过就不再赘述。

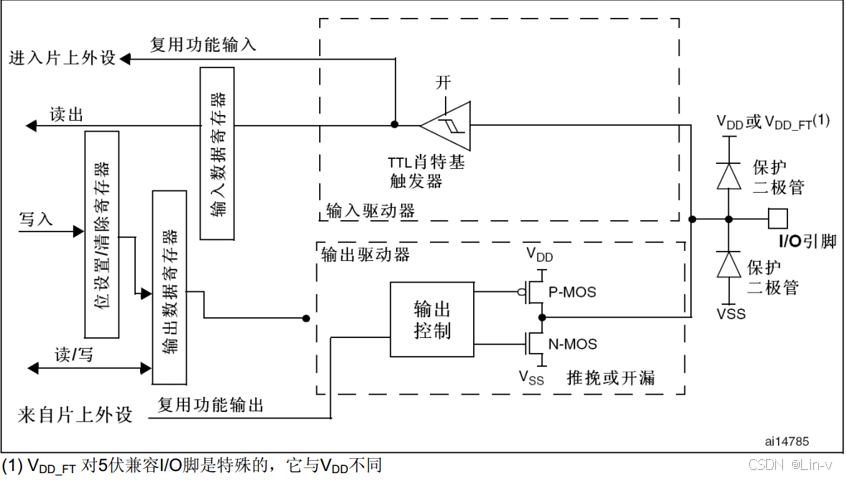

4、复用开漏/推挽输出电路

由片上外设控制与VDD和VSS的通断状态有关,电路与开漏/推挽相同。

11万+

11万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?