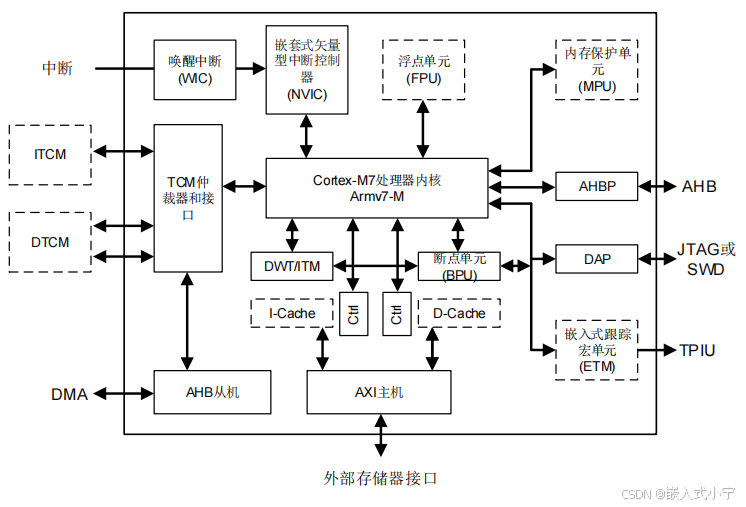

1. Cortex®-M7 处理器结构框图

系统外设:嵌套式向量型中断控制器(NVIC); 闪存地址重载及断点单元(FPB); 数据观测点及跟踪单元(DWT); 指令跟踪宏单元(ITM); JTAG或SWD调试接口 跟踪端口接口单元(TPIU);内存保护单元(MPU);双精度浮点运算单元(FPU); 加载存储单元(LSU); 数据处理单元(DPU); 预取单元(PFU);

系统外设:嵌套式向量型中断控制器(NVIC); 闪存地址重载及断点单元(FPB); 数据观测点及跟踪单元(DWT); 指令跟踪宏单元(ITM); JTAG或SWD调试接口 跟踪端口接口单元(TPIU);内存保护单元(MPU);双精度浮点运算单元(FPU); 加载存储单元(LSU); 数据处理单元(DPU); 预取单元(PFU);

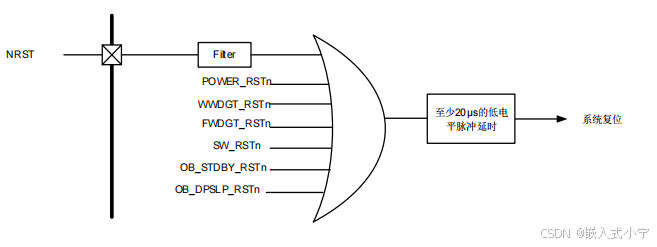

2. 系统复位电路

当发生以下任一事件时,产生一个系统复位:

电源复位(

POWER_RSTn

); 外部引脚复位(NRST

); 窗口看门狗计数终止(WWDGT_RSTn

); 独立看门狗计数终止(FWDGT_RSTn

); Cortex®

-M7

的中断应用和复位控制寄存器中的

SYSRESETREQ

位置‘

1

’(

SW_RSTn

); 用户选择字节寄存器nRST_STDBY

位设置为

0

,并且进入待机模式时将产生复位 (OB_STDBY_RSTn

); 用户选择字节寄存器nRST_DPSLP

设置为

0

,并且进入深度睡眠模式时将产生复位 (OB_DPSLP_RSTn

);

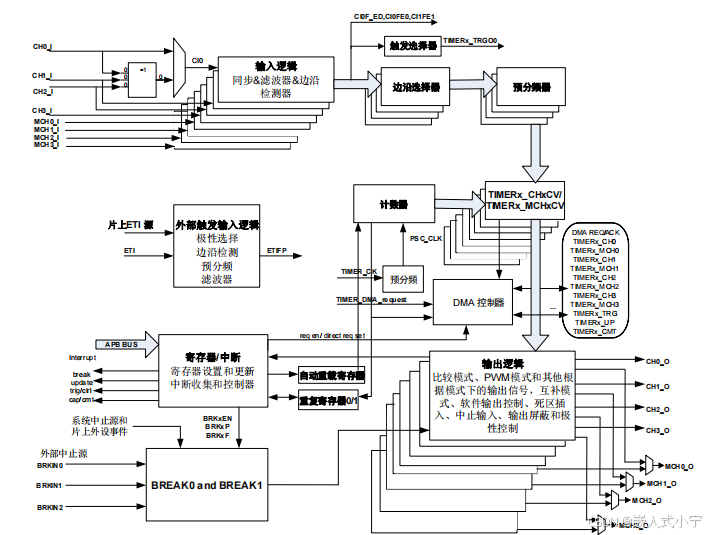

3. 高级定时器结构框图

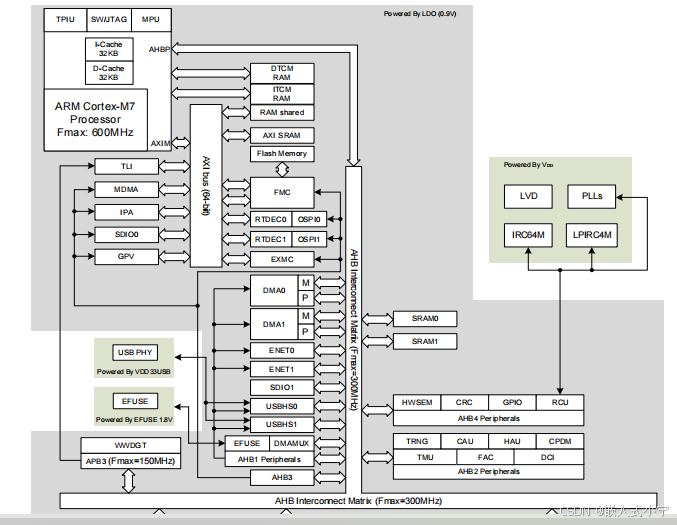

4. 系统架构示意图

398

398

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?