数字逻辑

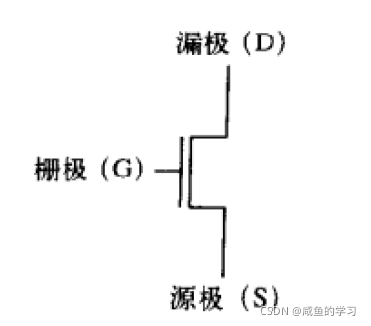

一、MOS晶体管

-

三个引脚(电极),分别被称作“栅级”、“源级”,“漏极”。

-

标识方法

-

横线代表正极

-

下三角代表接地

-

-

n-MOS晶体管

-

如果在栅极接入2.9V电压,则在源极和漏极之间会产生一条通路,这时候n-MOS晶体管就等于是一根连通线(“闭路”)。如果栅极电压是0V,则源极和漏极之间断开,此时称为“开路”

-

-

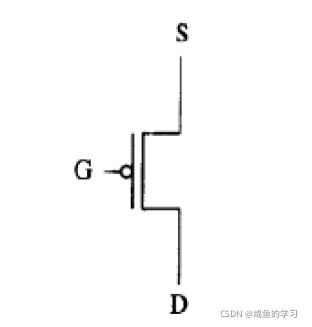

p-MOS晶体管

-

与n-MOS晶体管工作方式恰恰相反

-

-

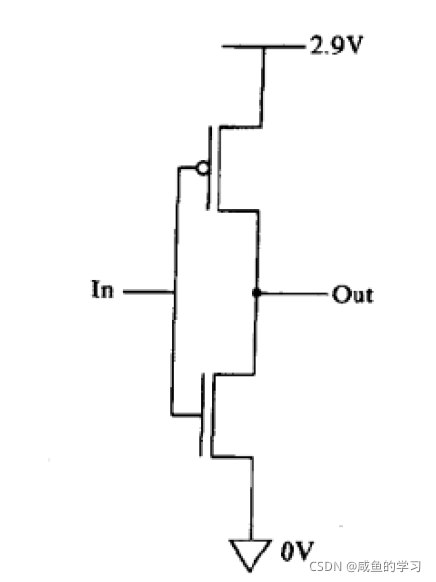

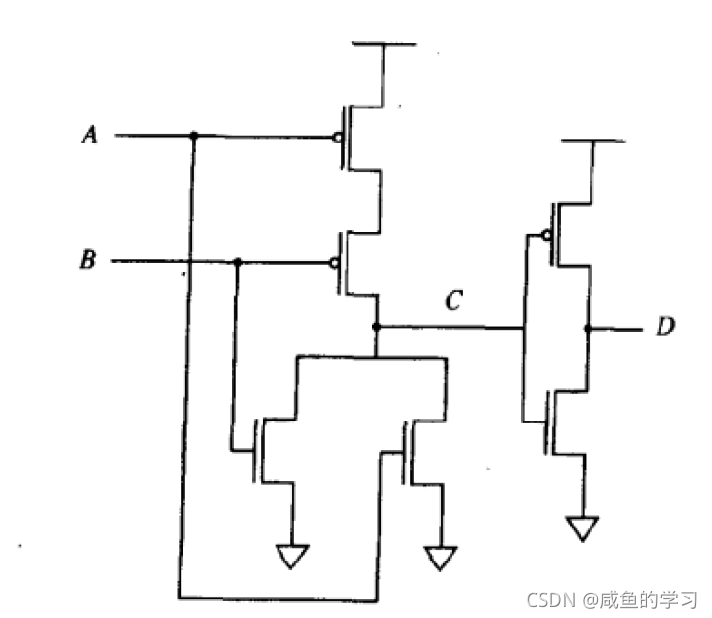

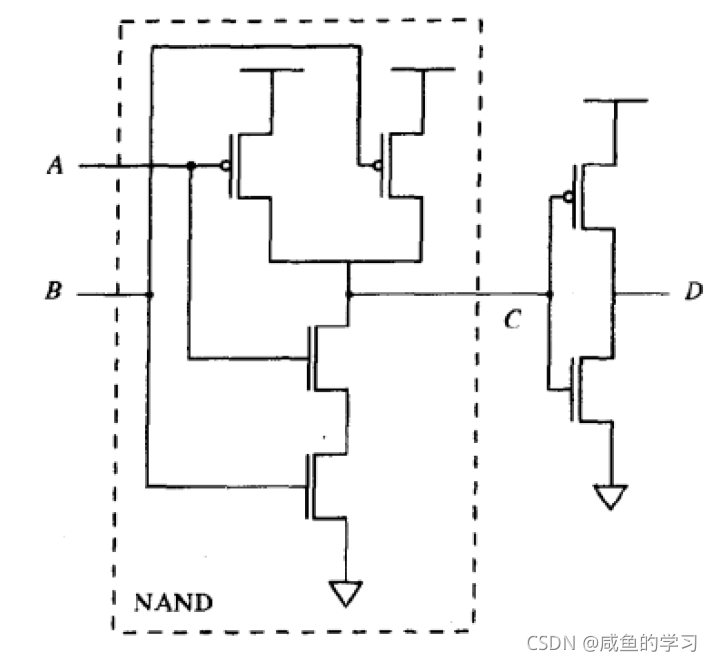

CMOS电路

-

电路中同时包含p-MOS管和n-MOS管

-

二、逻辑门

-

非门

-

或门、或非门

-

与门、与非门

-

摩根定律

~(~A AND ~B) = A OR B

-

多输入门

三、组合逻辑

-

译码器

-

特点:在所有输出中有且仅有一个为1,其余皆为0.每个输出端口对应了一种输入模式,因而该结构可以用于检测、匹配不同的输入模式。

-

主要用于解释一个二进制数(LC-3中,每条指令的操作码为一个4-bit值,通过4-16译码器可识别指令)

-

-

多路复用器(数据选择器)

-

全加器

| A | B | C0 | C | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

-

可编程逻辑阵列

-

通过PLA可实现任何形式的逻辑

-

-

逻辑完备性

-

可以实现任何逻辑函数

-

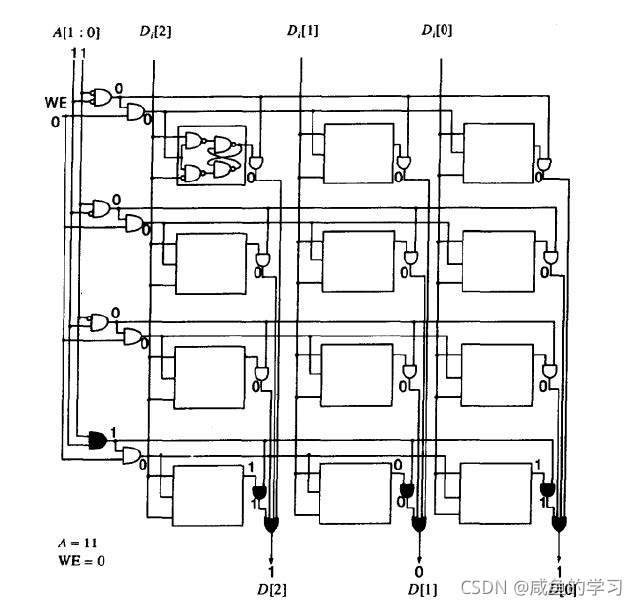

四、存储单元

-

R-S锁存器

-

门控D锁存器

-

寄存器

五、内存的概念

== 内存 ==是由一定数目的“位置”组成的,其中每个“位置”可以被单独识别并独立存放一个数据。通常,我们称位置识别符为“地址”,又称存储在各个位置中的bit数目为“寻址能力”。

-

寻址空间

-

内存中可独立识别的位置总数

-

-

寻址能力

-

每个内存位置中包含的bit数目

-

-

例子:2^2 * 3内存

-

2^2代表内存的地址空间大小为4

-

3代表寻址能力为3-bit宽度

-

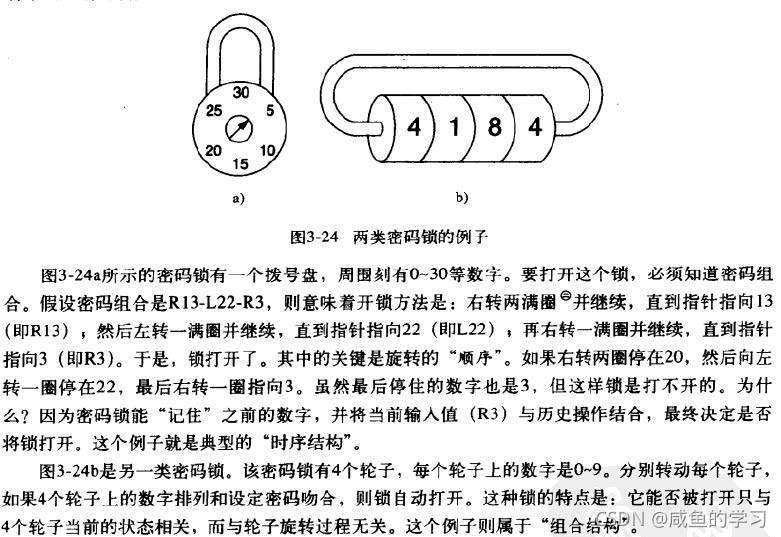

六、时序电路(组合逻辑电路 + 存储单元)

-

组合密码锁

-

状态的概念

-

系统的状态是系统中所有组成要素在拍照时刻的一个“快照”

-

-

有限状态机

-

组成部分

-

状态(有限数目)

-

外部输入(有限数目)

-

对外输出(有限数目)

-

任意状态间迁移(显式注名)

-

对外输出操作(显示注明)

-

-

状态图(状态节点和节点间的连接线组成)

-

时钟

-

时钟是0和1交替变换的信号

-

状态转移通常通过时钟来触发

-

-

-

有限状态机的实现(同数电)

-

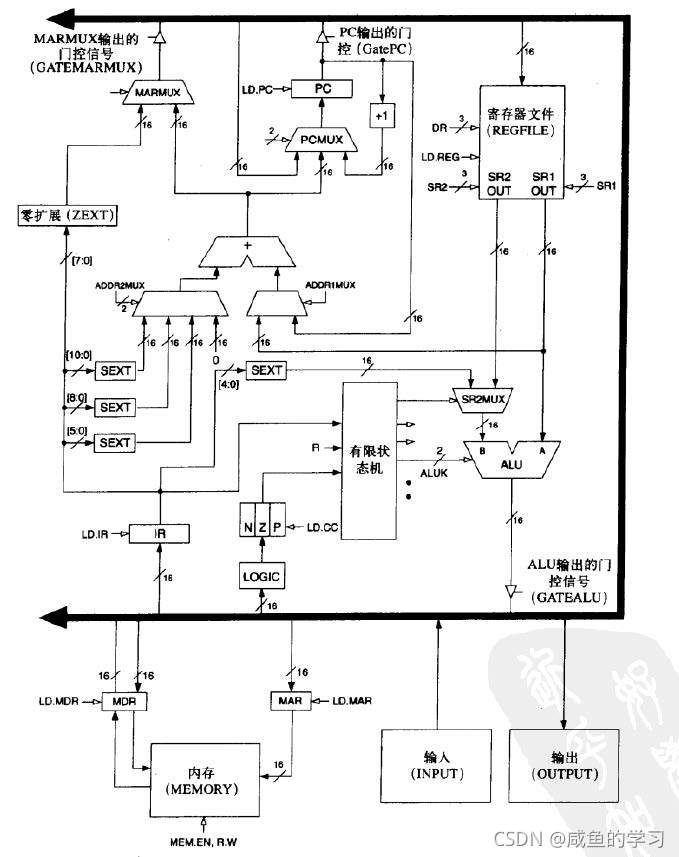

LC-3计算机的数据通路

-

353

353

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?