在Verilog中,casez语句用于进行模糊比较,其中z表示高阻状态。

casez允许您在输入表达式中的某些位上忽略匹配,并匹配包含x或z的情况。

这种形式的case语句对于处理不完全匹配的情况非常有用。

casez的匹配规则:

0和1位:精确匹配,输入表达式的对应位必须与case项完全匹配。

x和z位:模糊匹配,输入表达式的对应位可以是0、1、x、z中的任何一种,都会被认为是匹配的。

?位:通配匹配,输入表达式的对应位可以是0、1、x、z中的任何一种,都会被认为是匹配的.

reg [3:0] data;

reg [1:0] out;

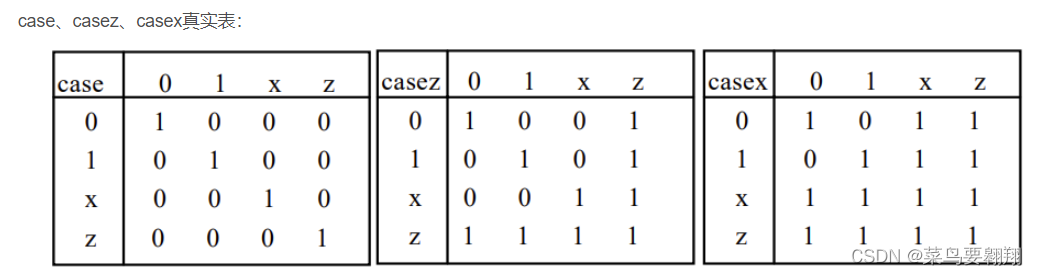

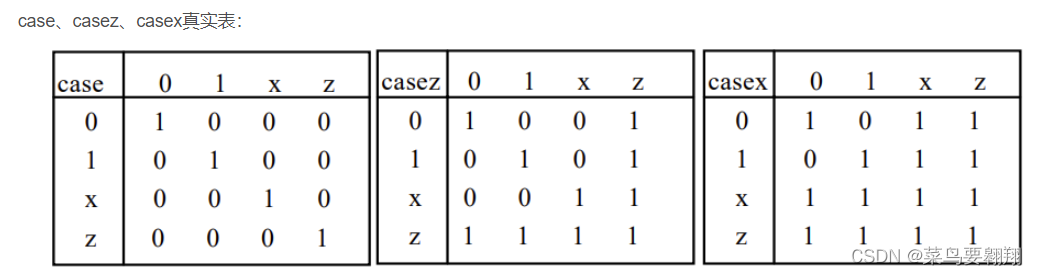

在case语句中 0一定要匹配0,也就是0=0;

在case语句中 1一定要匹配1,也就是1=1;

在case语句中 x一定要匹配x,也就是x=x;

在case语句中 z一定要匹配z,也就是z=z;

在casez中,表示不关心z,也就是z可以等于0,1,x,z,也就是

z = 0; z = 1; z = x z =z;这都可以,就表示模糊匹配。

?位:通配匹配,输入表达式的对应位可以是0、1、x、z中的任何一种,都会被认为是匹配的。

casez(data)

4'b1??0: out = 2'b00; // data= 1110,1100,1010,10000 都可以

4'b10??: out = 2'b01;

4'b01??: out = 2'b10;

4'b01xx: out = 2'b11;//必须data=01xx时候out=2’b11,完全匹配,xx不能是任意值

4‘bz011: out = 2'b10;//z可以为1或者0,或者是x或者是z都可以

default: out = 2'b11;

endcase

casex进一步放开,除了不关心z外,还不关心x也就是如下:x表示不定态

在casex语句中,

z = 0; x=0;

z = 1; x=1;

z = x; x=x;

z = z; x=z;

casex(data)

4'b1??0: out = 2'b00; // data= 1110,1100,1010,10000 都可以

4'b10??: out = 2'b01;

4'b01??: out = 2'b10;

4'b01xx: out = 2'b11;//xx可以是任意值

4‘bz011: out = 2'b10;//z可以为1或者0,或者是x或者是z都可以

default: out = 2'b11;

endcase

5441

5441

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?