什么是FPGA?

一种可通过编程来修改其逻辑功能的数字集成电路。

基础知识:

逻辑0:表示低电平,对应电路中为GND。

逻辑1:表示高电平,对应电路中为VCC。

逻辑X:表示未知,有可能为高电平,也有可能为低电平。

逻辑Z:表示高阻态,外部没有激励信号,是一个悬空状态。

数字进制格式

Verilog数字进制格式包括二进制、八进制、十进制和十六进制,一般常用二进制,十进制和十六进制。

二进制表示:4'b0101表示4为二进制数字

十进制表示:4'd2表示4为十进制数字2(二进制0010)

十六进制表示:4'ha表示4位十六进制数字a(二进制1010)

若没有指定位宽和进制,则默认为32位宽和十进制。

标识符

用于定义模块名、端口名和信号名等。可以是任意一组字母、数字、$和下划线(_)的组合,但是标识符的第一个字符必须是字母或者下划线,并且区分大小写。

推荐的写法:

使用有意义的有效的名字 sum、cpu_add等;

用下划线区分词 cpu_addr等;

采用一些前缀和后缀,比如时钟信号使用clk前缀:clk_50,clk_cpu。

数据类型

寄存器数据类型、线网数据类型、参数数据类型。

前两种数据类型会在数字电路中起作用。

寄存器类型

寄存器表示一个抽象的存储单元,通过赋值语句来改变寄存器的值。寄存器数据类型的关键字是reg,reg类型数据的初始值为不定值x。在定义数据是不能赋值,需要其他语句来赋值。

// reg define

reg[31:0] delay_cnt; //延时计数

reg key_reg;reg类型的数据只能在always语句和initial语句中被赋值。

- 如果该语句描述的是时序逻辑,即always语句带有时钟信号,则该寄存器变量对应为触发器。

- 如果该语句描述的是组合逻辑,即always语句不带有时钟信号,则该寄存器变量对应为硬件连线。

线网数据类型

表示结构实体(例如门)之间的物理连线。线网的变量不能存储值,他的值是由驱动它的元件所决定的。

线网数据类型包括wire型和tri型,最常用的是wire类型。

参数类型

参数实际就是一个常亮,在Verilog中使用parameter定义常亮。可以一次性定义多个参数,参数之间需要使用逗号隔开。

parameter H_SYNC = 11'd41;

parameter H_BACK = 11'd2;参数型数据常用于定义状态机的状态、数据位宽和延迟大小等。采用标识符来代表一个常亮可以提高程序的可读性和可维护性。

运算符

算术运算符(+-*/%)

关系运算符(<,>,>=,<=,==,!=)

逻辑运算符(!,&&,||)

条件运算符(?:)

a?b:c(如果a为真就选b,否则就选c)

位运算符

~ 取反

& 与

| 或

^ 异或

移位运算符

a<<b:a左移b位,a>>b:a右移b位

4'b1001<<2 = 6'b100100;

4'b1001>>2 = 4'b0010;

左移时,位宽增加;右移时,位宽不变

拼接运算符({})

{a,b}

c={a[7:0],b[4,0] \\a8位,b是5位,则c为13位。

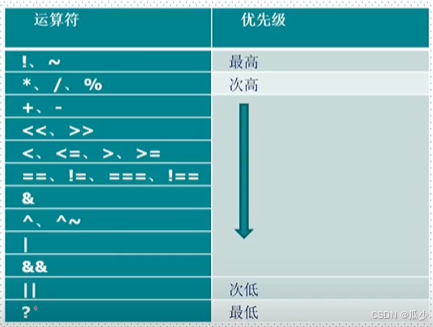

运算符优先级:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?