目录

Sequence

一、基本操作符号

1. 重复操作符

- ##用来表示周期延迟符号,例如##n表示在个时钟周期后,##0表示

在当前周期,即交叠周期。

sequence a b

@(posedge clk) a ##1 b;

endsequence

- ##[min:max]表示在一个范围内的时钟周期延迟。min、max必须是非负数,序列会在从min到max时间窗口中最早的时间来匹配。

sequence a b

@(posedge clk) a [1:5] b;

endsequence

- $用来表示无穷大的周期(在仿真结束前),但是一般我们不建议这么做,因为它会增大仿真评估序列的负担。

sequence a_b

@(posedge clk) a ##[1:$] b;

endsequence

- 事件也可以通过[*n]操作符来表示重复。n必须为非负数,其不能为$。

sequence a_b

@(posedeg clk) a ##1 b[*2];

endsequence

// b[*2] means 'b' must be ture for 2 consecutive clocks

5.类似地, 也可以使用[*m:n]来表示一定范围内的重复事件。

sequence a_b

@(posedge ck) a ##1 b[*2:5];

endsequence

//b[*2:5] meanes 'b' must be ture for

//minimus 2 consecutive cycles and

//maximum 5 consective cycles

- [==m]用来表示一个事件的连续性,需要重复发生m次,但是并不需要在连续周期内发生

- b[=3] 表示b必须在3个周期内为1,但是并不需要是在连续的3个周期内。

sequence a_b

@(posedge clk) a ##1 b[=3];

endsequence

- 例如,执行了一次burst read操作,期望读的数据和ack信号在接下来的4个周期内返回(一共返回4次),但是又不需要在连续的4个周期,即可以使用[=4]来表示

- 类似地,[=m:n] 用来表示从最小m到最大n的重复发生的非连续周期次数。

- a[*0]用来表示没有在任何正数时钟周期内有效

- 例如a[*0:3] ##1 b ##1 c 与下列哪些情形匹配呢?

- (b ##1 c)

- (a ##1 b ##1 c)

- (a ##1 a ##1 b ##1 c)

- (a ##1 a ##1 a ##1 b ##1 c)

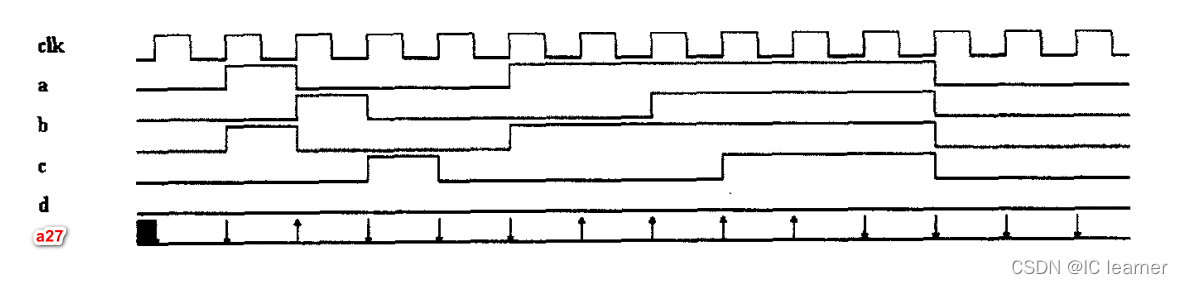

2. and操作符号

- and 用来表示两个序列(sequence)需要保持匹配

- 用法:

SEQ1 and SEQ2 - 下列情形将满足此操作符

- 在从同一个起始点开始后,seq1和seq2均满足

- 满足的时刻发生在两个序列都满足的周期,即稍晚序列的满足时刻。

- 两个序列的满足时间可以不同,即时序终点可以不一样。

示例

sequence s27a;

@(posedge clk) a ##[1:2] b;

endsequence

sequence s27b;

@(posedge clk) c ##[2:3] d;

endsequence

property p27;

@(posedge clk) s27a and s27;

endproperty

a27:assert property(p27);

波形如下

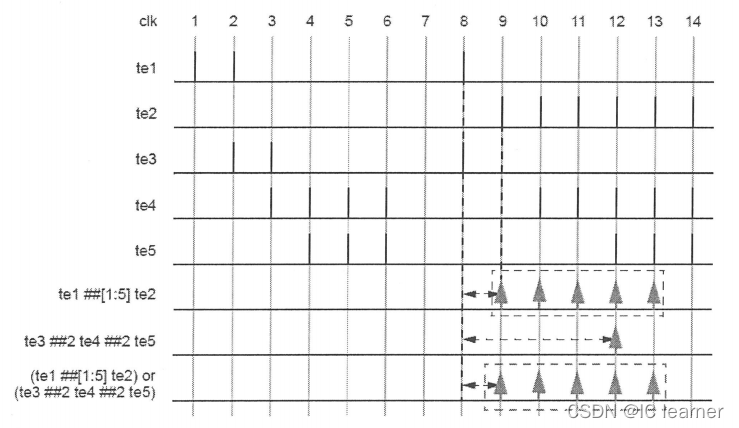

3. or操作符

- OR用来表示两个序列至少需要有一个满足。

- 用法:SEQ1 or SEQ2

- 下列情形将满足此操作符:

- seq1和seq2都从同一个时刻被触发。

- 最终满足seq1或者满足seq2.

- 每一个序列的结束时间可以不同,结束时间以序列满足的最后一个序列时间为准。

示例

(te1 ##[1:5] te2)or(te3 ##2 te4 ##2 te5)

波形

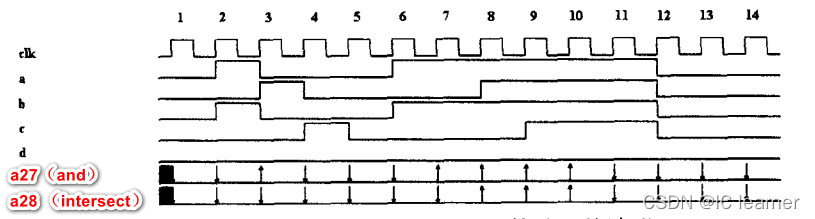

4. intersect 操作符号

- intersect操作符合and操作符类似,只是需要两边的序列时序在同一时钟周期内匹配,即时序1和时序2的起点和终点必须重合。

示例

sequence s28a;

@(posedge clk) a ##[1:2] b;

endsequence

sequence s28b;

@(posedge clk) c ##[2:3] d;

endsequence

property p28;

@(posedge clk) s28a intersect s28b;

endproperty

a28:assert property(p28);

和and操作符对比波形如下

5. throughout 操作符

- 可以用来检查一个信号或者一个表达式在贯穿(throughout)一个序列

时是否满足要求。 - 用法:Sig1/Exp1 throughout Seq

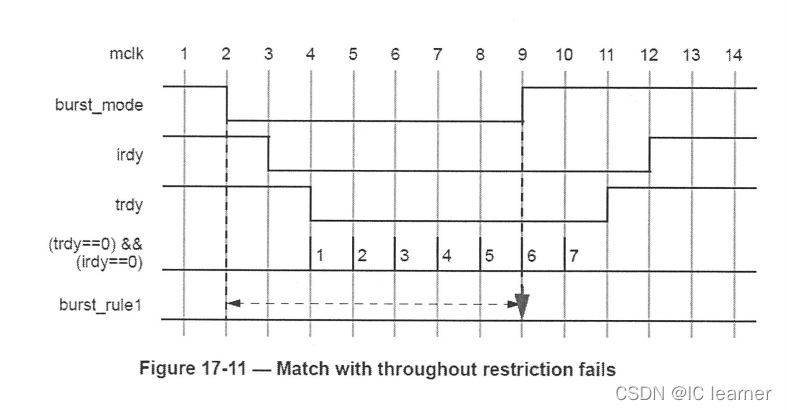

- 例如,在burst?模式信号拉低以后的2个周期时,irdy/trdy也应该在连续7个周期内保持为低,同时bust模式信号也应该在这一连续周期内保持为低。

sequence burst rulel;

@(posedge mclk) $fell(burst_mode) ##0

(!burst mode) throughout (##2 ((trdy==0)&&(irdy==0))[*7]);

endsequence

波形

6. within 操作符

- 可以用来检查一个序列与另外一个序列在部分周期长度上的重叠。

- 用法:SEQ1 within SEQ2

- 如果当seq1满足在seq2的一部分连续时钟周期内成立,seq1 within seq.2成立。

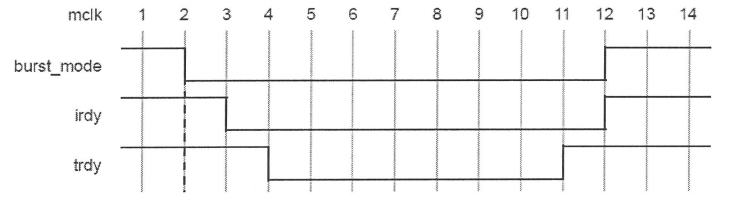

- 例如,trdy需要在Eirday下拉的1个周期后保持7个周期为低,同时irday也将保持8个周期为低,以下序列会在第11个时钟周期满足。

!trdy [*7] within ((sfell irdy) ##1 !irdy [*8])

波形

7. if 操作符

- 我们可以在sequence中使用if.else.

- 例如,当master_req为高时,下一个周期,req1或者req2应该为高,如果reg1为高,则下一个周期ack1为高,如果req2为高,则下一个周期ack2为高。

示例

property master_child regs;

@(posedge clk) master_reg (reg1 || reg2)

if(req1)

(##1 ack1)

else

(##1 ack2);

endproperty

8. first_match操作符

- first_match用来从多次满足的序列中选择第一次满足时刻,从而放弃其它满足的时刻。

sequence t1;

te1 ##[2:5] te2;

endsequence

- t1序列可以用来匹配

te1 ##2 te2,te1 ##3 te2,te1 ##4 te2或者te1 ##5 te2

sequence tsl;

first match(tel ##[2:5] te2);

endsequence

- 此序列则用来选择第一次匹配的时刻。

sequence t2;

(a ##[2:3] b) or (c ##[1:2] d);

endsequence

sequence ts2;

first_match(t2);

endsequence

-

对于上述的几种可能满足的sequence,ts2只会选择第一个满足上述

sequence的时刻点。 -

每一次PCI总线进入idIe状态时,状态机也应该返回IDLE状态。由此,在时序信息上要求,如果frame和irdy信号保持至少两个周期以上为高时,系统的状态应该为idle状态

sequnce checkBusIdle

(##[2:$] (frame &irdy));

endsequence

property first_match_idle

@(posedge clk) first_match(checkBusIdle) |-> (state == busidle);

endproperty

634

634

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?