众所周知,我校数电实验内容远超数电理论课程进度,且实验课一般都不上课(真的是一言难尽)。在深切体会了在各种平台找资料和答案的痛苦后,在假期我会陆续把实验上传,希望你不会再如此煎熬。

一、实验内容

(注:实验一的代码老师应该会在PPT上给出)

二、分析

本次实验主要应有三个模块构成,分别为杨辉三角发生器,译码器,和顶层文件。

注意顶层文件的名字应该与项目名字相同!!!

//顶层文件

module w_2495_02(codeout,clk, en,Q);

input clk,en;

output [6:0] codeout;

output [2:0] Q;

w_2495_2_1 a(clk, en,Q); //杨辉三角

w_2495_2_2 b(codeout,Q); //七位译码器

endmodule

在Verilog中模块调用与C中函数调用是很类似的,但需要注意的是:Verilog中每个模块实际上是同时进行的,也就是多线程作业,这一点和我们之前接触的C不大相同。

//杨辉三角发生器

module w_2495_2_1(clk, en,Q); //杨辉三角发生器

input clk,en;

output reg[2:0] Q;

always@(posedge clk)

begin

if(en == 1'b1)

begin

if(Q <3'd6)

Q <=Q + 1'b1;

else

Q <= 0;

end

else

Q <= Q;

end

endmodule

//译码器

module w_2495_2_2(codeout,Indec); //qi wei

input[2:0] Indec;

output reg[6:0] codeout;

always@(codeout)

begin

case(Indec)

3'd0: codeout=7'b0000001;

3'd1: codeout=7'b0000011;

3'd2: codeout=7'b0000111;

3'd3: codeout=7'b0001111;

3'd4: codeout=7'b0011111;

3'd5: codeout=7'b0111111;

3'd6: codeout=7'b0000000;

default codeout=7'bx;

endcase

end

endmodule

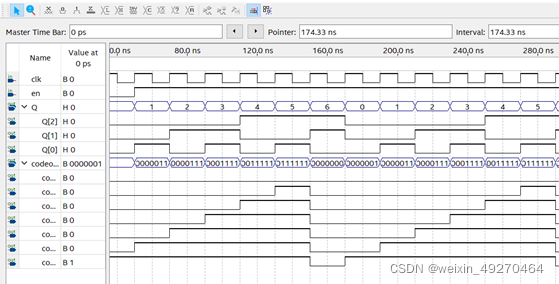

三、波形仿真

(仿真的具体操作在一个叫“Quartus操作入门”的pdf里,在群里找找自己下载下来看就好啦)

提醒:如果你是某位比较严格的老师验收,记得将左侧的信号名展示全,还有头顶的文件名。显示最好不要用二进制,虽然我觉得挺直观的。像上图这样的截图是要被抓起来扣分的!!!(你猜猜我是怎么知道的,泪目)

四、引脚分配表

| 信号名 |

主板器件 |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

475

475

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?