目录

本文仅作为个人学习心得和使用记录

1. DW_apb_uart规格简述

目前我使用DW_apb_uart协议是4.01a版本。该版本有如下特性:

- 支持AMBA APB接口

- 支持错误启动位检测

- 支持可编程小数波特率设置

- 支持数据位宽(5~8bit)和停止位位宽(1bit,1.5bit,2bit)可配置

- 支持校验位选配(奇校验,偶校验,固定1校验,固定0校验,无校验)

- 支持非FIFO模式串口收发

- 支持FIFO模式,用于缓冲收发数据,FIFO深度可以设置为0, 16, 32, 64, 128, 256, 512, 1024, 2048

- 支持DMA方式收发数据,可配置触发水线

- 支持中断,可通过配置触发水线,控制中断时机

- 支持红外模式

- 支持RS485接口,支持硬件自动控制DE/RE

- 支持用于多机通讯的9bit模式

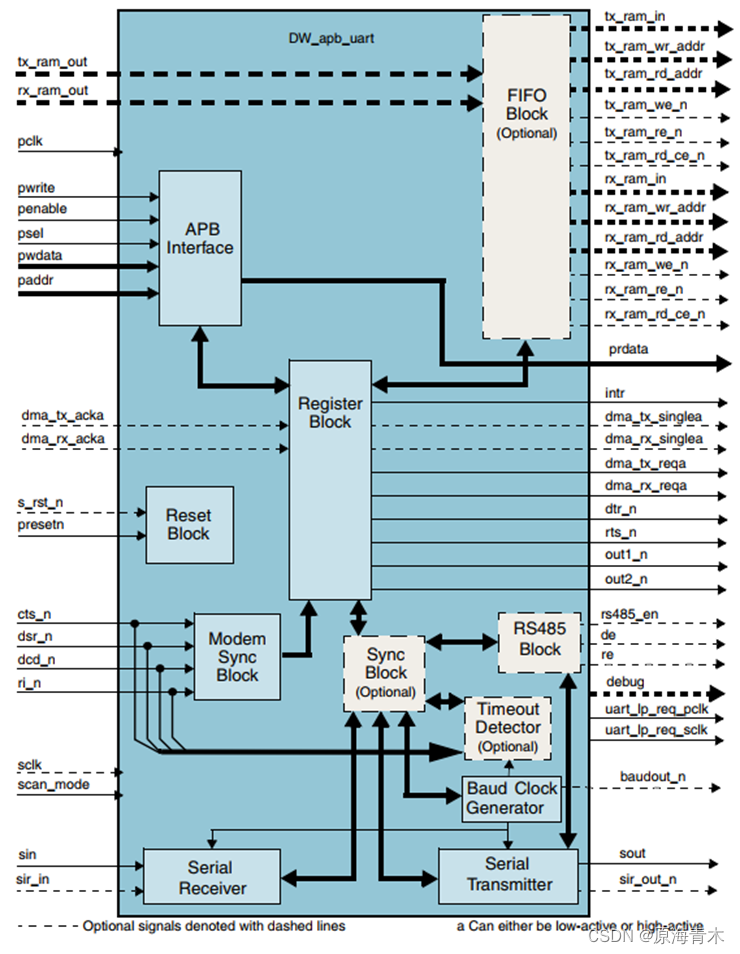

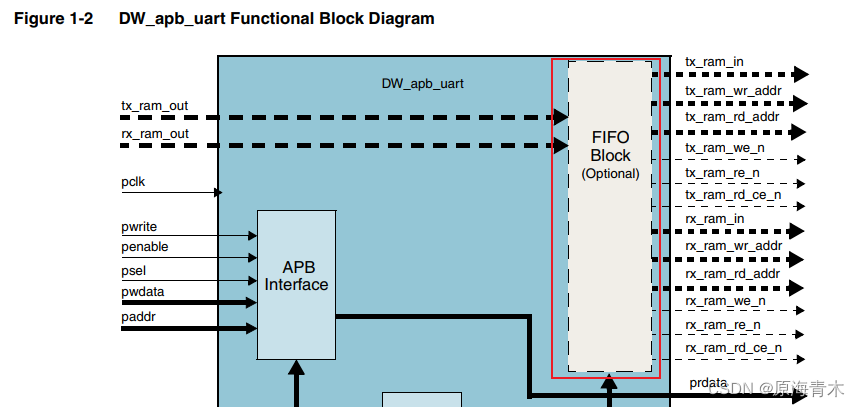

2. DW_apb_uart逻辑架构

各个模块功能介绍如下:

(1)Reset block:复位时钟

(2)APB interface :APB slave interface,连接到APB总线,实现数据传输和寄存器读写逻辑;

(3)Register block:寄存器模块

(4)Modem Synchronization block:同步调制解调器输入信号;

(5)FIFO block (optional) :当使用内部RAM或可选信号控制外部RAM时,负责FIFO控制和存储;

(6)Synchronization block (optional) :当外围设备被配置为具有单独的串行数据时钟(即双时钟实现)时实现时钟同步。DW_apb_uart可配置为具有一个系统时钟(pclk)或两个系统时钟(sclk)。实施第二个异步串行时钟(sclk)可适应准确的穿行波特率设置以及APB总线接口要求。选择两个时钟设计时,使用同步模块用于同步两个系统时钟边界的所有控制和数据。数据同步模块具有待处理数据功能。

(7)Timeout Detector block (optional) :数据收发超时检测;

(8)Baud Clock Generator :产生发送或者接收数据的波特率时钟

(9)Serial Transmitter –将写入UART的并行数据转换为串行形式发送出去,支持下面2种模式:

❑ Serial UART

❑ IrDA 1.0 SIR

(10)Serial Receiver:将以UART或IrDA 1.0 SIR格式接收的串行数据字符转换为并行形式

(11)RS485 block (optional) :当配置为具有RS485接口时,负责生成RS485收发器所需的驱动器启用(de)和接收器启用(re)信号;

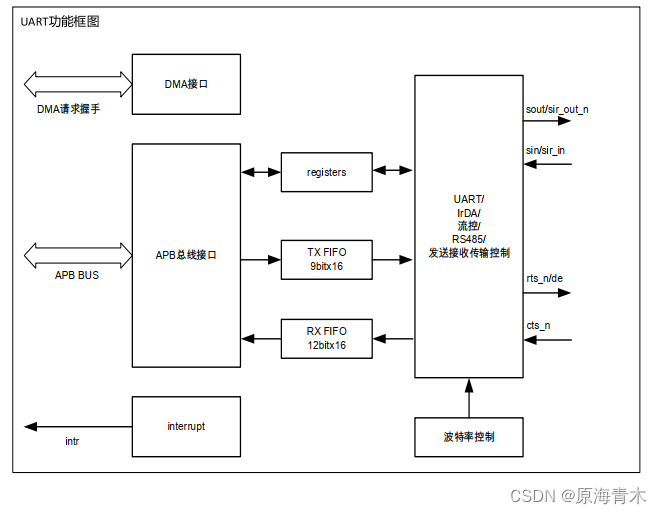

简化后的框图入上图所示:UART 最大可通过 4 个专用引脚与外部器件通讯,部分引脚在不同模式下的功能有所区别,具体功能如下:

(1)sout/sir_out_n:非红外 IrDA 模式下该引脚为常规 UART 的 TX 输出;红外模式该引

脚为红外协议下 TX 输出。

(2)sin/sir_in:非红外 IrDA 模式下该引脚为常规 UART 的 RX 输入;红外模式该引脚为

红外协议下 RX 输入。

(3) rts_n/de: 是一个输出信号, 四线流控模式下该引脚输出请求发送信号; RS485 模式

该引脚控制外部驱动的输出使能。非流控和 RS485 模式该引脚不会使用。

(4)cts: 是一个输入信号, 四线流控模式下该引脚接收清除发送信号,和 rts_n 握手。非流控模式该引脚不会使用。

3. DW_apb_uart功能介绍

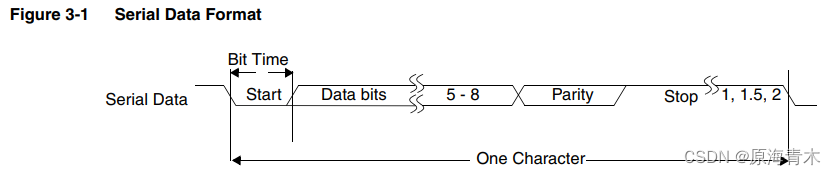

3.1 UART串行通信协议

DW_apb_uart通信数据格式如上图3-1所示,除了基本的开始位、停止位和奇偶校验位,DW_apb_uart还支持5~8bit数据位宽和1bit、1.5bit、2bit停止位位宽。

DW_apb_uart通过Line Control Register(LCR寄存器)控制串行字符的特性。

uart传输中所有的比特数据都是在完全相同的时间内传输的,只有当使用1.5bit停止位时例外,它多了0.5bit。每个bit传输的时间称为比特周期或比特时间;1bit时间等于16倍波特率时钟(这里指uart控制器工作时钟),这里就是所谓的支持16倍过采样。

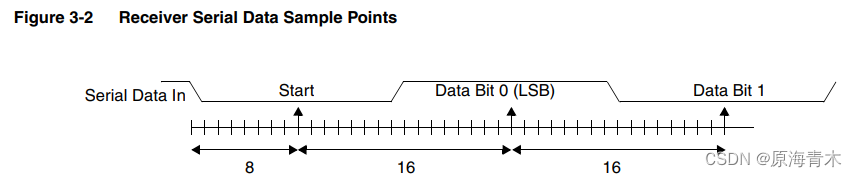

为了确保线路的稳定性,一旦检测到起始位,UART接收器就在比特时间的中点位置对串行输入数据进行采样。因为传输每个比特所需的波特率时钟数量是已知的,所以计算采样的中点并不困难;即在起始位的中点采样之后每16个波特时钟采样一次。如下图3-2所示。

配合串行输入去抖动滤波,毛刺信号将会被过滤掉,在线路上不会检测到电平转换,这种采样有助于避免检测到错误的起始位。如果毛刺信号足够宽,无法通过去抖动进行滤波,线路上则会检测到一个下降沿,只有在经过半位bit时间后线路再次被采样为低时,才认为是检测到起始位。

3.2 9bit模式

9bit 模式用于一主多从的情况下,当主机发起数据时,发送的第一个byte是地址信息,用于确定和哪个从机通信。第9bit用来表明当前的byte是地址还是数据,当第9bit是1时,表示的是地址,当第9bit是0时,表示的是数据。

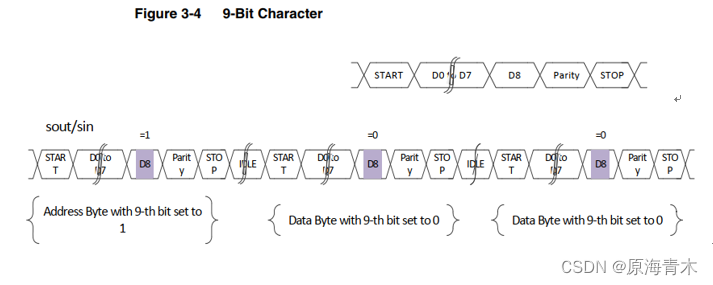

DW_apb_uart可以被配置为在发送和接收模式下都支持9bit数据传输。第9bit出现在字符串第8位之后、奇偶校验位之前。下图3-4显示了一般情况下的串行传输格式,其中D8表示第9bit。

9bit 模式下有2种Transmit Mode:

(1) Transmit Mode 0

THR和STHR都是8bit位宽,用户需要配置地址信息到TAR,配置数据到THR/STHR, SEND_ADDR用来控制什么时候发送地址。(In this mode, (LCR_EXT[3]) is set to 0)

(2)Transmit Mode 1

THR和STHR都是9bit位宽,不再使用TAR寄存器,用户需要在软件上控制THR/STHR的第9 bit来指明当前的信息是数据还是地址。(In this mode, (LCR_EXT[3]) is set to 1)

9bit 模式下有2种Receive Mode:

(1)Hardware Address Match Receie Mode

硬件自动识别第9bit是1还是0,如果是1且地址匹配,会把响应的标志位置1,并把下一个byte数据放到RXFIFO。(In this mode, ADDR_MATCH (LCR_EXT[1]) is set to 1)

(2)Software Address Mvatch Receive Mode

软件上进行地址匹配和数据处理。(In this mode, ADDR_MATCH (LCR_EXT[1]) is set to 0)

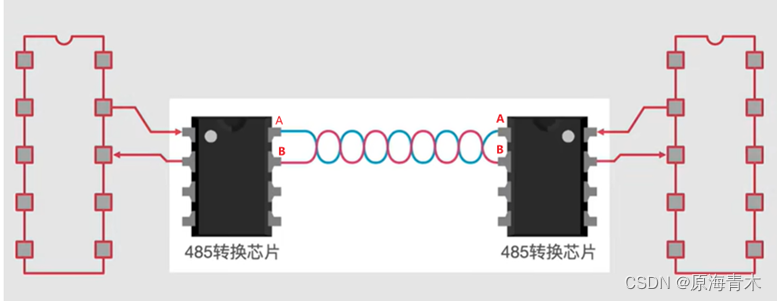

3.3 RS485模式

DW_apb_uart支持RS485接口,通过以下流程配置 RS485 接口模式:

(1)TCR.rs485_en 用于使能或者关闭 RS485 模式。

(2)TCR.de_pol 用于选择 de 的有效极性。

(3)TCR.xfer_mode 用于选择不同模式类型。

(4)DE_EN 寄存器用于通过软件控制 de。

(5)RE_EN 寄存器用于通过软件控制 re。

(6)DET 寄存器用于配置 de 的 assertion 和 de-assertion 时间。

DW_apb_uart RS485支持下面3种模式:

(1)Full Duplex Mode

全双工模式。(In this mode, XFER_MODE of TCR is set to 0.)

(2) Software-Controlled Half Duplex Mode

软件控制半双工模式,通过软件配置DE/RE信号控制数据收发。(In this mode, XFER_MODE of TCR is set to 1.)

(3)Hardware-Controlled Half Duplex Mode

硬件控制半双工模式,逻辑同过判断TXFIFO是否为空来控制DE/RE信号。(In this mode, XFER_MODE of TCR is set to 2)

RS485特点:

(1)收发器输出A、B之间的电平为+2V~+6V,是逻辑“1”;为-6V~-2V,是逻辑“0”;

(2)传输速率高(10Mbps);

(3)传输距离达到1200m;

(4)具有多站点传输能力,即总线上允许挂接多达128个收发器,可建立设备网络;

(5)有“使能”控制信号,可使收发器处于高阻状态,切断与传输线的连接;

RS485收发控制方法:

RS485属于半双工总线,在实际使用时一般采用主机轮询或令牌传递的方法来分配总线控制权,RS485设备需要进行发送和接收的方向转换。

最常用的RS485收发换向方法是程序换向,即由MCU的一个I/O端口控制RS485收发器件的收发使能引脚。

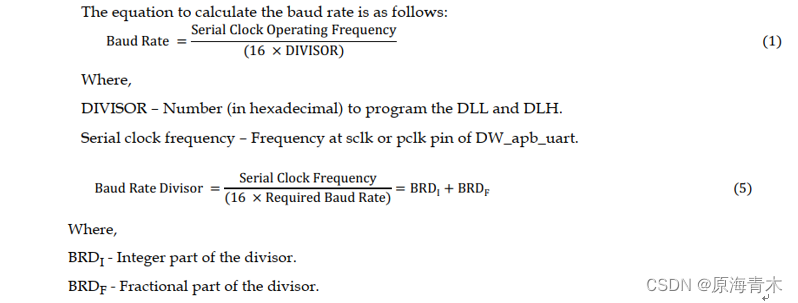

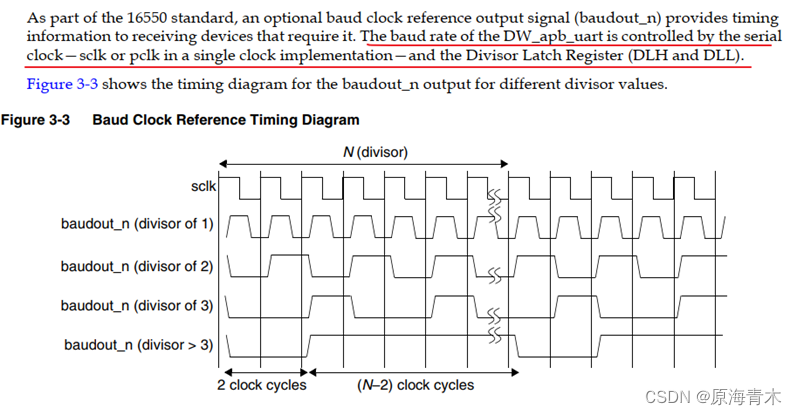

3.4 波特率小数分频

波特率可软件配置,支持小数部分设置。计算公式如下:

其中分频系数divisor由DLH和DLL寄存器控制。

以 DLF_SIZE为6举例,分别计算整数部分和小数部分取值:

/*

* Baud Rate = Serial Clock Operating Frequency / (16 × DIVISOR)

*

* ==> DIVISOR = Serial Clock Operating Frequency / (16 × Baud Rate)

* = (Serial Clock Operating Frequency / 16 / Baud Rate

* = (Serial Clock Operating Frequency >> 4) / Baud Rate

* = Div_Integer + Div_Fractional

*

* ==> uartdivi = Div_Integer

* = (Serial Clock Operating Frequency >> 4) / Baud Rate (unsigned short类型保存数据时自动取整);

*

* 当前 DLF_SIZE = 6,精度是6bit ,可以等分成为64份

* ==> uartdivf = Div_Fractional x 2^6

* = Div_Fractional << 6

* = (DIVISOR - uartdivi) << 6

* = ((Serial Clock Operating Frequency >> 4) / Baud Rate - uartdivi) << 6

* = ((Serial Clock Operating Frequency >> 4) / Baud Rate)<< 6 - (uartdivi << 6)

* = (Serial Clock Operating Frequency << (6 - 4) / Baud Rate) - (uartdivi << 6)

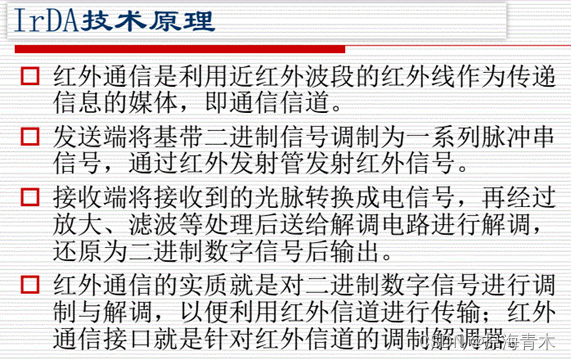

*/3.5 红外模式

DW_apb_uart 协议规定:支持双向数据传输,传输波特率最大支持115.2K,有1个起始位,8个数据位,1个结束位,没有校验位。

IrDA1.0协议:又称为SIR(Serial InfraRed),是基于HP开发出来的一种异步、半双工的红外通信方式。通过对船型数据脉冲和光电信号脉冲编码实现红外数据传输,最高通信速率只有115.2kbps,适用于串行端口的速率。

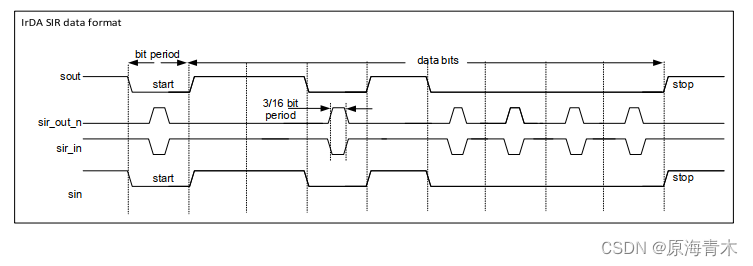

MCR.sire 用于使能或者关闭 IrDA1.0 SIR 模式,使能该模式后串行数据的发送和接收通过sir_out_n 和 sir_in 表示。端口上在一个 bit 时间内传输了一个红外脉冲表示逻辑 0,否则表示逻辑 1。每个脉冲的宽度是正常串行位时间的 3/16。因此每个新字符以起始位的红外脉冲开始。

当启用IrDA-SIR 模式时,数据传输只能以半双工方式进行。 由于 IrDA SIR 物理层规定了传输和

接收之间的最小 10ms 延迟,这个 10ms 的延迟需要软件产生。

3.6 FIFO

DW_apb_uart支持配置使能用于缓冲传输和接收数据的FIFO;如下图1-2所示。

如果未选择FIFO支持,则逻辑不实现FIFO,这样的话,只能在RBR和THR寄存器中存储一个接收数据字节和发送数据字节;在这种操作模式下,大多数增强功能都不可用。

3.7 时钟

DW_apb_uart可以配置为具有一个系统时钟(pclk)或两个系统时钟(pclk和sclk)。第二个异步串行时钟(sclk)适用于串行波特率设置以及满足APB总线接口要求。

当使用单个系统时钟时,系统时钟设置会受到很大限制。当选择使用双时钟设计时,需要使用同步模块,用于跨两个系统时钟域同步所有控制和数据。

3.8 中断

UART 模块通过 intr 输出(高有效)通知 MCU 系统该模块有中断发生,中断的输出需受到中断使能的控制,中断使能控制可参考 IER 寄存器。以下中断类型可以使用IER寄存器启用:

■ 接收器错误

■ 接收器数据可用

■ 字符超时(仅在FIFO模式下)

■ 变送器保持寄存器为空,处于/低于阈值(在可编程THRE中断模式下)

■ 调制解调器状态

■ 忙检测指示

当发生中断时,CPU可访问IIR寄存器获取中断信息。

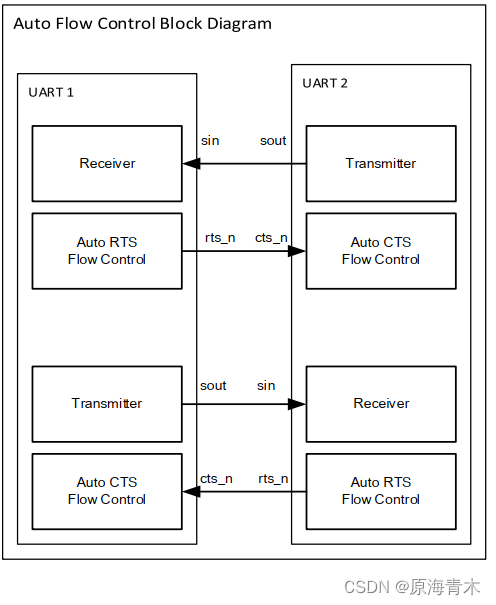

3.9 硬件流控

硬件流控制常用的有RTS/CTS流控制和DTR/DSR(数据终端就绪/数据设置就绪)流控制。

RTS(Require ToSend,发送请求)为输出信号,用于指示本设备准备好可接收数据,低电平有效,低电平说明本设备可以接收数据。

CTS(Clear ToSend,发送允许)为输入信号,用于判断是否可以向对方发送数据,低电平有效,低电平说明本设备可以向对方发送数据。

控制流程介绍:

假定A、B两设备通信,A设备的RTS 连接B设备的CTS ;A设备的CTS连接B设备的RTS。前一路信号控制B设备的发送,后一路信号控制A设备的发送。对B设备的发送(A设备接收)来说,如果A设备接收缓冲快满的时发出RTS信号(高电平)(意思通知B设备停止发送),B设备通过CTS 检测到该信号,停止发送;一段时间后A设备接收缓冲有了空余,发出RTS信号(低电平),指示B设备开始发送数据。A设备发(B设备接收)类似。

DW_apb_uart 可配置 Auto-RTS 和 Auto-CTS 串行数据流控制模式,功能应用框图入上图所示。

Auto-RTS 功能有效的前提:

(1)MCR.rts 和 MCR.afce 设置为 1

(2)FIFO 使能 FCR.fifoe 开启

(3)SIR 模式 MCR.sire 关闭

UART 使能 Auto-RTS 时,当 UART 的 RX FIFO 阈值达到 FCR.rt 设置的阈值时,rts_n输出信号会强制变成无效信号(高电平)。此时如果 rts_n 连接到另一个UART设备的cts_n,对端的 UART 会停止发送数据,直到UART自己 RX FIFO 有可用空间。

Auto-CTS 功能有效的前提:

(1)MCR.rts 和 MCR.afce 设置为 1

(2)FIFO 使能 FCR.fifoe 开启

(3)SIR 模式 MCR.sire 关闭

启用自动 CTS 时,当 cts_n 输入信号无效(高电平)时,UART 会停止发送,避免接收端的 RX FIFO 溢出。如果 cts_n 输入信号在发送最后一个停止位之前仍是有效(低电平),则 UART 在传输停止之前还会继续发送一帧数据。当发送被禁用时,发射器 FIFO 仍可被写入,甚至溢出。

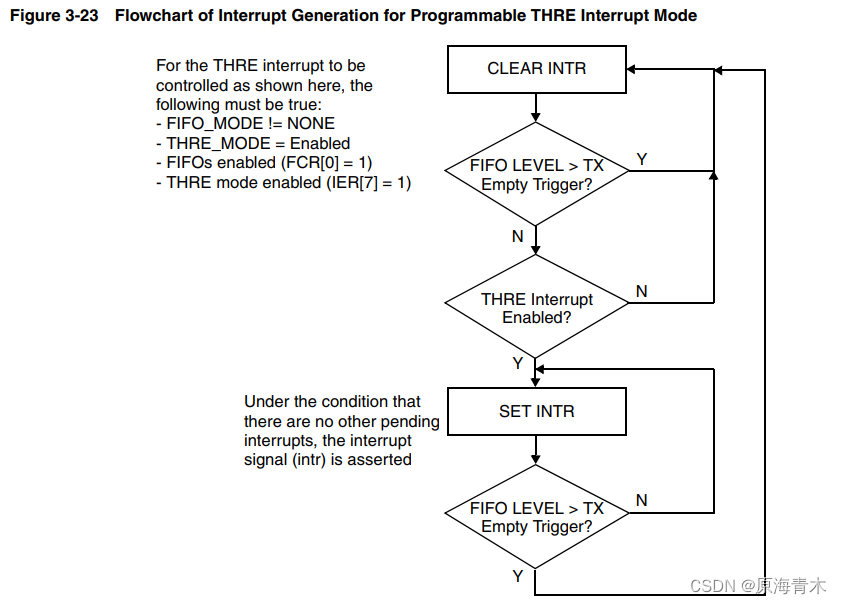

3.10 可编程THRE中断

DW_apb_uart可以使能可编程THRE中断模式,以增加系统性能,如果没有使能FIFO,则不能选择该模式。

■ 当没有选择可编程THRE中断模式时,UART控制器将不实现任何相关的逻辑,并且软件无法启用该模式,这样减少总门数,减小芯片面积。

■ 当选择了可编程THR中断模式时,软件可以配置中断启用寄存器(IER[7])启用该模式。

当FIFO和THRE模式被实施和启用时,当FIFO内数据量低于FIFO空阈值时,THRE 中断和dma_tx_req_n信号将触发激活,并不是当FIFO完全空了才会激活,如图3-23的所示:

FIFO空阈值可通过编程FCR[5:4]选择。可用的空阈值为:

■ empty

■ 2

■ ¼

■ ½

3.11 DMA

DW_apb_uart 有两个并行的 DMA 通道,可以通过输出的dma_tx_req/dma_tx_single_req信号 来告知系统TX FIFO 可以被写入了;输出dma_rx_req/ dma_rx_single 信号来告知系统接收的数据可以被读取了。 DMA 模块根据UART的 DMA 请求进行数据传输。

dma_tx_req 在以下情况下会变为有效:

(1)在非 FIFO 模式下,发送保持寄存为空。

(2)在 FIFO 模式下,当 THRE 中断模式关闭且发送 FIFO 为空时。

(3)在 FIFO 模式下,当 THRE 中断模式开启且发送 FIFO 内数据小于配置的阈值。

dma_rx_req 在以下情况下会变为有效:

(1)在非 FIFO 模式下,有一帧数据已经存放在了接收缓存寄存器中。

(2)在 FIFO 模式下,当接收 FIFO 配置内数据大于等于配置的阈值时。

3.12 时钟和复位

UART 模块本身有两个时钟:

(1)一个是 pclk,系统内部 cpu 总线同 UART 模块交互的 apb 总线时钟,CRG 模块中对UART 模块的软件复位不会复位 pclk 管控的部分,如寄存器配置操作。

(2)一个是 sclk,UART模块内部工作时钟,主要用于控制UART收发串行数据。CRG 模块中对 UART 模块的软件复位会复位 sclk 时钟管控部分

UART 的波特率产生使用的是 sclk,配置和计算波特率的分频值注意sclk。

本文详细介绍了DW_apb_uart的规格、逻辑架构,包括波特率小数分频、9bit模式、RS485接口、红外模式、DMA支持、硬件流控、中断机制和时钟复位等内容,适合深入理解该协议的开发者阅读。

本文详细介绍了DW_apb_uart的规格、逻辑架构,包括波特率小数分频、9bit模式、RS485接口、红外模式、DMA支持、硬件流控、中断机制和时钟复位等内容,适合深入理解该协议的开发者阅读。

2051

2051

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?