FPGA基础程序学习

第二节 UART通信

回环

//判断接收完成信号,并在串口发送模块空闲时给出发送使能信号

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

tx_ready <= 1’b0;

send_en <= 1’b0;

send_data <= 8’d0;

end

else begin

if(recv_done_flag)begin //检测串口接收到数据

tx_ready <= 1’b1; //准备启动发送过程

send_en <= 1’b0;

send_data <= recv_data; //寄存串口接收的数据

end

else if(tx_ready && (~tx_busy)) begin //检测串口发送模块空闲

tx_ready <= 1’b0; //准备过程结束

send_en <= 1’b1; //拉高发送使能信号

end

end

end

endmodule

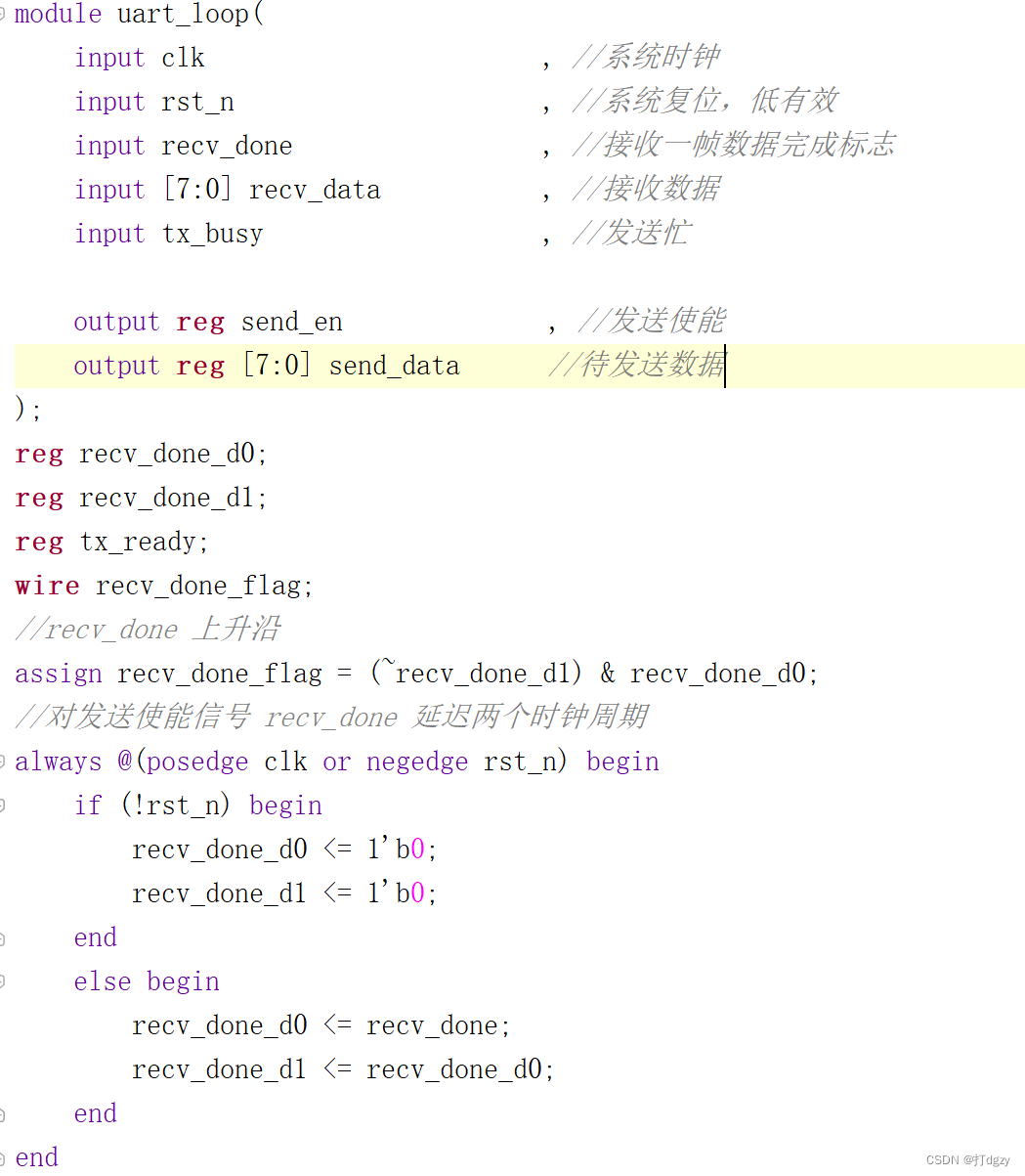

uart_loop 模块的代码比较简单,首先代码的 25 至 38 行实现了上升沿检测功能。当检测到 recv_done 信

号的上升沿时,recv_done_flag 输出一个时钟周期的高电平,标志着串口接收模块接收到了一帧数据。在代

码的 48 至 52 行,在判断到 recv_done_flag 为高电平时,寄存接收到的数据 recv_data 到 send_data 中;同时

将 tx_ready 信号拉高,表示已经准备好了待发送的数据。另外还要将 send_en 信号拉低,为接下来产生一个

上升沿作准备。

uart_loop 模块还有一个输入信号 tx_busy,它是由串口发送模块所输出,该信号为高电平表示串口发送

模块正处于发送过程中。在代码的第 53 行,当 tx_ready 信号为高电平时,如果检测到 tx_busy 为低电平,

则说明串口发送模块处于空闲状态。此时将 send_en 信号拉高,由此产生一个上升沿,以启动串口发送模块

的发送过程,将寄存到 send_data 中的数据发送出去。于此同时,将 tx_ready 信号拉低,等待下一个串口接

收数据的到来

本文详细介绍了FPGA中UART通信的回环检测机制。当recv_done标志上升沿触发时,模块准备发送接收的数据。一旦检测到串口发送模块空闲(tx_busy为低),便拉高send_en启动发送,将send_data中的数据送入串口。这个过程确保了数据的无缝传输并有效利用了串口资源。

本文详细介绍了FPGA中UART通信的回环检测机制。当recv_done标志上升沿触发时,模块准备发送接收的数据。一旦检测到串口发送模块空闲(tx_busy为低),便拉高send_en启动发送,将send_data中的数据送入串口。这个过程确保了数据的无缝传输并有效利用了串口资源。

1575

1575

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?