定长序列或不连续序列的检测

对于定长序列,即每n个数为一组,前边的数不满足则直接跳到下一组开始检测,这种情况就需要创建一个sequence把每n个数装进来检测,再定义一个count用来计数,当count达到序列长度就和模板匹配,若匹配成功match则拉高。

VL27 不重叠序列检测

请编写一个序列检测模块,检测输入信号(a)是否满足011100序列, 要求以每六个输入为一组,不检测重复序列,例如第一位数据不符合,则不考虑后五位。一直到第七位数据即下一组信号的第一位开始检测。当信号满足该序列,给出指示信号match。当不满足时给出指示信号not_match。

模块的接口信号图如下:

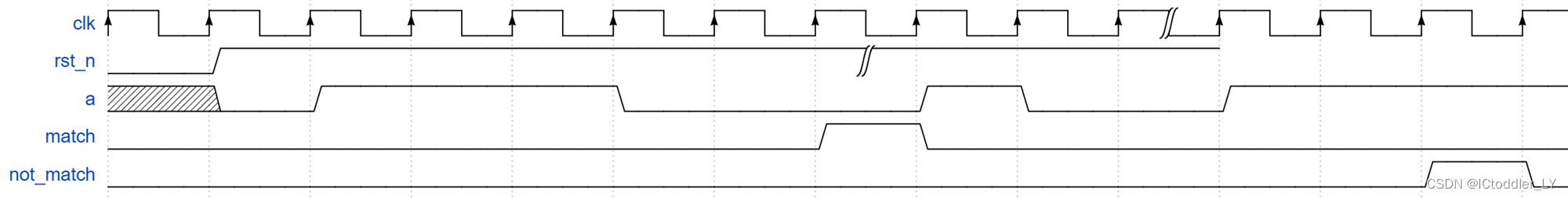

模块的时序图如下:

请使用Verilog HDL实现以上功能,要求使用状态机实现,画出状态转化图。并编写testbench验证模块的功能。

输入描述:

clk:系统时钟信号

rst_n:异步复位信号,低电平有效

a:单比特信号,待检测的数据

输出描述:

match:当输入信号a满足目标序列,该信号为1,其余时刻该信号为0

not_match:当输入信号a不满足目标序列,该信号为1,其余时刻该信号为0

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

output reg match,

output reg not_match

);

//reg variable

reg [5:0] seq;

reg [2:0] count;

always @ (posedge clk or negedge rst_n) begin

if(~rst_n) begin

count <= 3'b0;

end

else begin

if(count == 3'd5) begin

count <= 3'd0; //when count is full,back to 0.

end

else begin

count <= count + 1'b1;

end

end

end

always @ (*) begin

case (count)

3'd0: seq[5] <= data;

3'd1: seq[4] <= data;

3'd2: seq[3] <= data;

3'd3: seq[2] <= data;

3'd4: seq[1] <= data;

3'd5: seq[0] <= data;

default : seq <= 6'b0;

endcase

end

always @ (posedge clk or negedge rst_n) begin

if(~rst_n) begin

match <= 1'b0;

not_match <= 1'b0;

end

else begin

if(count == 3'd5) begin

if(seq == 6'b011100) begin

match <= 1'b1;

not_match <= 1'b0;

end

else begin

match <= 1'b0;

not_match <= 1'b1;

end

end

else begin

match <= 1'b0;

not_match <= 1'b0;

end

end

end

endmodule

这里创建的sequence和被检测序列等长,每来一个上升沿(每来一个输入信号a)就把输入放进seq同时count就+1,当count加到被检测序列长度时,seq就和模板匹配,若匹配成功match拉高。

不连续序列的检测

对于不连续序列的检测,也需要把有效输入数据(data_valid拉高时输入有效)放入一个sequence中,待序列长度达到待检测序列长度时seq与模板匹配,匹配成功match拉高。

VL28 输入序列不连续的序列检测

请编写一个序列检测模块,输入信号端口为data,表示数据有效的指示信号端口为data_valid。当data_valid信号为高时,表示此刻的输入信号data有效,参与序列检测;当data_valid为低时,data无效,抛弃该时刻的输入。当输入序列的有效信号满足0110时,拉高序列匹配信号match。

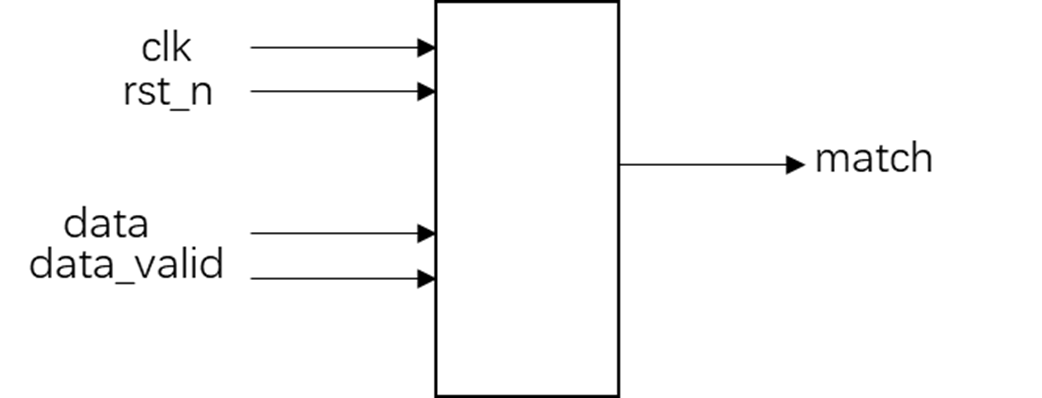

模块的接口信号图如下:

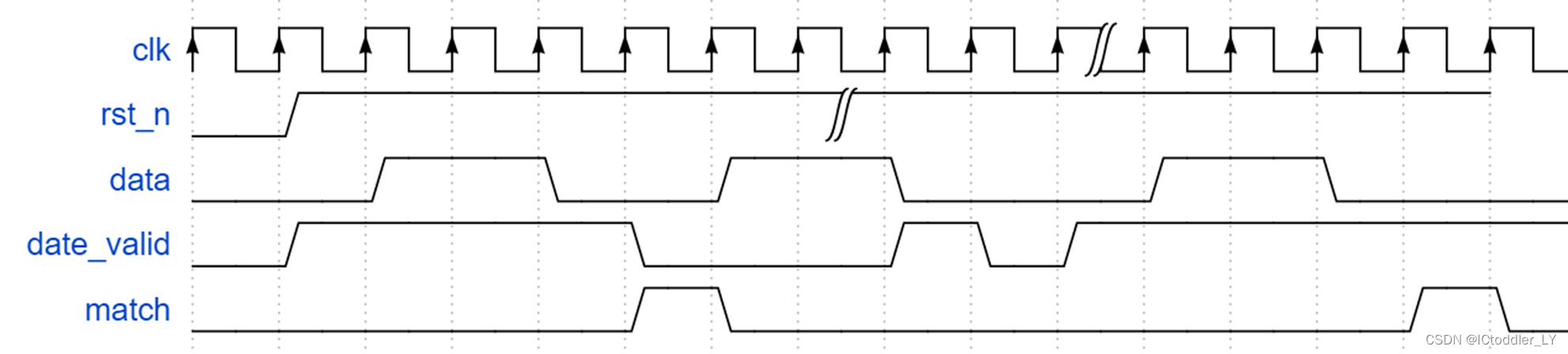

模块的时序图如下:

请使用状态机实现以上功能,画出状态转移图并使用Verilog HDL编写代码实现以上功能,并编写testbench验证模块的功能.

输入描述:

clk:系统时钟信号

rst_n:异步复位信号,低电平有效

data:单比特信号,待检测的数据

data_valid:输入信号有效标志,当该信号为1时,表示输入信号有效

输出描述:

match:当输入信号data满足目标序列,该信号为1,其余时刻该信号为0

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

input data_valid,

output reg match

);

reg [1:0] count;

reg [3:0] seq;

//one

always @ (posedge clk or negedge rst_n) begin

if(~rst_n) begin

count <= 2'b0;

end

else begin

if(count == 2'd3) begin

count <= 2'd0;

end

else begin

if(data_valid == 1'b1) begin

count <= count + 1'b1;

end

else begin

count <= 2'd0;

end

end

end

end

//two

always @ (*) begin

case(count)

2'd0 : seq[count] = data;

2'd1 : seq[count] = data;

2'd2 : seq[count] = data;

2'd3 : seq[count] = data;

default : seq <= 4'b0;

endcase

end

//three

always @ (posedge clk or negedge rst_n) begin

if(~rst_n) begin

match <= 1'b0;

end

else begin

if(count == 2'd3) begin

if(seq == 4'b0110) begin

match <= 1'b1;

end

else begin

match <= 1'b0;

end

end

else begin

match <= 1'b0;

end

end

end

endmodule

data_valid拉高情况下每来一个上升沿count就+1同时把输入数据放入seq,当count达到被检测序列长度时与模板匹配,匹配成功match拉高。

453

453

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?