verilog代码编写规则、思想(持续更新)

记录自己在编程序过程中遇到的编写规则(持续更新)

zynq中模块选择PLorPS:时序要求高,不常修改——PL;时序要求不高,解析复杂,调试经常修改,从PL拉出线来,建立数据传输线,在PS中作数据操作

规范类

1、对模块中的每个中间变量进行赋值之前,要保证变量在初始时能被复位或有初始值

2、尽量不在不同if或者其他模块中对同一个变量进行赋值改变

3、在过程块中用变量赋值、存储值等要用reg;在top中、不同模块间进行连接、传递值时要用wire

4、ila采样时,ila时钟频率和被采样时钟频率

根据采样定理ila时钟频率最好时被采样时钟频率的4倍以上,才可以得到比较好的时钟波形。但是我们只要看时钟是否work就行。只要ila时钟频率比被采样时钟频率高2倍就可以了。

5、寄存器reg用来寄存值,满足时序要求,对每一个已寄存值的寄存器,用reg中的值去连接其他模块时,要拉出来一根线wire去连接,不要直接用reg的变量去做值,特别是在模块接口,输入和输出尽量都用wire,用wire去取reg 中 的值。

reg x <= y;

wire z = x;

z-> 组合、时序逻辑

积累类

1、捕捉信号上升沿:

<1>打两拍

assign flag = ((touch_key_d0 != touch_key_d1) && (touch_key_d1 == 0))? 1'd1:1'd0;

assign touch_en = (~touch_key_d1) & touch_key_d0;

<2>打一拍,在一个时序逻辑下捕捉上升沿

always@(posedge clk)begin

x_r<=x;

up<=({x,x_r}==2'b10)?1'b1:1'b0;

end

2、用多位寄存实现信号打拍

always @ clk

x_r[2:0] <= {x_r[1:0],x} //存储当前和上两拍的值

x_r[1:0] <= {x_r[0],x} //存储当前和上一拍的值

用该寄存器的值可以方便的实现捕捉上升沿等操作

3、计数器计数时,用计数器的高位来表示更高单位的计数:

cnt[11:0] //用来计数d2304个

x[4:0] //索引d0-d17

always @clk

x[cnt[11:7]] //每128个时钟,x索引增加d1;2的7次方=128,cnt[6:0]用作128计数的单位

面向硬件的软件编写

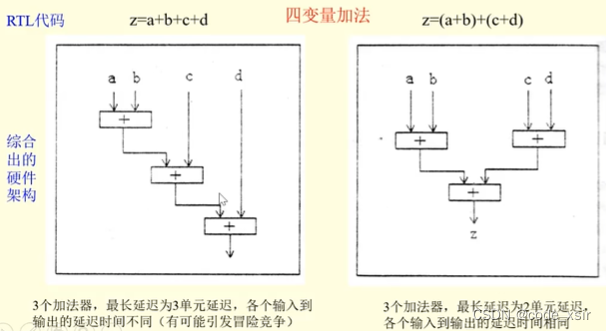

优化思想1:图示

编程思想:

1、对于模块间数据传输,要时刻保持MOS管思想,有数据流的同时,要有valid信号,去通知互连模块的什么时候读写数据。

2、触发寄存器时 要注意寄存器的当前状态值和下一状态值、在同一时钟下多级寄存器的时序关系构造

always @clk begin

reg_1 <= a; //一级寄存

reg_2 <= b; //一级寄存

reg_3 <= reg_1 //二级寄存

end

always @clk

if(reg_1 == a ) reg_4 <= c; //二级寄存

(1)DFF有输入端(D端)和输出端(Q端),D端连接部分组合电路,其值随组合电路的输入值同步变化;

(2)所谓“延迟一拍”是指当时钟上升沿来临时,D端数据会传送到Q端,即Q值相较于D值会延迟一拍;

(3)当数据变化沿与寄存器时钟上升沿重合时,可看作D端数据先变化,随即再将值传给Q端

(4)寄存器之间的延迟,即每经过一个DFF,就会增加一个时钟周期的延迟。 在时序图中要分明每一级时钟延迟寄存器的关系

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?