目录

1.始终资源的分类

时钟的设计非常的重要,合理利用始终资源设计始终网络。

提供的吩咐始终资源,可以保证低抖动、高精度灯时钟输出特性,对时钟网络的色设计具有非常重要的帮助。

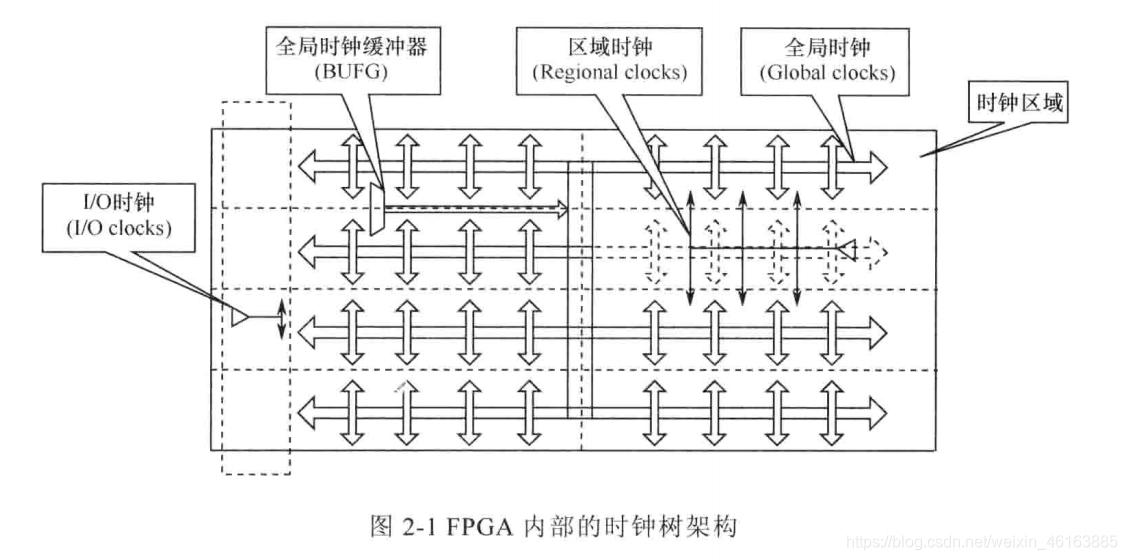

时钟网络被分为全局时钟,区域时钟和I/O时钟。

同时被分为多个不同的始终区域。如下图:

全局时钟是为所有时钟输入设计的专用互联网络,可以覆盖FPGA中的各种资源。

通过使用专用始终缓冲(BUFG,非常重要的资源,在工作中会经常见到)和驱动结构,确保了整个芯片的任意一个触发器的电延迟是等长的,并且全局时钟网络可以提供低延时和低抖动的时钟。(常被用在时钟,快速信号和高扇出信号的布线)

区域始终是驱动时钟区域内所有资源的时钟网络,对于该时钟区域内部的资源,区域始终拥有更好的时钟特性。(在基于源同步接口设计中使用区域时钟网络更加好,但是在通常的设计中并不使用,至少我很少用,多数使用全区时钟,那样可以更少的减少延迟。)

FPGA 中的全局始终资源是一种进行设计的布线资源,路线很长且扇出系数很大,一般使用全铜层工艺实现。

全局时钟设计采用了专用始终缓冲与驱动结构,是的全局时钟达到芯片内部所有资源(包括CLB,I/O单元,Block RAM 和DSP 核等) 的时延核抖动都最小。

全局时钟网络到FPGA 内部的各种资源的采样始终同时到达,使得信号的时序计算核分析较为容易,不会产生不稳定的情况。

在FPGA设计中需控制时钟信号数量,尽力保证所有时钟信号都使用全局始终网络驱动。

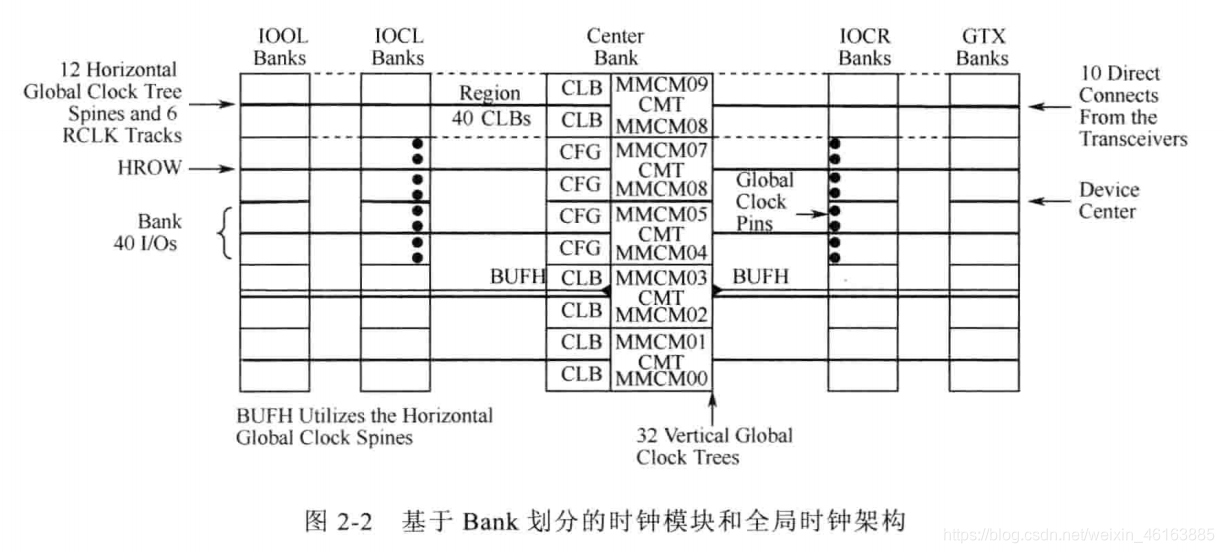

2.FPGA 时钟管理器说明

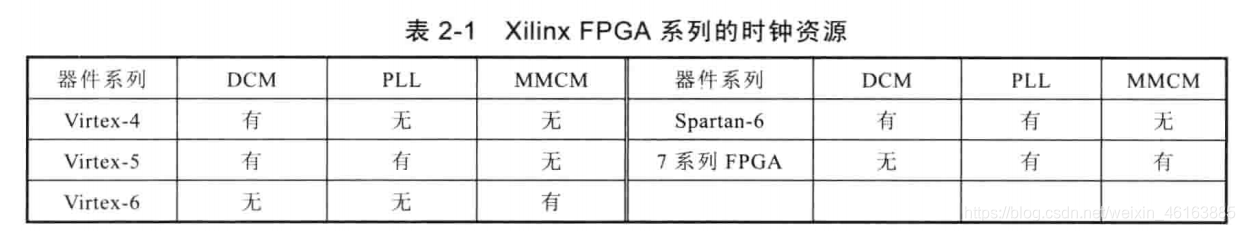

DCM(数字时钟管理器),适用于实现延迟锁相环(DLL),数字平路综合器,数字移相器核数字频谱扩展器;

混合始终管理单元(MMCM),采用基于PLL的混合模式,实现最低的Skew核抖动滤波,为FPGA 设计提供了更高性能的始终管理功能;MMCM比PLL 提供更精确的时钟分屏功能;

3.FPGA 时钟详述

3.1 时钟相关的基本概念

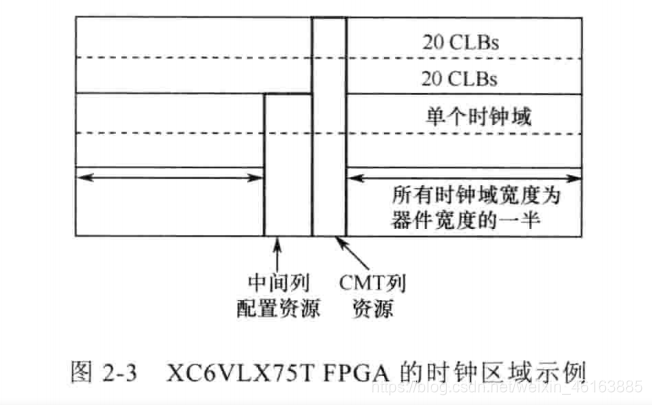

为更好的控制时钟,时钟被分为若干个时钟区域。如下图:

(1)时钟区域(Region)

FPGA 在水平方向以时钟区域为组织结构,单个时钟区域的高度为40个CLB,时钟宽度为器件宽度的一半。

5564

5564

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?