壹 | 引言

前几天与好友聚餐,席间好友向我们分享了他近期面试硬件研发岗的过程,在技术面试环节,其中一个问题问:设计AD采样电路时,如何选择运放?需要注意哪些参数?

当时我能联想到的要素只有:输入/输出范围、供电电源、带宽这些参数。

感觉到自己对这个问题似乎也没什么把握,回来后查找资料,发现确实远不止这几点,遂整理记录下来。

贰 | 运放的作用

示例:pandas 是基于NumPy 的一种工具,该工具是为了解决数据分析任务而创建的。

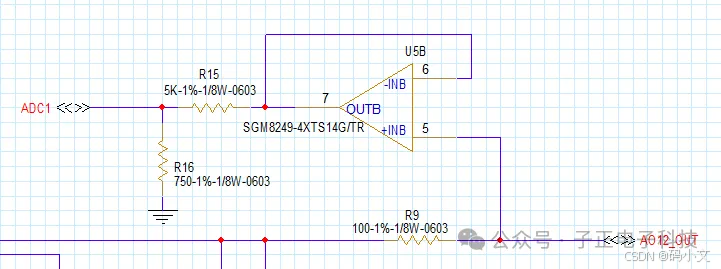

在常见的ADC采集电路中,运算放大器大多是用作信号调理。

· 放大:放大小信号,让信号保持在合理的采样区间中;

· 缓冲:对信号与ADC采集通道进行隔离,避免信号过冲或其它异常情况下,损坏ADC芯片;

· 滤波:一般情况下,运算放大器内部都具备滤波功能,可以在ADC采样前,先对信号进行硬件上的滤波处理;

叁 | 运放的核心参数

在ADC采集电路设计中,运放选型的核心参数如下:

· 输入/输出范围

运放的输入和输出电压范围必须能够覆盖AD芯片的输入范围。

假设AD采集范围是0~5V,那运放的输出必须也要达到这个范围,并且也要满足前级信号的范围。

另外,如果ADC芯片是单电源供电,运放可能也需要单电源工作,且支持轨到轨输出,这样能够充分利用AD采集的动态范围。

· 轨到轨输出(R2R)

输入轨到输出轨大小保持同步。

· 精度

对于高精度的应用,比如测量静态电压,运放的失调电压和温漂必须足够小,否则会出现较大的静态误差,影响测量结果。

当出现静态误差试,可能需要选择零漂移运放或者额外进行外部校准,这样做无疑会增加成本或复杂度。

· 带宽

运放的带宽需要足够高,以处理输入信号的频率,尤其是在高速采样的情况下。

如果运放的带宽不够,信号可能会有失真或者延迟,导致ADC无法准确采集。这里主要考虑增益带宽积(GBW),因为放大倍数会影响可用带宽。

· 增益带宽积(GBW)公式:

GBW≥信号最高频率×闭环增益×安全系数(通常GBW值为5或10)

· 压摆率(Slew Rate)

压摆率决定了运放输出信号的最大变化速率。

当输入信号的变化很快时,比如高频或大幅度的信号,压摆率不足的情况下,输出可能会跟不上,导致采样失真。

所以需要计算信号的最大斜率,确保运放的压摆率满足要求。

比如,最大电压变化率是Vpeak乘以2πf,压摆率必须大于这个值。

计算公式:

![]()

· 电源/功耗

电源电压和功耗是系统级设计的考虑因素,同时也是AD采集电路中关键的一环。

如果系统是电池供电,可能需要低功耗运放。

同时,运放的电源电压需要与系统其他部分兼容,比如是否使用单电源或双电源供电。

在低功耗场景下(如电池供电),需选择低IQ运放(如微功耗运放)。

· 噪声性能

噪声也是一个关键参数,尤其是对于高分辨率的ADC。

运放的噪声包括电压噪声和电流噪声,这些噪声会被放大并叠加到信号上,影响ADC的信噪比。

需要根据ADC的分辨率和输入信号幅度来选择低噪声的运放。

比如,16位以上的ADC可能需要非常低的噪声运放,否则噪声可能会淹没小信号。

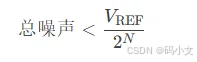

总噪声需小于ADC的LSB值:

例如:5V参考电压的16位ADC,LSB≈76μV,需运放噪声远低于此。

· 动态响应

· 建立时间(Settling Time)

在高速或多通道切换时很重要。运放的输出需要在ADC的采样时间内稳定到足够精度,否则会导致采样错误。

特别是在多路复用器中快速切换通道时,运放必须能够快速稳定到所需的误差范围内。通常要求运放在采样时间内稳定到目标精度(如0.01%)。

· 输出驱动能力

需驱动ADC输入电容(如SAR ADC的容性开关负载),避免振铃或失真。

ADC的输入可能还有一定的输入阻抗,运放需要能够驱动这样的负载而不影响性能。

· 输入阻抗

高输入阻抗(如JFET或CMOS输入)减少对高阻信号源(如传感器)的负载效应。

肆 | 总结

在设计ADC采样电路时,综合考虑以上要素基本可以满足需求,但针对特殊的场景应用,可能还需要考虑一些其它因素。

理论+经验=一板成功

希望我们都能成为硬件设计大牛。

329

329

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?