VIVADO固化程序步骤

1烧录bit文件

1、正确的将FPGA专用下载器与调试板卡或者产品连接,检查无误后打开电源上电。注:严禁带电操作。

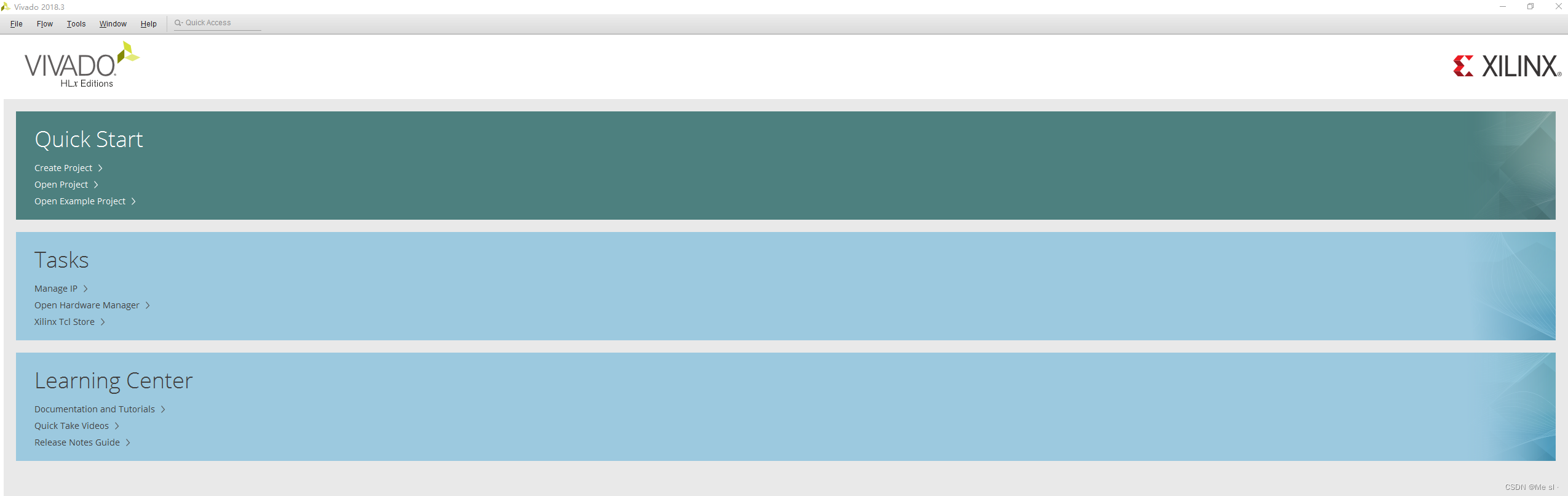

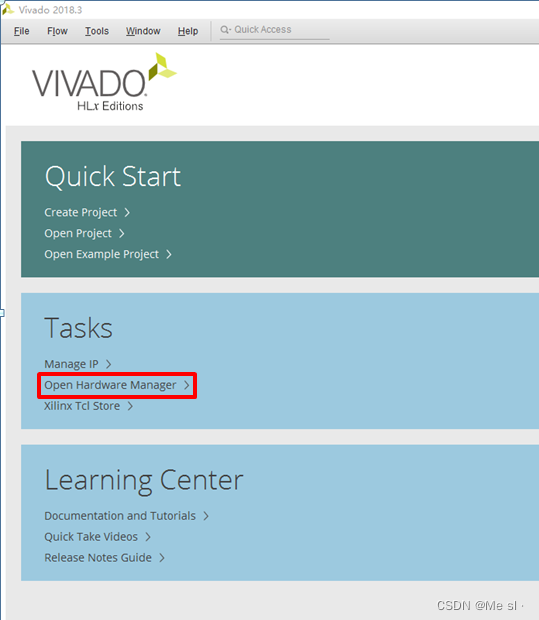

2、打开VIVADO18.3软件,如下所示:

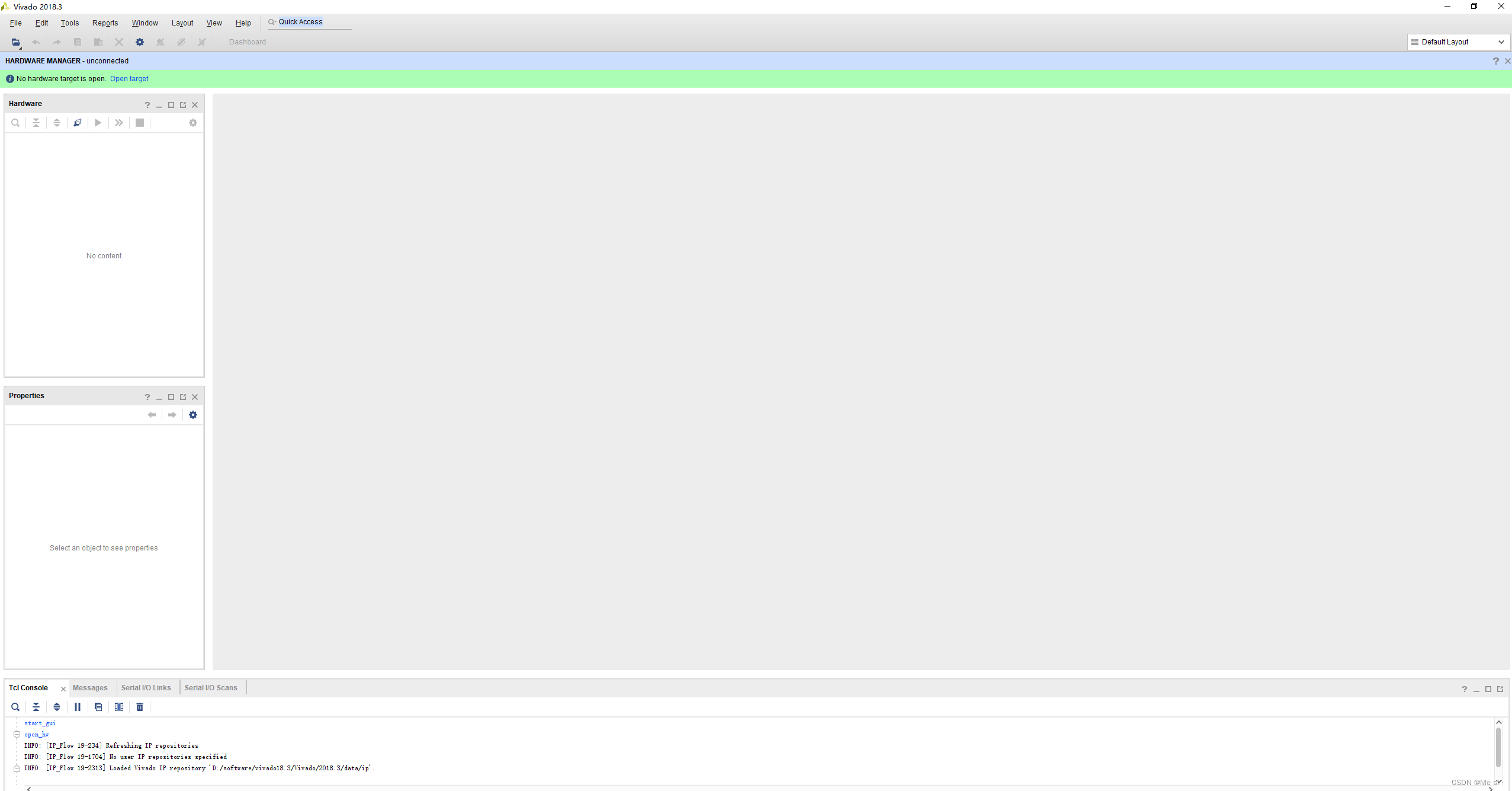

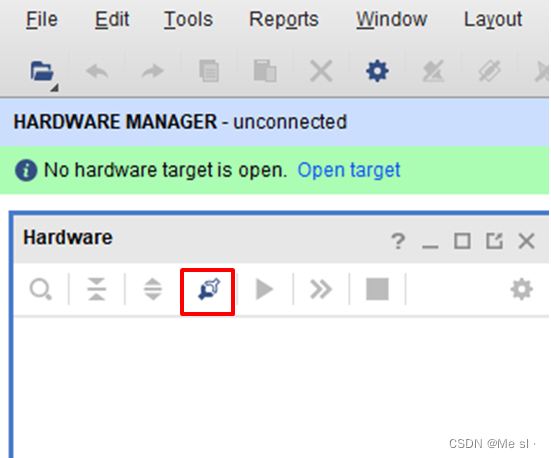

3、点击Open Hardware Manager,界面如下所示:

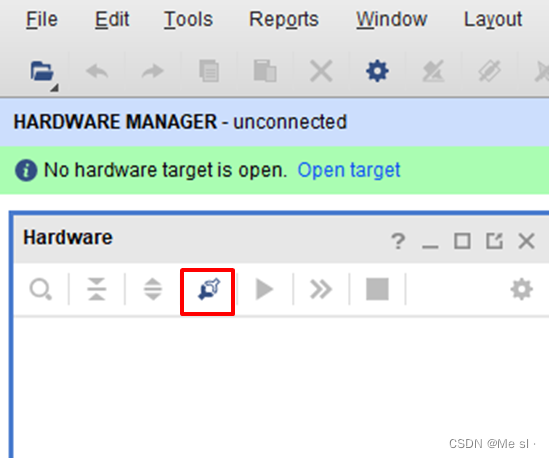

4、点击如下标识,连接板卡。

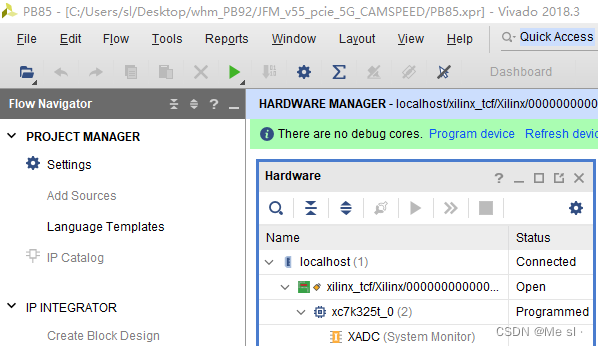

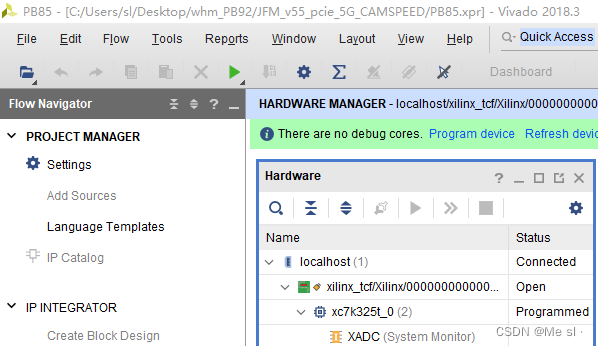

5、软件自动识别芯片型号,如下所示:

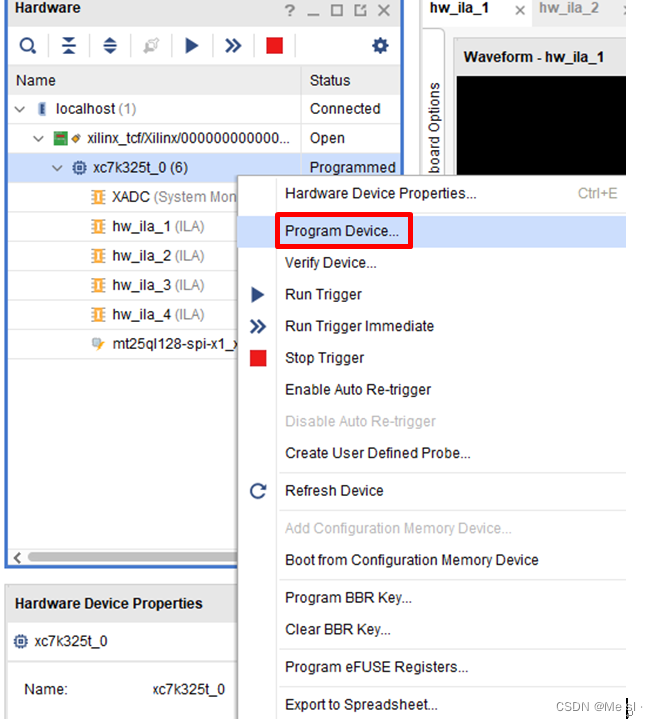

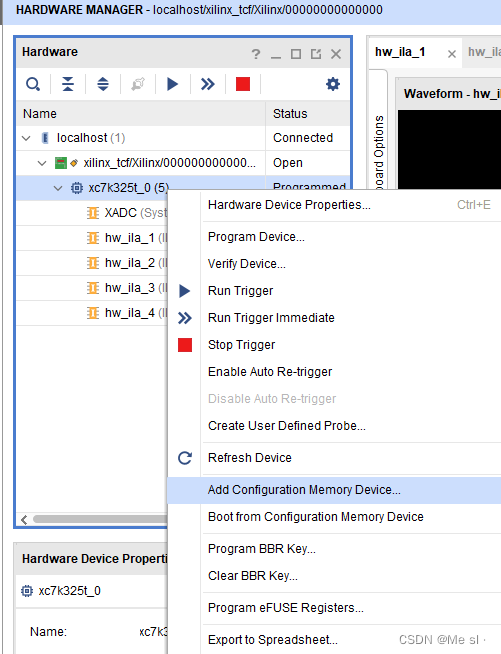

6、右击芯片型号,选择Program Device...,具体流程如下图所示:

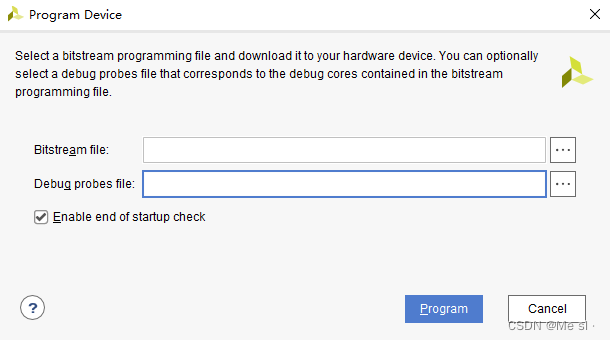

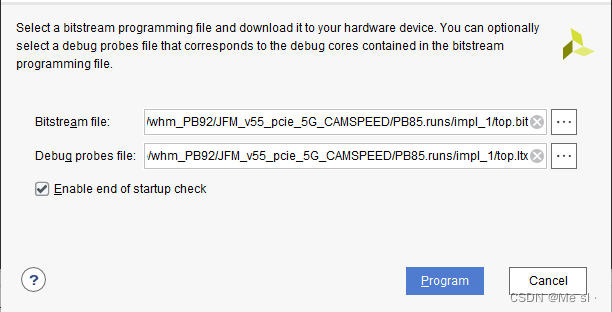

7、在Bitstream file:选择要固化的bit文件,如果有debug probes file文件,软件会主动关联(前提是bit文件和ltx文件在同一个目录下),如下所示:

8、文件选择完成后点击Program即可,等待软件下载完成,下载完成后就可以进行下一步调试。

2固化MCS文件

1、正确的将FPGA专用下载器与调试板卡或者产品连接,检查无误后打开电源上电。注:严禁带电操作。

2、打开VIVADO18.3软件,如下所示:

3、点击Open Hardware Manager,界面如下所示

4、点击如下标识,连接板卡。

5、软件自动识别芯片型号,如下所示:

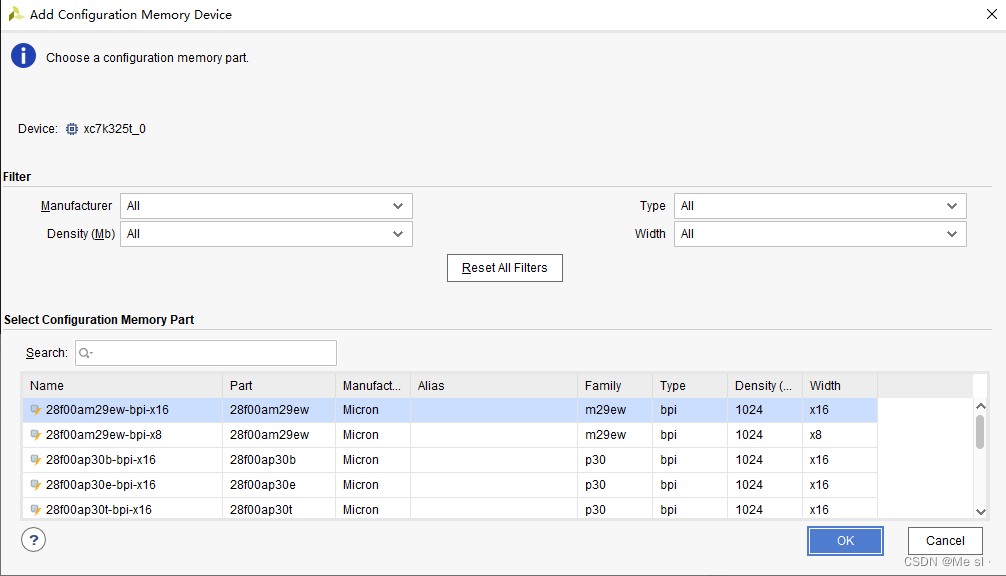

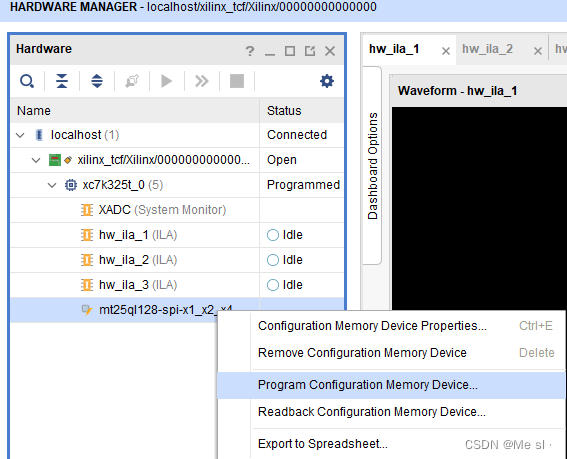

6、右击芯片型号,选择Add Configuration Memory Device...,添加FLASH型号,具体流程如下图所示:

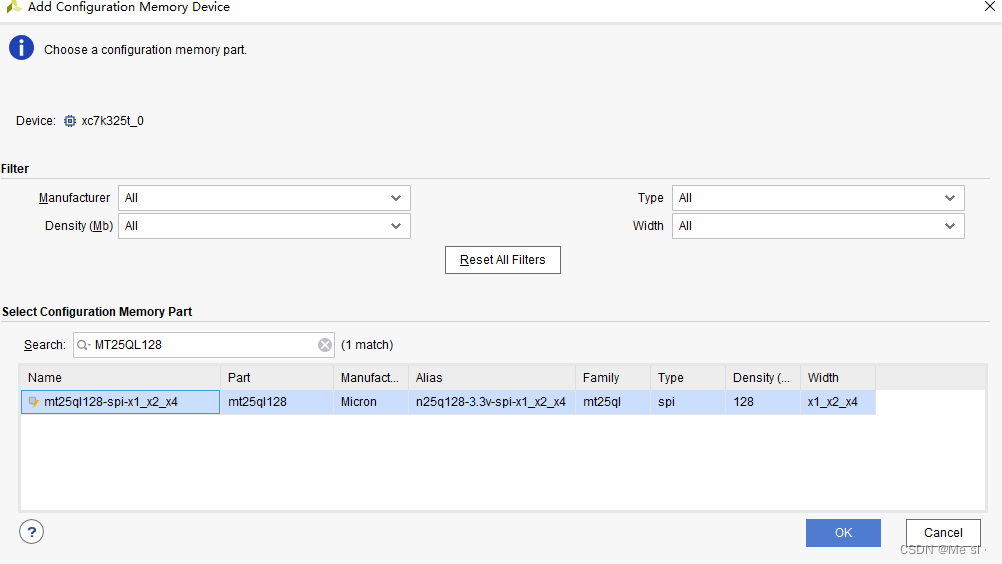

7、在search中输入具体型号,如MT25QL128,具体流程如下所示:

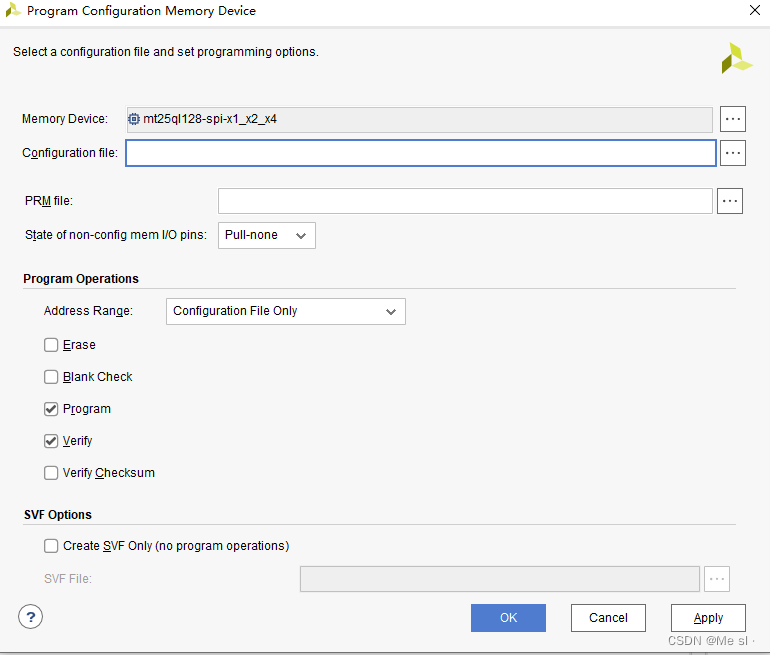

8、点击ok,出现如下所示流程:

9、固化的FLASH为xilinx官方指定型号和使用xilinx原厂FPGA芯片按如下操作。

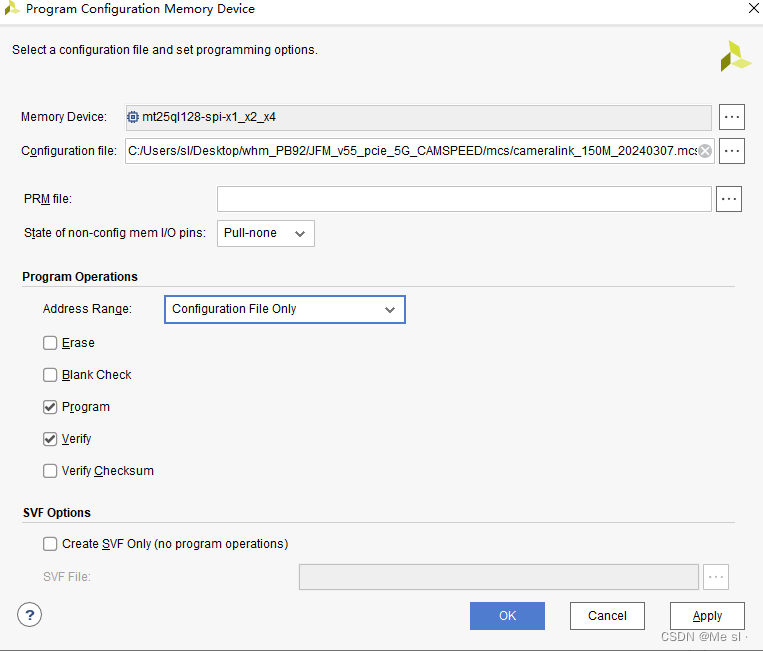

9.1、在configuration file 中添加要固化的mcs文件,如下所示:

9.2、添加完成后点击OK即可,等待烧录完成即可。

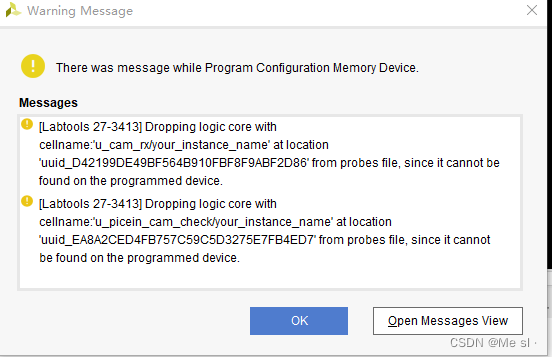

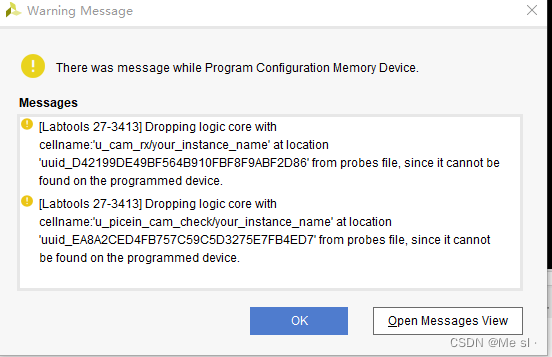

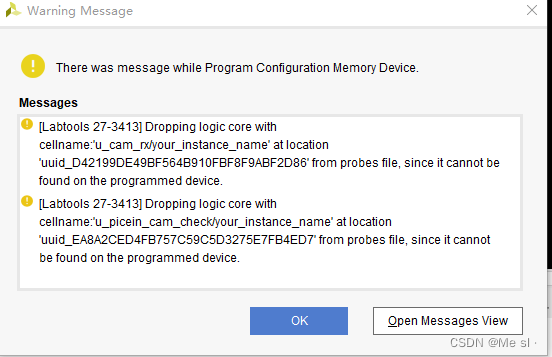

9.3、烧录完成如果程序中有ILA调试模块会弹出如下所示,不需要关心,点击OK即可。烧录完成后关掉电源,退出vivado烧录界面,重新上电即可。即程序烧写完成。

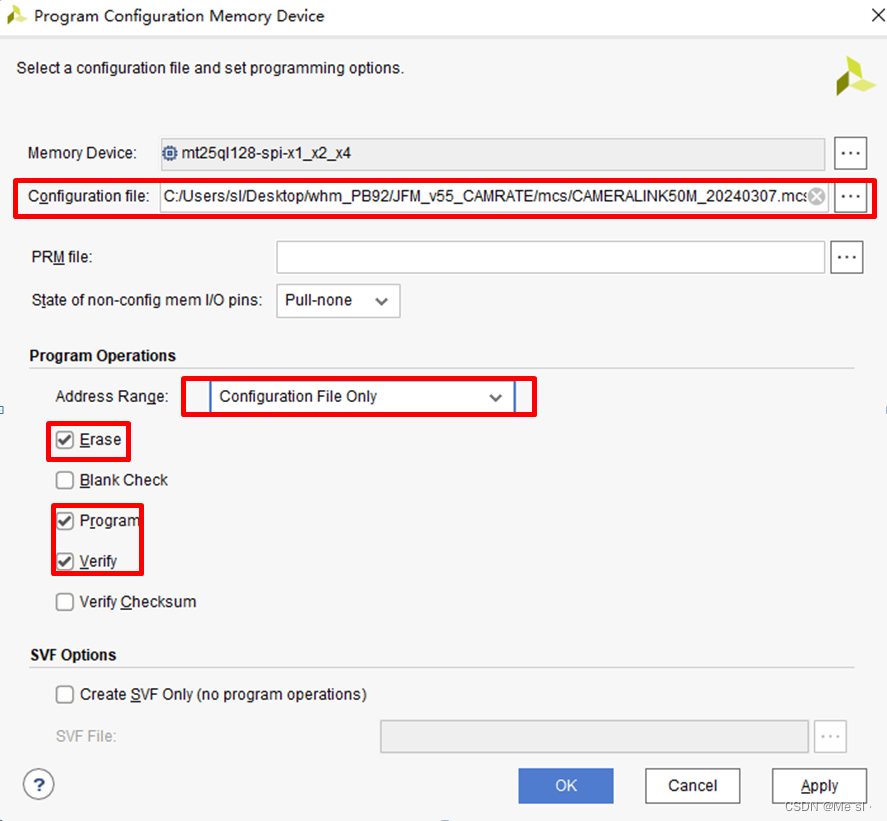

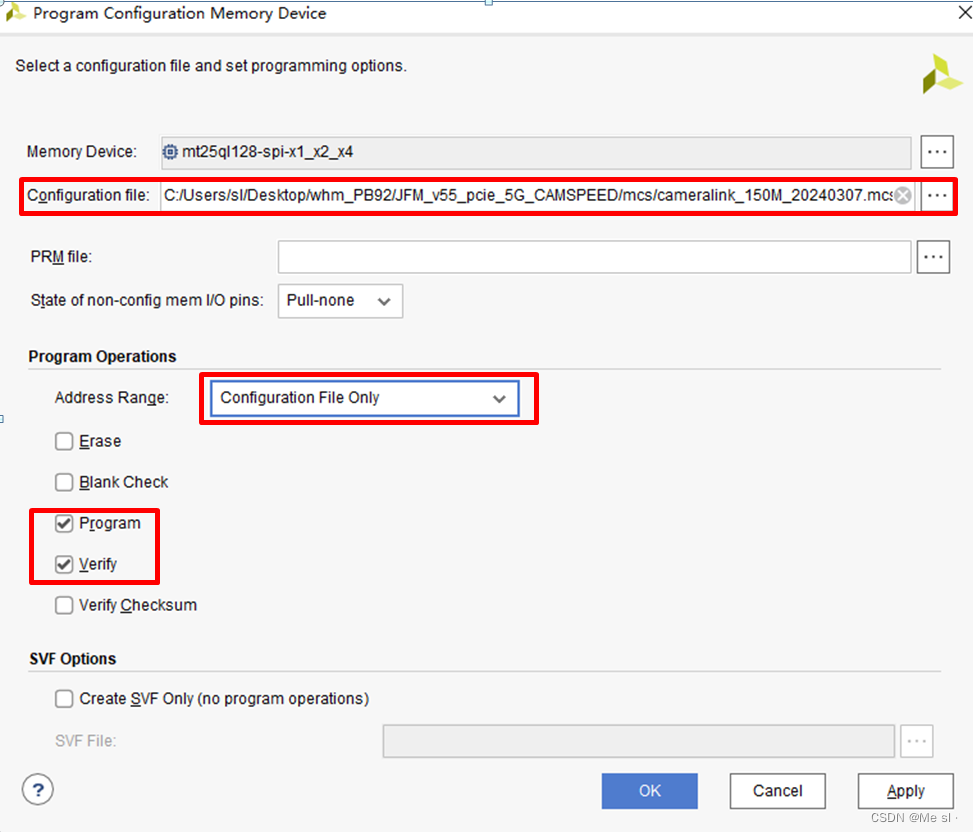

10、固化的FLASH为非xilinx官方指定型号和非xilinx原厂FPGA芯片按如下操作。

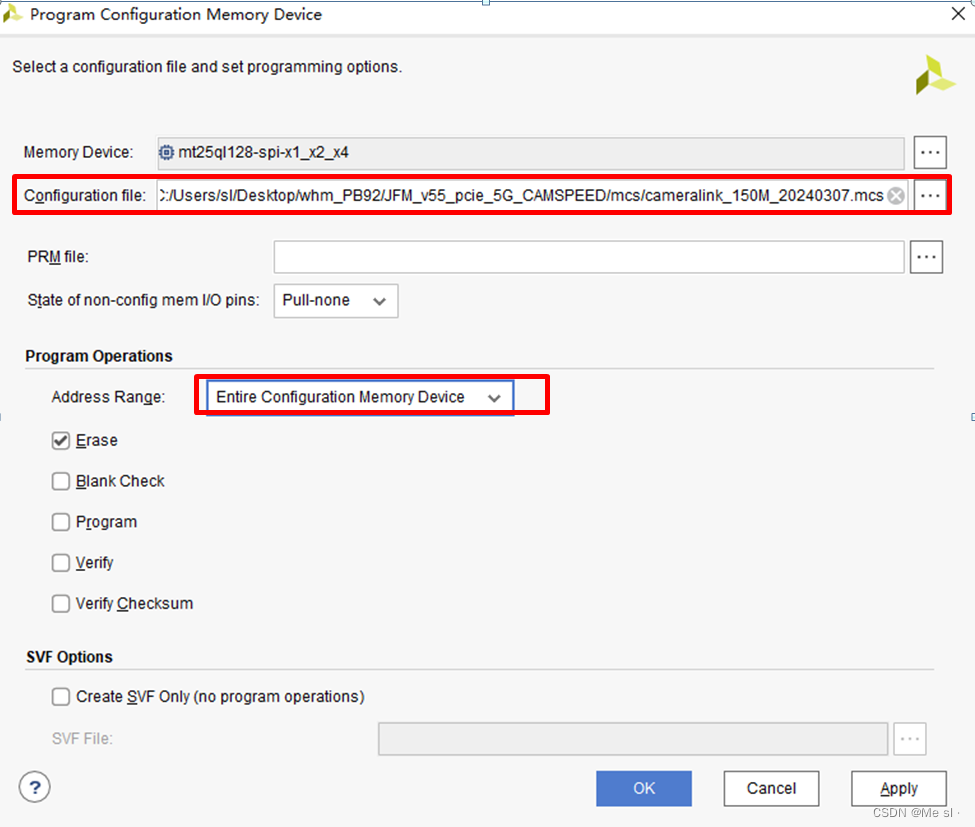

10.1、在configuration file 中添加要固化的mcs文件,文件添加完成后先执行擦除步骤,具体流程如下所示:

10.2、点击OK,等待擦除完成。

10.3、如果程序中有ILA调试模块会弹出如下所示,不需要关心,点击OK即可。

10.4、再右击flash型号,如下所示,选择Program Configuration Memory Device...,进入如下界面:

10.5、在configuration file 中添加要固化的mcs文件,文件添加完成后先执行擦除步骤,具体流程如下所示:

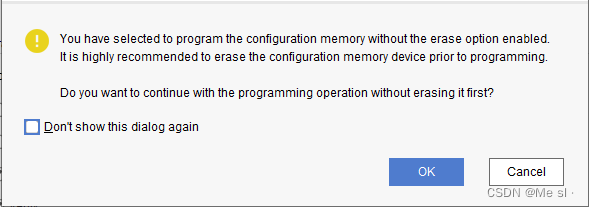

10.6、点击OK即可,出现如下提示点击OK即可。

10.7、如果软件很快的完成烧写,即未成功(一般固化需要两到三分钟),需要重新按照10.3-10.6步骤执行烧写程序。

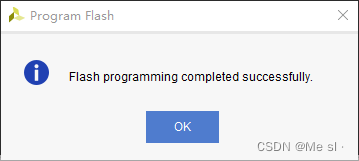

10.8、烧录完成如下所示:

10.9、烧录完成如果程序中有ILA调试模块会弹出如下所示,不需要关心,点击OK即可。烧录完成后关掉电源,退出vivado烧录界面,重新上电即可,即程序烧写完成。

2141

2141

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?