Vectors

module top_module (

input wire [2:0] vec,

output wire [2:0] outv,

output wire o2,

output wire o1,

output wire o0 ); // Module body starts after module declaration

assign outv=vec;

assign o2=vec[2];

assign o1=vec[1];

assign o0=vec[0];

endmoduleVectors in more detail

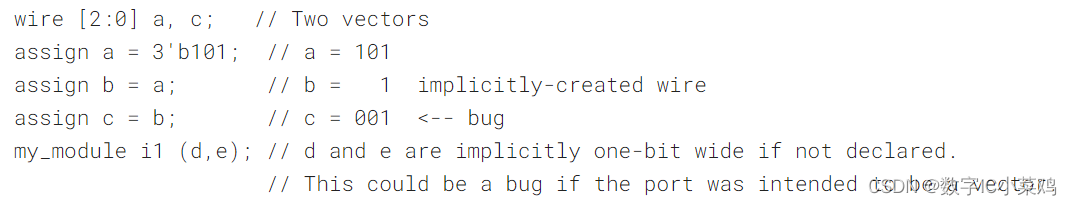

这里面主要介绍了我觉得可能稍微难懂的就是 隐式线网 的部分,如图所示,b是未生名的变量却直接使用这种就要隐式线网,默认为一位,最好不要这么使用,如果把b赋给向量则会报错。

其次,还有一些关于数组的知识,直接拿例子来说,如 reg [7:0] mem [0:255]代表了宽度为8,深度为256的数组,相当于256个寄存器,每个寄存器的长度为8位。reg [7:0] mem [0:255][0:255]则代表一个2维数组,行和列长度为256,就像长宽为256的矩阵一样,每一位数据的宽度为8。

此题答案:

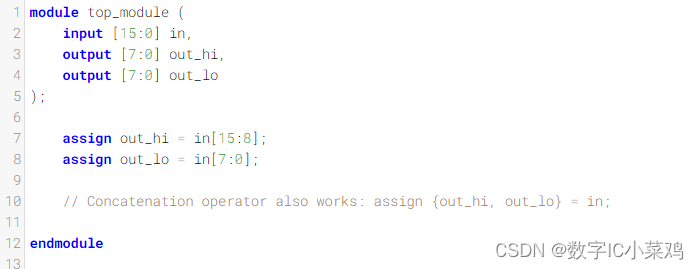

vector part select(矢量部分选择)

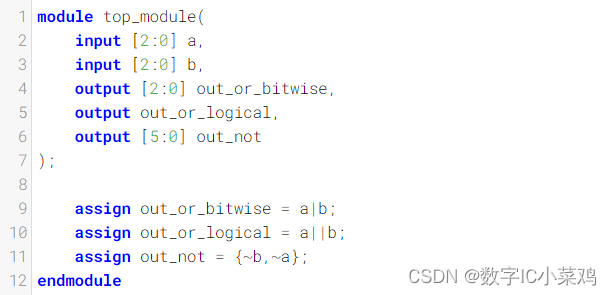

Bitwise operators(位运算符)

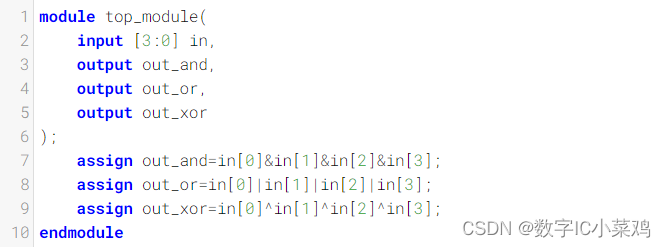

Four_input gates(四输入门)

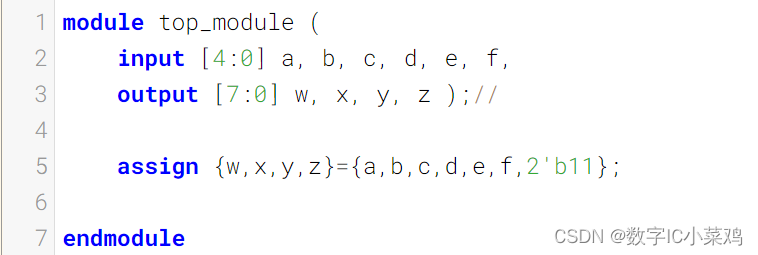

Vectors concatenation operator(向量连接运算符)

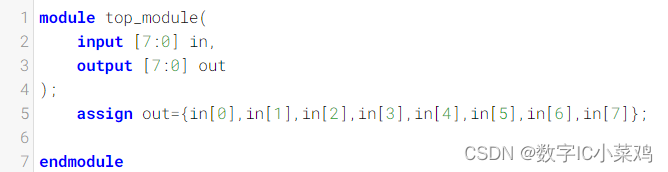

Vectors reversal 1(矢量反转)

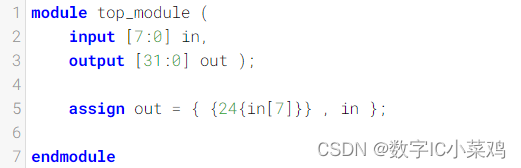

Replication operator(复制运算符)

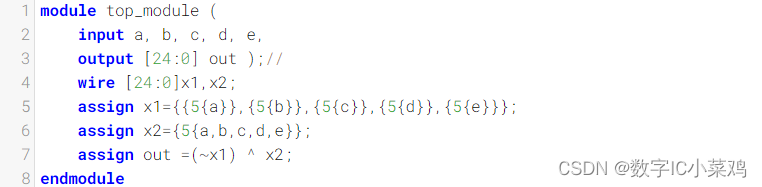

more replication(更多复制)

拜拜,下期见。

114

114

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?